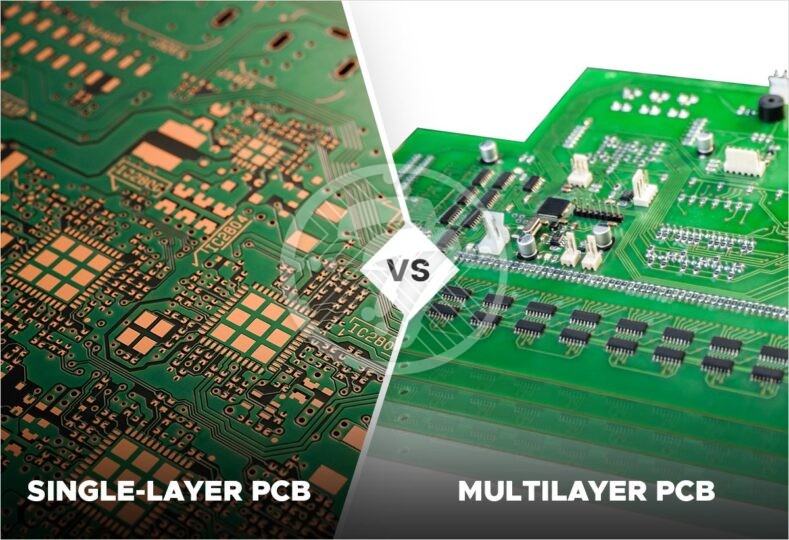

Multi-layer PCBs are generally defined as high multilayer PCBs with 10 – 20 layers or more, which are more difficult to process than traditional multilayer PCBs and their quality and reliability requirements are high, mainly used in communication equipment, high-end servers, medical electronics, aviation, industrial control, military and other fields. In recent years, the market demand for high-rise boards for applications such as communications, base stations, aviation, and military remains strong, and with the rapid development of China’s telecom equipment market, the prospects for the high-rise board market are promising.

Currently, the PCB manufacturers in China that can mass produce high level PCBs are mainly from foreign companies or a few domestic companies. The production of high level PCBs requires not only high technology and equipment investment, but also the accumulated experience of technicians and production personnel, as well as the introduction of high level PCB customer certification procedures are strict and cumbersome, so high level PCBs have a high threshold of entry into the enterprise and a long period of time to achieve industrial production.

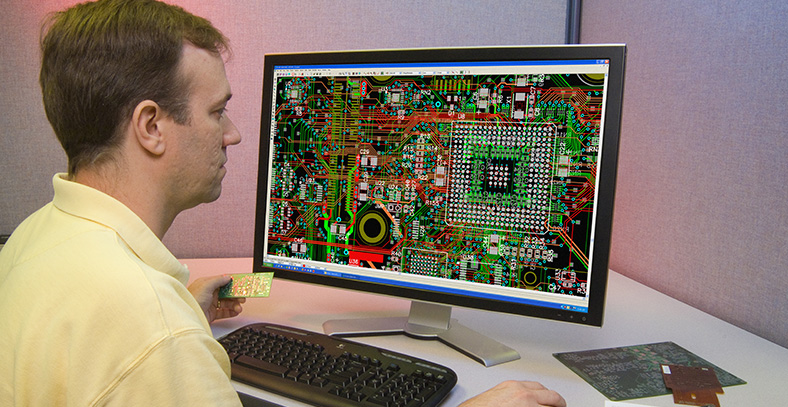

The average number of PCB layers has become an important technical indicator to measure the technology level and product structure of PCB companies. This article briefly describes the main processing difficulties encountered in the production of high level PCBs, and introduces the key control points of the key production processes of high level PCBs for your reference.

I. Major production difficulties

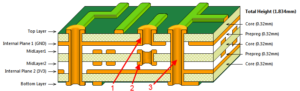

Compared to the features of conventional PCB products, high level PCBs feature thicker boards, more layers, denser lines and vias, larger cell sizes, thinner dielectric layers, and more stringent requirements for inner space, inter-layer alignment, impedance control, and reliability.

1 Difficulty with interlayer alignment

Because of the high level board layers, the customer design side of the PCB layers alignment requirements are becoming more and more stringent, usually inter-layer alignment tolerance control ± 75μm, taking into account the high level board unit size design larger, graphics transfer workshop environment temperature and humidity, and different core board layer up and down inconsistency brought about by the misalignment of the stack, inter-layer positioning method and other factors, making the high level board inter-layer alignment control more difficult.

2 Difficulties in creating inner lines

High layer boards use special materials such as high TG, high speed, high frequency, thick copper, thin dielectric layer, etc., which put high demands on the inner layer line fabrication and graphic size control, such as the integrity of impedance signal transmission, increasing the difficulty of inner layer line fabrication. Line width line spacing is small, open short circuit increases, micro-short increases, low pass rate; fine line signal layer is more, the chances of inner layer AOI leakage increased; inner layer core board thickness is thin, easy to crease leading to poor exposure, etching over the machine is easy to roll the board; most of the high level board for the system board, the unit size is larger, the cost of scrapping in the finished product is relatively high.

3 Press fit production difficulties

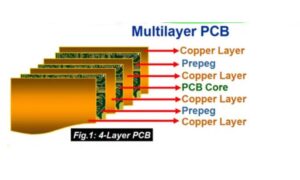

Multiple inner core sheets and semi-cured sheets are stacked, and defects such as slippage, delamination, resin voids and air bubble residue are easily generated during press-fit production. When designing the laminated structure, the heat resistance, voltage resistance, glue filling amount and media thickness of the material need to be fully considered, and a reasonable press-fit program for the upper layers needs to be set. The number of layers, the control of the amount of rise and shrinkage and the amount of size coefficient compensation can not maintain consistency; thin insulation layer between the layers, easy to lead to inter-layer reliability test failure problems. Figure 1 is a defective diagram of the burst board delamination after the thermal stress test.

4 Difficulties in drill hole fabrication

The use of special plates with high TG, high speed, high frequency, and thick copper increases the difficulty of drilling roughness, drilling burrs, and deburring. More layers, cumulative total copper thickness and plate thickness, drilling prone to tool breakage; more dense BGAs, CAF failure problems due to narrow hole wall spacing; prone to slant drilling problems due to plate thickness.

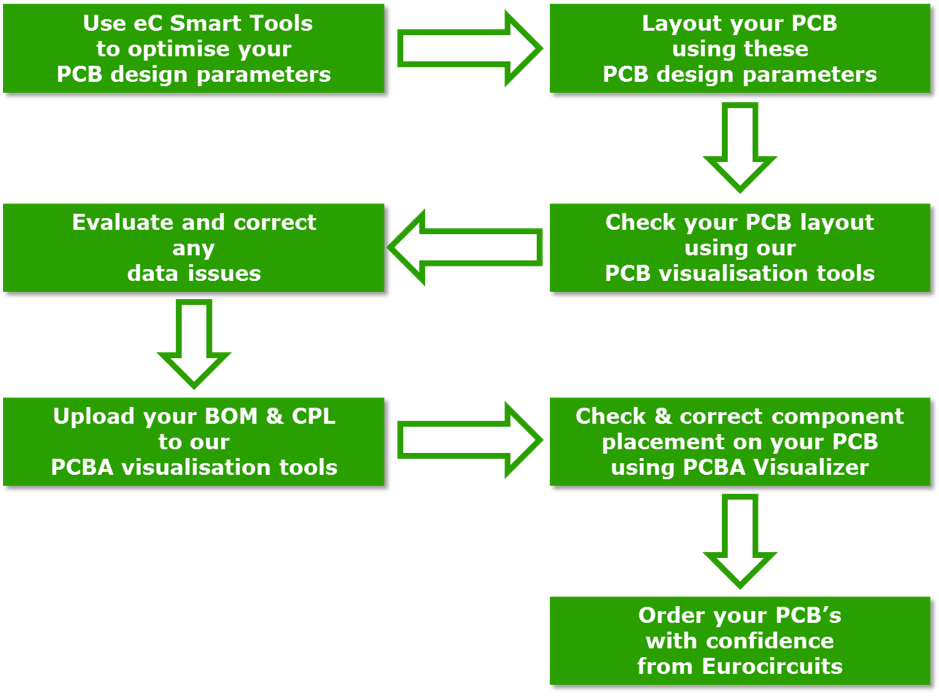

II. Critical production process control

1 Material selection

With the development of electronic components in the direction of high performance and multi-function, while bringing high frequency and high speed development of signal transmission, therefore, electronic circuit materials are required to have relatively low dielectric constant and dielectric loss, as well as low CTE, low water absorption and better high performance copper-clad materials to meet the processing and reliability requirements of high level boards. Commonly used sheet suppliers are mainly A series, B series, C series, D series, the main characteristics of these four inner substrate comparison, see Table 1. for high level thick copper circuit board selection of high resin content of the semi-curing sheet, layer between the flow of semi-curing sheet glue enough to fill the inner layer graphics, insulation media layer is too thick easy to appear in the finished board super-thick, and vice versa insulation media layer is thin, it is easy to cause media delamination, high voltage test failure The quality of the insulating dielectric material selection is therefore extremely important.

2 Press-fit laminated structure design

The main factors considered in the design of the laminated structure are the heat resistance of the material, the voltage resistance, the amount of adhesive filling and the thickness of the dielectric layer, etc. The following main principles should be followed.

(1) Semi-cured sheets must be consistent with the core board manufacturer. To ensure PCB reliability, all layers of semi-cured sheets avoid using a single 1080 or 106 semi-cured sheet (except for special customer requirements), and when the customer has no media thickness requirements, the media thickness between each layer must be guaranteed to be ≥0.09mm per IPC-A-600G.

(2) When customers require high TG sheets, both core and semi-cured sheets are made of the corresponding high TG material.

(3) Inner substrate 3OZ or more, choose high resin content of the semi-curing sheet, such as 1080R/C65%, 1080HR/C 68%, 106R/C 73%, 106HR/C76%; but try to avoid all use of 106 high adhesive semi-curing sheet structure design, to prevent multiple 106 semi-curing sheet stacked, because the glass fiber yarn is too fine, glass fiber yarn in Large substrate area collapse and affect the dimensional stability and burst board delamination.

(4) If the customer has no special requirements, the thickness tolerance of the interlayer media layer is generally controlled by +/-10%. For impedance boards, the media thickness tolerance is controlled by IPC-4101 C/M level tolerance, and if the impedance influence factor is related to the thickness of the substrate, the board tolerance must also be controlled by IPC-4101 C/M level tolerance.

3 Interlayer Alignment Control

The accuracy of inner core board size compensation and production size control requires precise compensation of the graphic size of each layer of the high level board through the data collected in production over a certain period of time with the experience of historical data to ensure the consistency of the rise and shrinkage of each layer of the core board. Select high precision and reliable interlayer positioning methods before press-fit, such as four-slot positioning (Pin LAM), heat fusion and rivet combination. Setting proper laminating process procedures and routine maintenance of the press is the key to ensure laminating quality, control laminating flow and cooling effect, and reduce interlayer misalignment problems. The control of interlayer alignment requires a combination of factors such as inner layer compensation values, press-fit positioning methods, press-fit process parameters, and material properties.

4 Inner layer line process

As the resolution of conventional exposure machines is around 50μm, for high level board production fabrication, laser direct imaging machines (LDI) can be introduced to improve the graphics resolution to around 20μm. The alignment accuracy of traditional exposure machines is ±25μm and the interlayer alignment accuracy is greater than 50μm. By using high precision alignment exposure machines, the graphic alignment accuracy can be increased to about 15μm and the interlayer alignment accuracy is controlled to within 30μm, reducing the alignment deviation of traditional equipment and improving the interlayer alignment accuracy of high level boards.

To improve line etch capability, proper compensation for line width and pads (or solder rings) in addition to more detailed design considerations for special patterns such as return lines, independent lines, etc. compensation is required for engineering design. Confirm the inner layer line width, line spacing, isolation ring size, independent line, hole to line distance design compensation is reasonable, otherwise change the engineering design. There are impedance, inductive design requirements pay attention to the independent line, impedance line design compensation is sufficient, etching control parameters, the first part to confirm qualified before mass production. In order to reduce the etching side corrosion, the etching solution needs to be controlled within the best range for each group of the composition of the solution. Traditional etching line equipment etching capacity is not enough, you can make technical changes to the equipment or import high precision etching line equipment to improve etching uniformity, reduce etching burrs, etching not net and other problems.

5 Press-fit process

Currently, the main methods of positioning between layers before lamination include: four-slot positioning (Pin LAM), heat fusion, riveting, and a combination of heat fusion and riveting, with different positioning methods used for different product structures. For the high level board, we adopt the four-slot positioning method (Pin LAM), or use the fusion + riveting method to produce, OPE punching machine punching out the positioning holes, punching accuracy control at ±25μm. The presses are equipped with high performance presses to meet the layer alignment accuracy and reliability of the high level boards.

According to the high level board stack structure and the materials used, study the appropriate pressing procedure, set the best heating rate and curve, on the conventional multi-layer circuit board pressing procedure, appropriately reduce the pressing board material heating rate, extend the high temperature curing time, so that the resin fully flows and cures, while avoiding the problems of slipping board and inter-layer misalignment during pressing. Material TG value is not the same board, can not be the same furnace row board; ordinary parameters of the board can not be mixed with the special parameters of the board press; to ensure that the rise and shrinkage coefficient is given reasonable, the performance of different plates and semi-curing sheet is not the same, the need to use the corresponding plate semi-curing sheet parameters pressed together, never used special materials need to verify the process parameters.

6 Drilling process

Severe wear on the drill bit and easy breakage of the drill cutter due to the super-thickness of the plate and copper layer caused by the stacking of the layers, for the appropriate downward adjustment of the number of holes, drop speed and RPM. Accurately measure the rise and shrinkage of the plate to provide accurate coefficients; layer ≥ 14 layers, hole diameter ≤ 0.2mm or hole to line distance ≤ 0.175mm, the use of hole accuracy ≤ 0.025mm drilling machine production; diameter φ4.0mm or more hole diameter using step drilling, thickness to diameter ratio of 12:1 using step drilling, positive and negative drilling method production; control drilling phi and hole coarse, high level plate as far as possible using a new drill cutter or grinding 1 drilling tool drilling, hole thickness control within 25um. In order to improve the drilling burr problem of high level thick copper plate, the batch verification, the use of high-density pad, the number of stacked plate is one, the drill bit grinding times control within 3 times, can effectively improve the drilling burr, as shown in the figure below.

For high frequency, high speed, high level boards for massive data transfer, back drilling technique is an effective way to improve signal integrity. Back drilling mainly controls residual stub length, hole alignment between two drill holes, and copper wire in the hole. Not all driller equipment has back-drilling capability and it is necessary to upgrade the driller equipment with technology (with back-drilling capability) or purchase a driller with back-drilling capability. Back drilling technology from industry related literature and mature mass production applications mainly include: traditional depth control back drilling method, inner layer for signal feedback layer back drilling, and depth calculation back drilling according to the ratio of board thickness, which is not repeatedly described here.

III. Reliability testing

High-rise boards are typically system boards that are thicker, heavier, and have larger cell sizes than conventional multilayer boards, with correspondingly larger heat capacities, requiring more heat and experiencing longer soldering heat times when soldering. It takes 50 seconds to 90 seconds at 217°C (the melting point of tin-silver-copper solder), while the cooling rate of the high level board is relatively slow, thus extending the time for over reflow testing and combining with IPC-6012C, IPC-TM-650 standards and industry requirements for major reliability tests on high level boards, as described in Table 2.