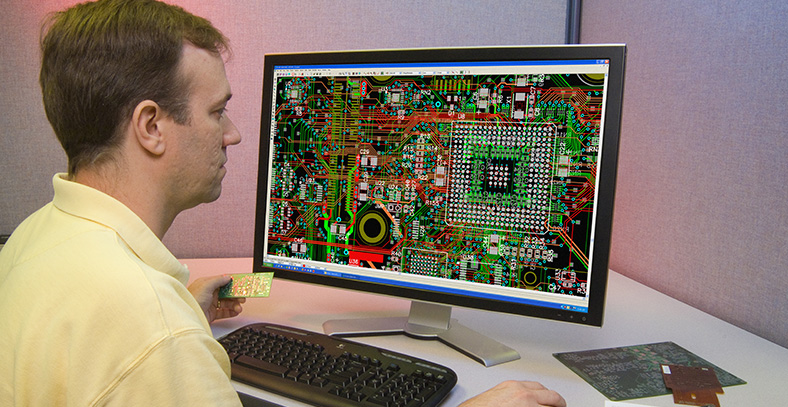

Board design is a critical and time-consuming task, and any issues that arise require engineers to go through the entire design, network by network, component by component. It can be said that circuit board design requires a level of care that is no less than that required for chip design.

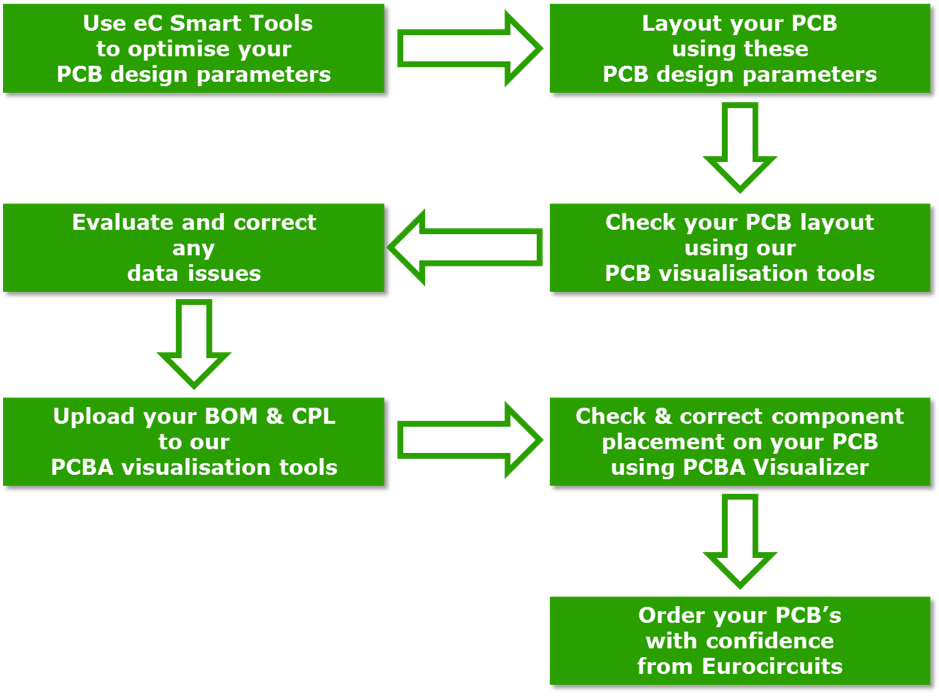

A typical board design flow consists of the following steps:

The first three steps took the most time, because schematic checking is a manual process. Imagine a SoC board with 1000 or more wires. Manually checking each wire is a long and tedious task. In fact, it is almost impossible to check every single wire, which can lead to problems with the final board, such as incorrect connections, suspended nodes, etc. The following types of problems are typically faced during the schematic capture phase:

●Underline errors: e.g. APLLVDD and APLL_VDD

●Case issues: e.g. VDDE and vdde

●Spelling errors

●Signal shorting problem

●…… and many more

To avoid these errors, there should be a way to be able to check the entire schematic in a matter of seconds. This can be done using schematic simulation, which is rarely seen in the current board design flow. With schematic emulation the final output can be observed at the requested node, so it automatically checks all the connectivity issues.

This is explained below with an example project. Consider a typical block diagram of a circuit board:

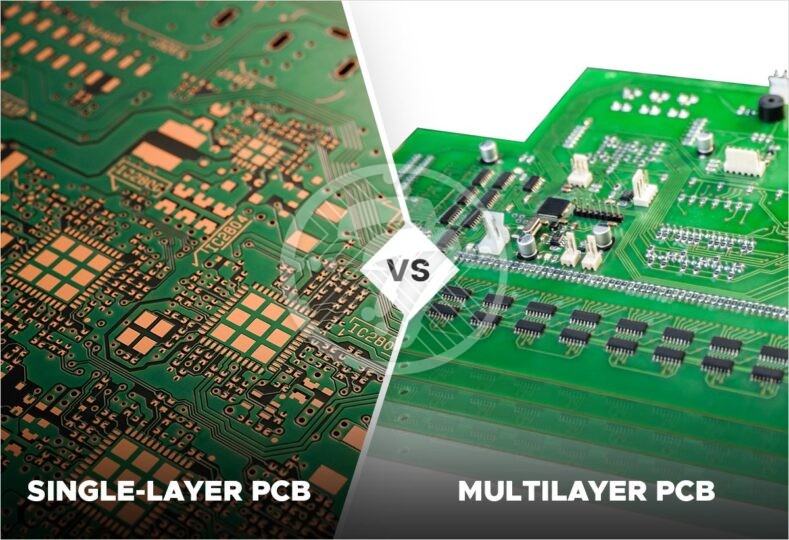

In complex board designs, the number of connections can run into the thousands, and a very small number of changes are likely to waste a lot of time checking.

The schematic simulation not only saves design time, but also improves board quality and makes the overall process more efficient.

A typical device under test (DUT) has some of the following signals: <!

The device under test will have a wide variety of signals after some pre-tuning and has various modules, such as regulators, op-amps, etc., for signal tuning. Consider an example of a supply signal obtained through a voltage regulator:

To verify the connection relationships and perform an overall check, schematic simulation is used. Schematic simulation consists of schematic creation, testbench creation, and simulation.

During the testbed creation process, there will be excitation signals given to the necessary inputs, and then the output results will be observed at the signal points of interest.

The above process can be achieved by connecting a probe to the node to be observed. Node voltages and waveforms can indicate whether the schematic has errors. All signal connections are automatically checked.

Let’s look at a partial view of the graph above, where the probed nodes and voltages are clearly visible:

So with the help of simulation, we can directly observe the results and confirm if the board schematic is correct. In addition, careful adjustment of the excitation signal or component values also enables investigation of design changes. So schematic simulation saves a lot of time for board designers and checkers, and increases the chance of a correct design.