לאחר השלמת הגדרת המערכת, חלוקה פונקציונלית, סימולציה ומיקום רכיבים (Placement), עבודת תכנון ה-PCB במהירות גבוהה נכנסת לשלב הקריטי ביותר שלה.

בשלב הזה המטרה כבר אינה רק להוכיח שהסכימה (Schematic) עובדת. המטרה היא לוודא שהתכנון הפיזי מסוגל להתמודד עם מהירויות חזית אמיתיות (Edge Rates), צפיפות ניתוב, מגבלות ייצור, וחזרתיות בייצור סדרתי. במילים אחרות, כאן זרימת תכנון ה-PCB עוברת מכוונת תכנון לתוצאה שניתן לייצר באופן עקבי.

מדריך זה מכסה את החצי השני של PCB design flow עבור תכנון PCB במהירות גבוהה, ומתמקד ב-high-speed PCB routing, PCB signal integrity, PCB timing analysis, PCB routing constraints, PCB routability analysis, ובהכנת PCB manufacturing files מלאים לשחרור לייצור.

אילוצי ניתוב PCB: שלמות האות מתחילה לפני ניתוב מהיר

בתכנונים איטיים (Low-Speed), לרוב מספיק חיבור לוגי נכון. ב-תכנון PCB במהירות גבוהה זה לא מספיק.

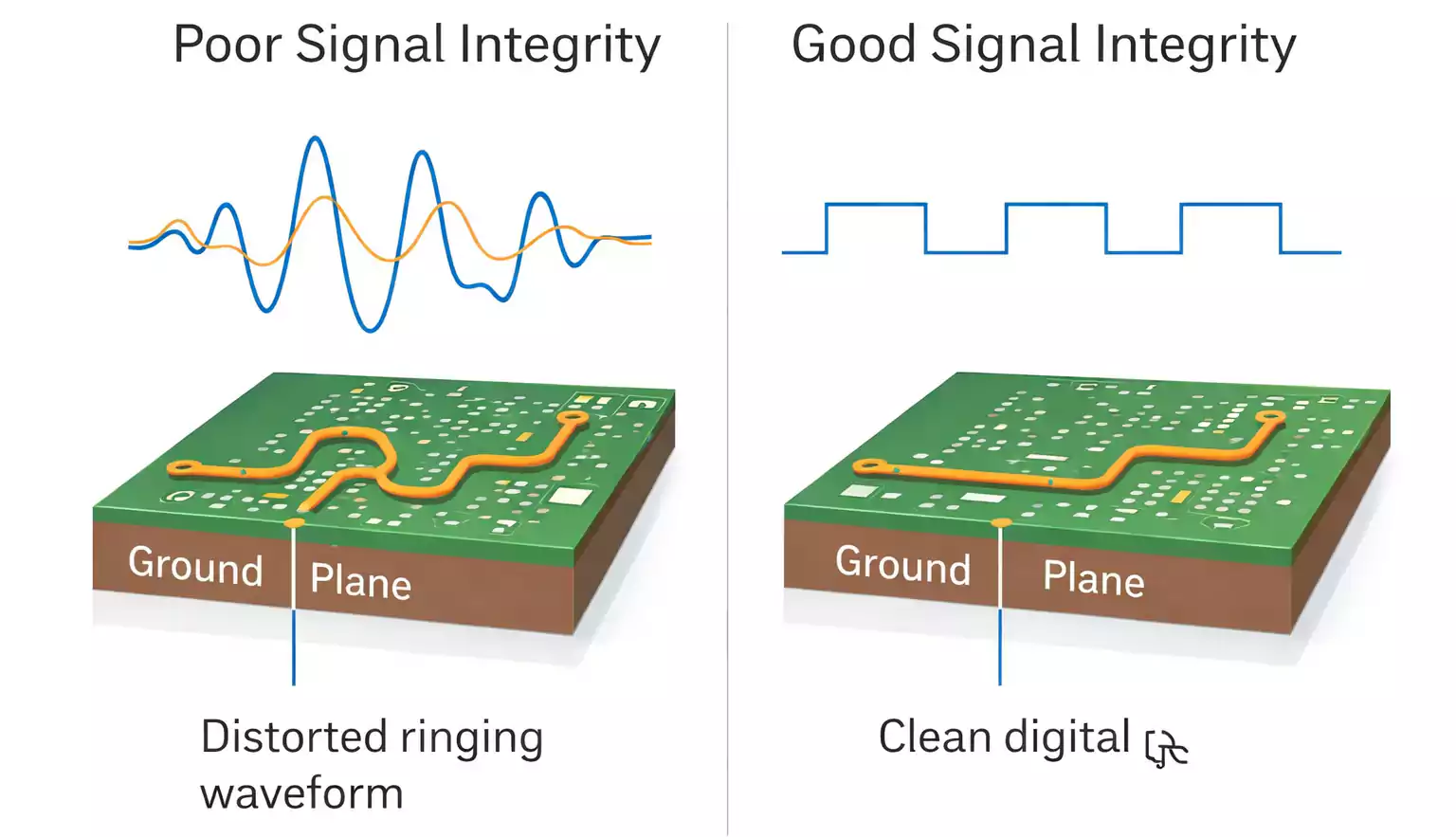

כאשר מהירויות החזית עולות ועיכובי החיבורים (Interconnect Delays) נעשים משמעותיים, המסלולים (Traces) מתנהגים כקווי תמסורת. בשלב הזה הגיאומטריה של ה-Layout משפיעה ישירות על שלמות האות (PCB signal integrity). תופעות כשל נפוצות כוללות:

- החזרים (Reflections)

- זליגת אות/השראה הדדית (Crosstalk)

- רינגינג/צלצול (Ringing)

- Overshoot ו-Undershoot

- מיתוג שגוי / שגיאות סף (False switching / threshold errors)

לכן יש להגדיר ולסקור אילוצי ניתוב מייד לאחר ה-Placement, לפני שמתחילים ניתוב מהיר מפורט.

אילוצים מרכזיים כוללים בדרך כלל:

- טופולוגיית Driver-to-Load

- אסטרטגיית טרמינציה (Termination) ומיקומה

- סדר הצמתים לאורך הרשת (Node ordering)

- בקרת אורכים ומגבלות Skew

- עקביות אימפדנס (Single-Ended ו-Differential)

המטרה היא התנהגות תמסורת צפויה לפני שמקבעים את הנחושת. ב-Backplanes מהירים ובפלטפורמות מחשוב, אילוצים אלה חיוניים — החלטות פיזיות קטנות עלולות להוביל לאי-יציבות משמעותית.

ניתוח תזמון ומידול קווי תמסורת: לחזות לפני שמנתבים

כאשר ה-Placement יציב, המיקומים הפיזיים ומסדרונות הניתוב המשוערים ידועים. עוד לפני ניתוב מפורט, אפשר לבצע PCB timing analysis מוקדם ומידול קווי תמסורת על בסיס:

- אורכי מסלולים משוערים וזמני מעבר (Flight times)

- הנחות טופולוגיה (Point-to-Point לעומת Multi-Drop)

- אינדיקציות סיכון מוקדמות להחזרים ולעיוות חזית

מכיוון שקואורדינטות הצמתים וסדר החיבור מוגדרים, ניתן לסמלץ התנהגות צפויה ולזהות בעיות מרווח תזמון כאשר עדיין קל לבצע שינויים.

הערך כאן פשוט: תיקון בעיות PCB signal integrity אחרי הניתוב יקר; זיהוי שלהן לפני high-speed PCB routing יעיל ומבוקר. עבור צוותי תכנון PCB מהיר מנוסים, מידול מוקדם של תזמון וקישוריות הוא שלב סטנדרטי להפחתת סיכונים בתוך זרימת התכנון.

רעש בשלמות האות: רעש פנימי מול הפרעות חיצוניות

לא כל רעש נובע מאותה סיבה, וטיפול זהה בכל בעיות הרעש מוביל לפתרונות לא יעילים. גישה נקייה יותר ב-PCB signal integrity היא להפריד לשתי קטגוריות:

1) רעש פנימי של המערכת (Intrinsic)

כולל:

- רעש תרמי (Thermal noise)

- רעש מיתוג (Switching noise)

- רעש אות פנימי (Intrinsic signal noise)

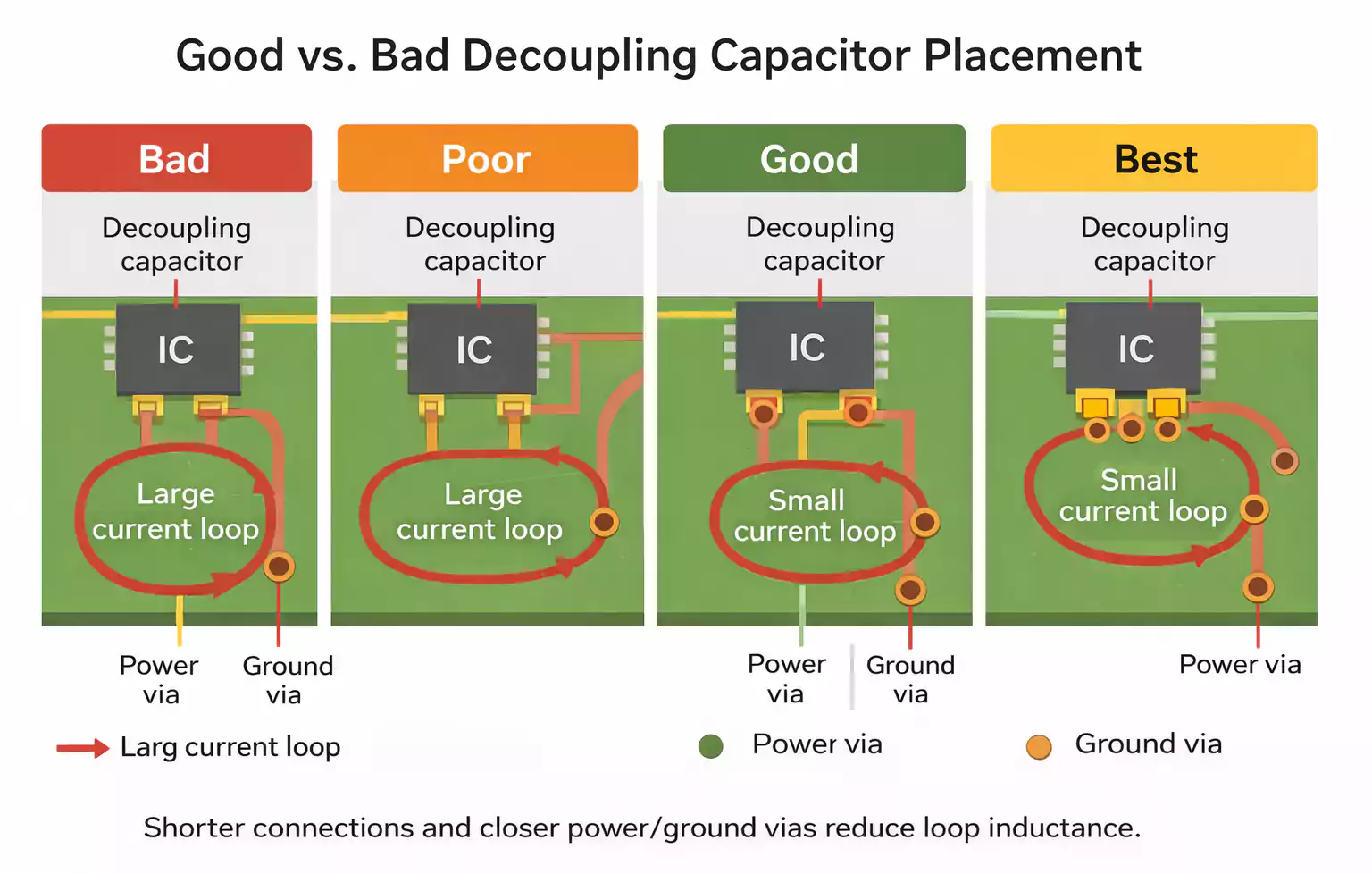

רעש פנימי הוא חלק מהתנהגות רגילה של המעגל. אי אפשר לבטל אותו לגמרי, אבל ניתן לנהל אותו על ידי שיפור יחס אות-רעש ושליטה ביישום הפיזי: מסלולי חזרה (Return paths), דה-קפלינג (Decoupling) וניהול מהירות חזית.

2) הפרעות חיצוניות (Coupled / Environmental)

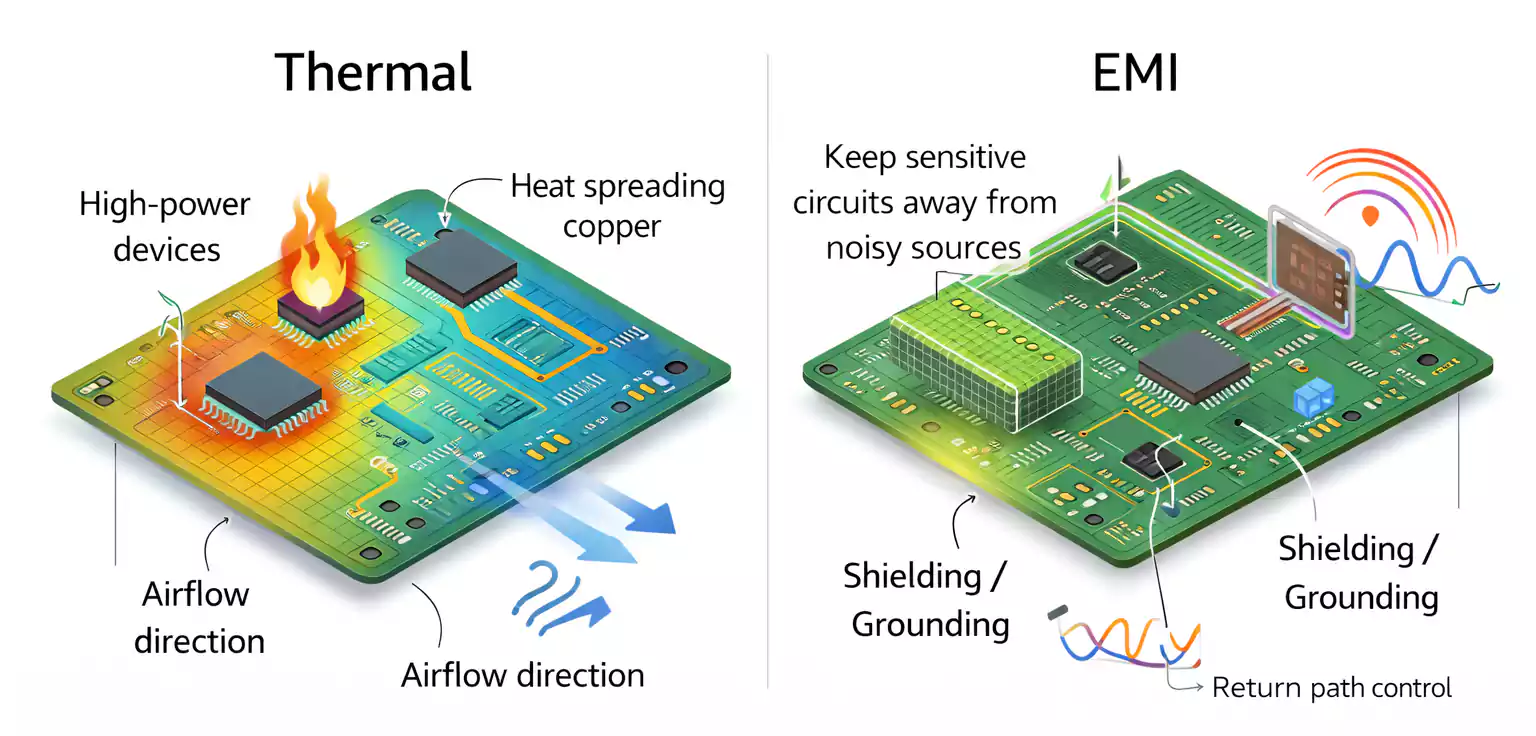

הפרעות אלה מגיעות מחוץ למעגל המיידי ועלולות להיות מזיקות במיוחד באזורים רגישים: אנלוגי, RF-adjacent, ומערכות Mixed-Signal.

אמצעי מיתון טיפוסיים:

- מיגון (Shielding)

- שיפור אסטרטגיית הארקה (Grounding)

- בידוד פיזי של בלוקים רגישים

- רשתות פילטר (Filter networks)

- תכנון ממשקים מבוקר (Controlled interface design)

הבנה האם הבעיה פנימית או חיצונית עוזרת לבחור את הפתרון הנכון ומקצרת זמן דיבוג.

אם התזמון או ה-SI נכשלים: לחזור ל-Placement ולטופולוגיה (לפני ניתוב)

אם המידול המוקדם מצביע על:

- עיכוב מוגזם

- מרווח תזמון נמוך

- החזרים משמעותיים

- עיוות חזית או Ringing

התגובה הנכונה אינה “ננתב ונראה”. ב-תכנון PCB במהירות גבוהה זה הזמן לשנות Placement וטופולוגיה.

פעולות תיקון נפוצות:

- קירוב רכיבים קריטיים

- קיצור מסלולי אות בעדיפות גבוהה

- שינוי טופולוגיה (Point-to-Point מול Multi-Drop)

- הוספה/הסרה/הזזה של טרמינציה

- התאמת Stackup כדי לתמוך באילוצים

במערכות דיגיטליות בסדרי גודל של GHz — במיוחד בלוחות גדולים פיזית — אורך ופריסת הטופולוגיה משפיעים ישירות על התזמון הגלובלי. איטרציה בשלב הזה מגדילה את סיכויי ה-First-Pass Success ומונעת Reroute מאוחר ויקר.

ניתוח Routability: לוודא שאפשר לנתב את הלוח כפי שהוא

תכנונים רבים נכשלים לא בגלל טעויות חשמליות אלא בגלל הערכת חסר של משאבי ניתוב. לכן PCB routability analysis צריך להתבצע לפני ניתוב מפורט.

בדיקות Routability צריכות לענות על:

- האם יש מספיק שכבות סיגנל?

- האם המרווחים ב-Placement ריאליים ל-Fanout הצפוי?

- היכן מוקדי הצפיפות (Congestion hot spots)?

- האם ערוצים קריטיים חסומים על ידי אילוצים מכניים או Keepout?

- האם ה-Floorplan תומך ב-Stackup ובאסטרטגיית ה-Via?

כלי EDA מודרניים מספקים מדדי צפיפות ובדיקות היתכנות ניתוב. אם ה-Routability חלשה, לרוב הפתרון הנכון הוא שינוי אסטרטגיית Placement/Layer — ולא “לכפות” ניתוב פגום.

השלב הזה חשוב במיוחד בלוחות רב-שכבתיים צפופים ובתכנוני Mixed-Signal, שבהם PCB routing constraints מצמצמים את שטח הניתוב הזמין.

High-Speed PCB Routing: לעבוד במסגרת האילוצים, לא נגדם

כאשר ה-Placement, PCB timing analysis ו-PCB routability analysis במצב טוב, מתחיל ניתוב מהיר מפורט.

הניתוב חייב לעמוד באילוצים שהוגדרו מראש, כולל:

- כללי רוחב ומרווח מסלולים

- התאמת אורכים ושליטת Skew

- דרישות אימפדנס

- צימוד וסימטריה של זוגות דיפרנציאליים

- רציפות מסלול החזרה (Return path continuity)

- מגבלות Crosstalk וסיווגי מרווח

בפועל, צוותים חזקים משתמשים בדרך כלל ב:

- ניתוב ידני לרשתות מהירות קריטיות

- ניתוב מבוקר למסלולי חלוקת הספק (Power distribution)

- ניתוב אוטומטי לאותות לא קריטיים

- ניקוי ואופטימיזציה לאחר ניתוב (Post-route)

“Playbook” לניתוב — מדיניות שכבות, חוקי Via, עדיפויות Net-class וקריטריוני סקירה — משפר עקביות ומפחית סבבי Review בצוותים מרובי מהנדסים.

אימות לאחר ניתוב: לסגור את הלולאה על SI, תזמון וקישוריות

סיום הניתוב לא אומר שהעבודה הסתיימה; עכשיו אורכים וגיאומטריות בפועל מחייבים אימות מחדש.

בדיקות Post-route כוללות בדרך כלל:

1) אימות מחדש של PCB signal integrity ו-PCB timing analysis

- אישור מרווחי תזמון לפי אורכים בפועל

- בדיקה חוזרת של החזרים ואיכות חזית

- הערכת סיכוני צימוד בין Aggressor/Victim nets

2) אימות Netlist / Connectivity

- לוודא שלא הוכנסו שינויים לא מכוונים בקישוריות

- לוודא שלא נוצרו Opens/Shorts בזמן עריכות

3) יכולת ייצור ועמידה בכללים (Manufacturability / Rule compliance)

- בדיקת עמידה ברוחב/מרווח

- אימות מרווחי מסכת הלחמה (Solder mask clearances)

- לוודא ש-Pads לא נחשפו או כוסו בטעות

- לוודא שמבני אימפדנס ניתנים לייצור

כאן נמנעות רבות מהבעיות של “עבד ב-CAD” מלהפוך ל“נכשל בבנייה”.

PCB Manufacturing Files: ממסד נתוני התכנון לחבילת שחרור מוכנה לייצור

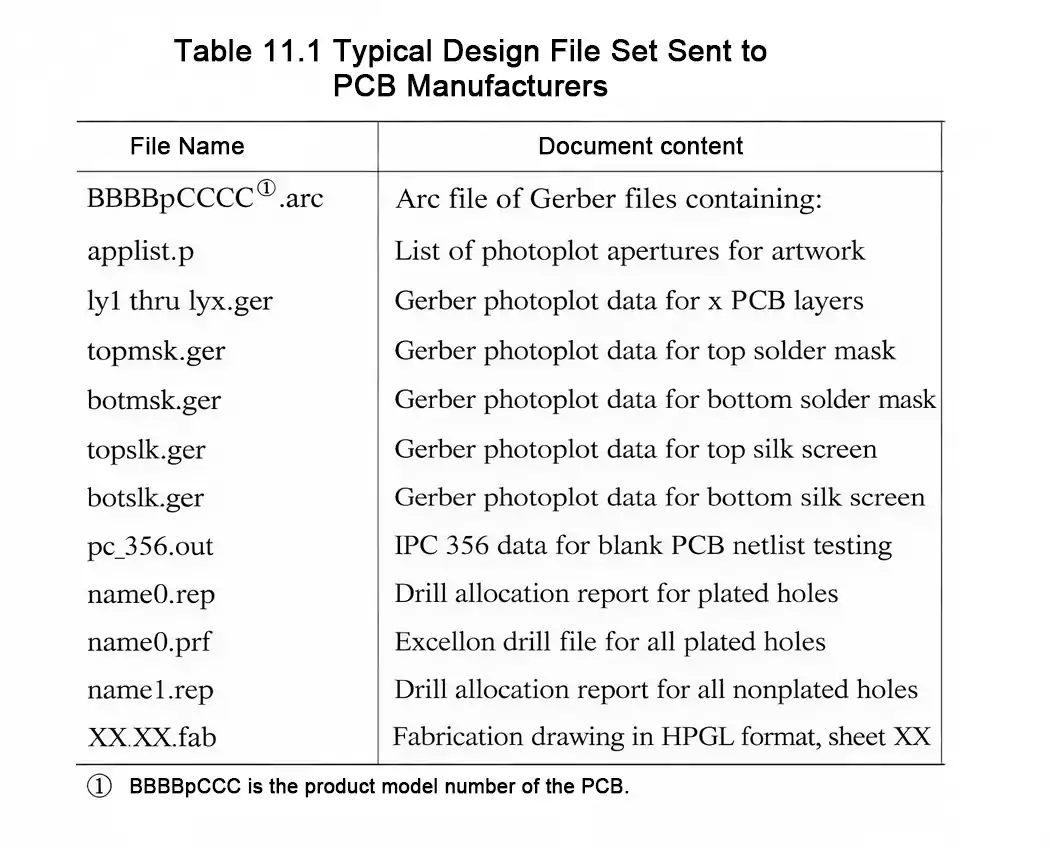

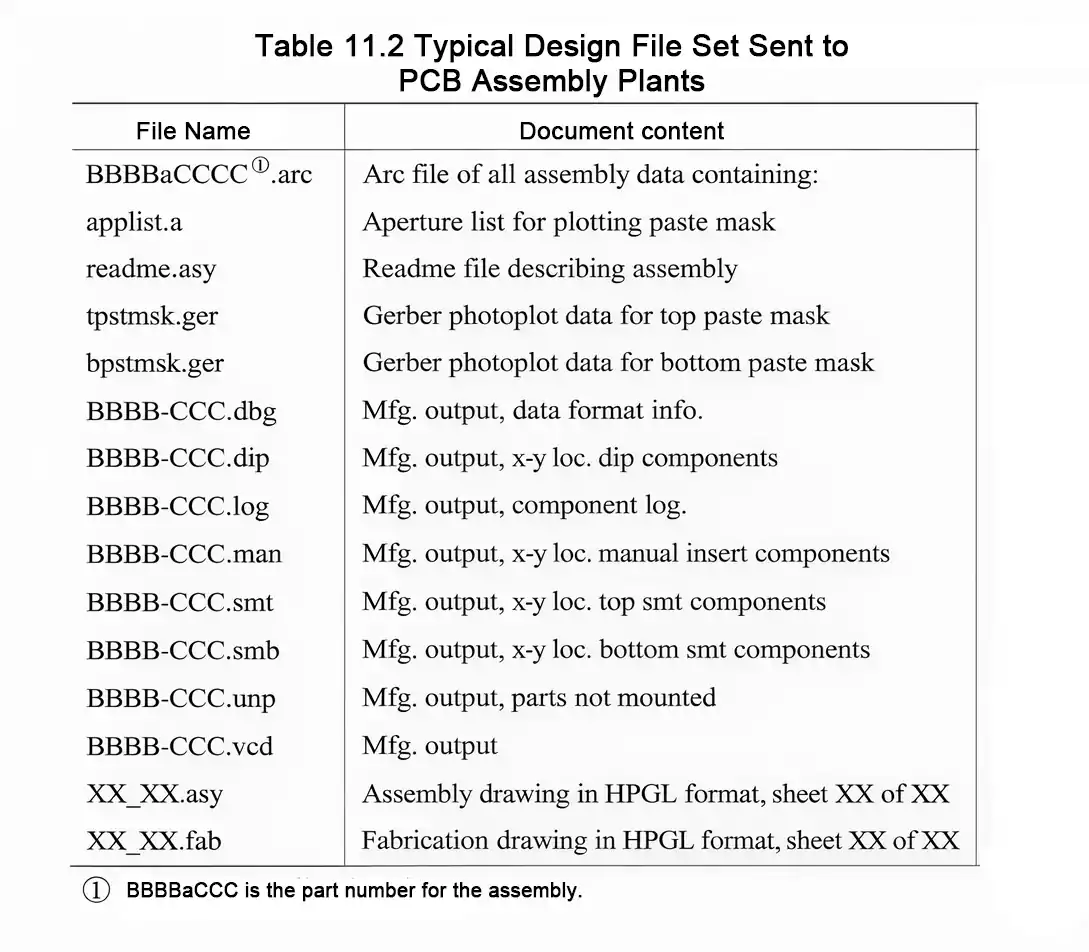

לאחר סיום האימות, זרימת התכנון עוברת לשחרור לייצור. חבילת שחרור מלאה כוללת בדרך כלל:

- קבצי ייצור (Gerber או ODB++)

- קבצי קידוח (Drill files)

- נתוני Pick-and-Place

- שרטוטי הרכבה (Assembly drawings)

- נתוני בדיקת לוח חשוף (Bare-board test) — לפי הצורך

- תיעוד בדיקות פונקציונליות — לפי הצורך

- BOM מלא ומאומת

אלו הם PCB manufacturing files שהיצרנים והמרכיבים משתמשים בהם בפועל. כל עמימות גורמת לעיכובים, סיכון לגרוטאות (Scrap) וירידת Yield. בחומרה B2B, בהירות ושלמות הקבצים קשורות ישירות ל-Lead time, חזרתיות ויכולת סקיילינג.

ארכוב תכנון: להגן על נכס ה-High-Speed PCB Design

השלב האחרון: ארכוב מובנה.

ארכוב אינו רק גיבוי. הוא תומך ב:

- גרסאות עתידיות ושינויים (ECOs)

- חקירת תקלות שטח (Field failure investigation)

- עקיבות גרסאות (Version traceability)

- ניהול מחזור חיים (Lifecycle management)

ארכיון מלא צריך לכלול את בסיס הנתונים המקורי, קבצי הייצור, מסמכי בדיקה, היסטוריית גרסאות והערות הנדסיות. חוסר יכולת לשחזר תכנון בעתיד הופך לסיכון עסקי ולא רק לאי-נוחות.

סיכום: High-Speed PCB Design דורש PCB Design Flow ממושמע

החצי השני של זרימת התכנון קובע האם תכנון PCB מהיר יגיע לייצור בצורה חלקה או ייכנס ללולאת דיבוג יקרה.

כאשר PCB routing constraints, PCB timing analysis, PCB routability analysis ו-high-speed PCB routing ממושמעים מבוצעים כתהליך מחובר — ומאומתים עם נתונים פיזיים אמיתיים — התוצאה היא לוח ש:

- מיוצר באופן עקבי

- מורכב בצורה אמינה

- עובר בדיקות ביעילות

- ניתן להרחבה לייצור סדרתי

- תומך בתחזוקה לאורך זמן

זה ההבדל בין לוח שעובד במעבדה לבין מוצר שנשלח לשוק בצורה אמינה.