Depois que a definição do sistema, a divisão funcional, a simulação e o placement (posicionamento de componentes) estão concluídos, o trabalho de high-speed PCB design entra na sua fase mais crítica.

Neste ponto, o objetivo não é mais apenas provar que o esquemático funciona. O objetivo é garantir que o design físico suporte edge rates reais, densidade de roteamento, limites de fabricação e repetibilidade na produção. Em outras palavras, é aqui que o PCB design flow passa da intenção de projeto para uma realidade fabricável.

Este guia cobre a segunda metade do PCB design flow para high-speed PCB design, com foco em high-speed PCB routing, PCB signal integrity, PCB timing analysis, PCB routing constraints, PCB routability analysis e na liberação de PCB manufacturing files completos.

PCB Routing Constraints: A Integridade de Sinal Começa Antes do High-Speed PCB Routing

Em projetos de baixa velocidade, a conectividade lógica costuma ser suficiente. Em high-speed PCB design, não.

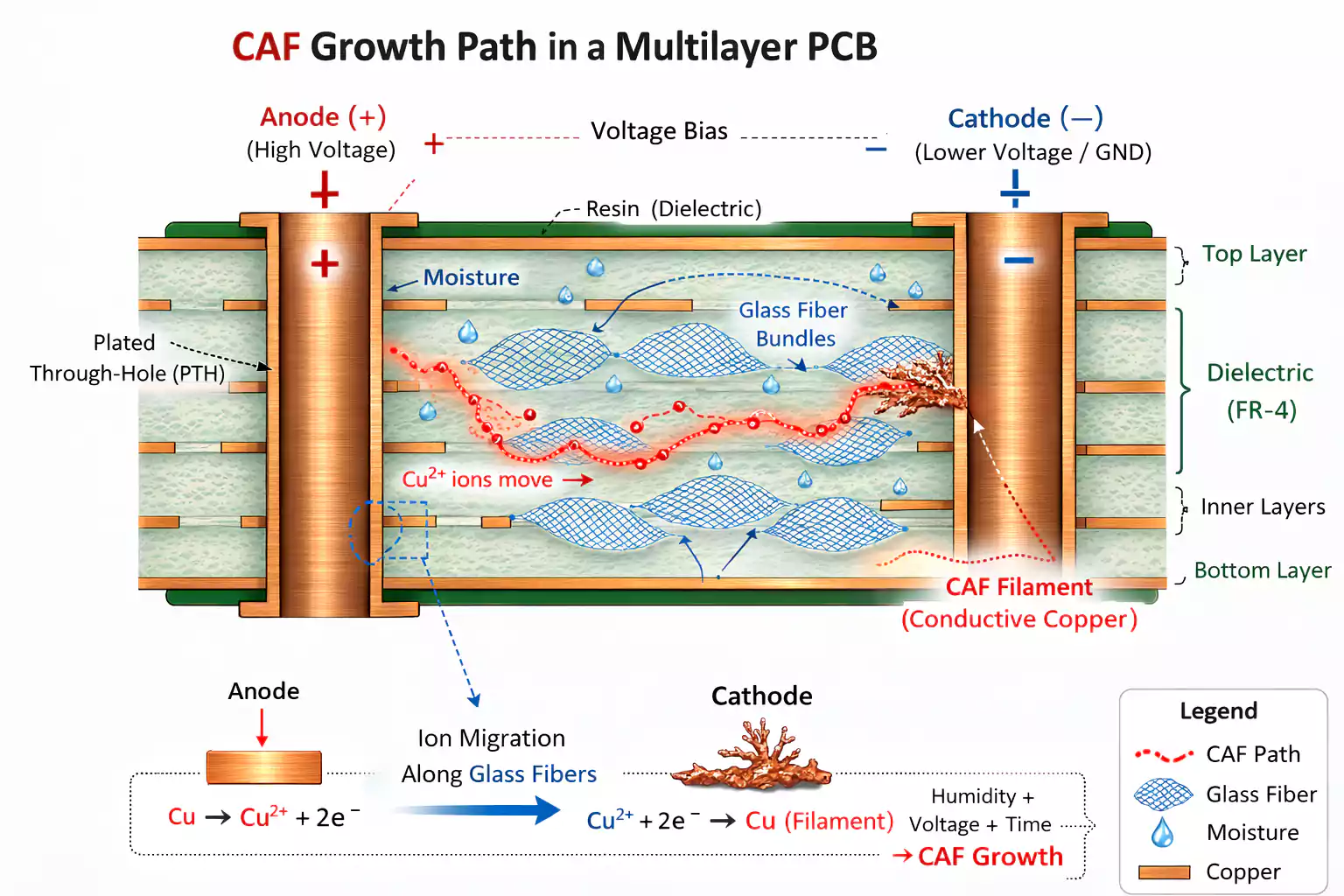

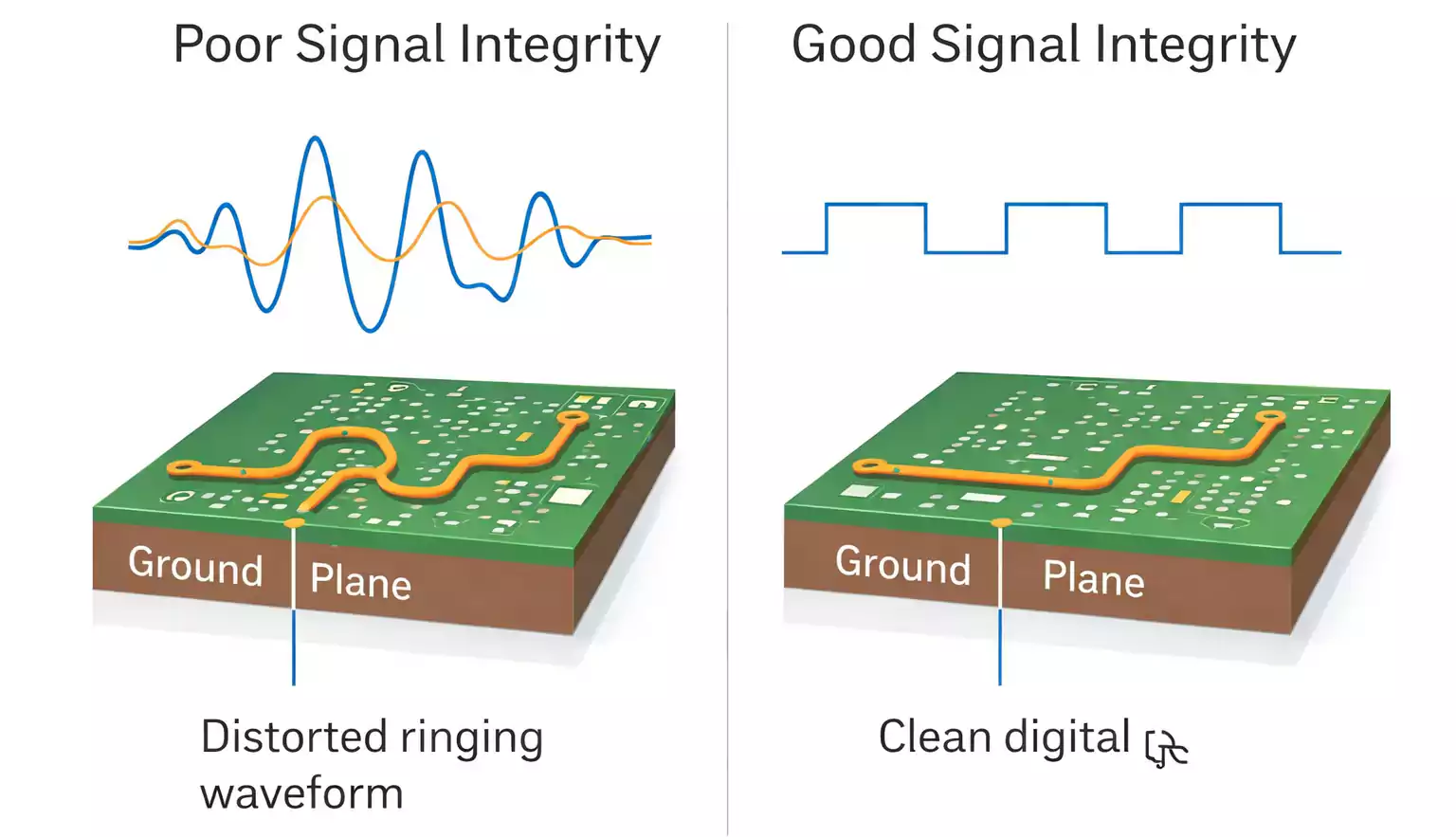

À medida que os edge rates aumentam e os atrasos de interconexão se tornam significativos, as trilhas (traces) passam a se comportar como linhas de transmissão. É aí que a geometria do layout impacta diretamente a PCB signal integrity. Modos de falha comuns incluem:

- Reflexões (Reflections)

- Crosstalk (diafonia)

- Ringing (oscilação)

- Overshoot e undershoot

- Comutação falsa / erros de limiar (false switching / threshold errors)

Por isso, defina e revise as routing constraints imediatamente após o placement — antes do high-speed routing detalhado.

As principais constraints normalmente incluem:

- Topologia driver-to-load

- Estratégia de terminação e posicionamento

- Ordem dos nós ao longo da rede (net)

- Controle de comprimento e limites de skew

- Consistência de impedância (single-ended e diferencial)

O objetivo é um comportamento de transmissão previsível antes de “fechar” o cobre. Em backplanes de alta velocidade e plataformas de computação, essas constraints são essenciais — pequenas escolhas físicas podem gerar grande instabilidade.

PCB Timing Analysis e Modelagem de Linha de Transmissão: Prever Antes de Roteiar

Quando o placement está estável, posições físicas e corredores aproximados de roteamento já são conhecidos. Mesmo antes do roteamento detalhado, isso permite PCB timing analysis antecipada e modelagem de linha de transmissão com base em:

- Comprimentos estimados e tempos de voo (flight times)

- Suposições de topologia (point-to-point vs. multi-drop)

- Sinais iniciais de risco para reflexões e distorção de borda

Como as coordenadas dos nós e a ordem de conexão estão definidas, os projetistas conseguem simular o comportamento provável e identificar problemas de margem de timing enquanto as mudanças ainda são simples.

O benefício é direto: corrigir problemas de PCB signal integrity depois do roteamento é caro; identificá-los antes do high-speed PCB routing é mais eficiente e controlável. Para equipes maduras de high-speed PCB design, a modelagem antecipada de timing e interconexão é uma etapa padrão de redução de risco no PCB design flow.

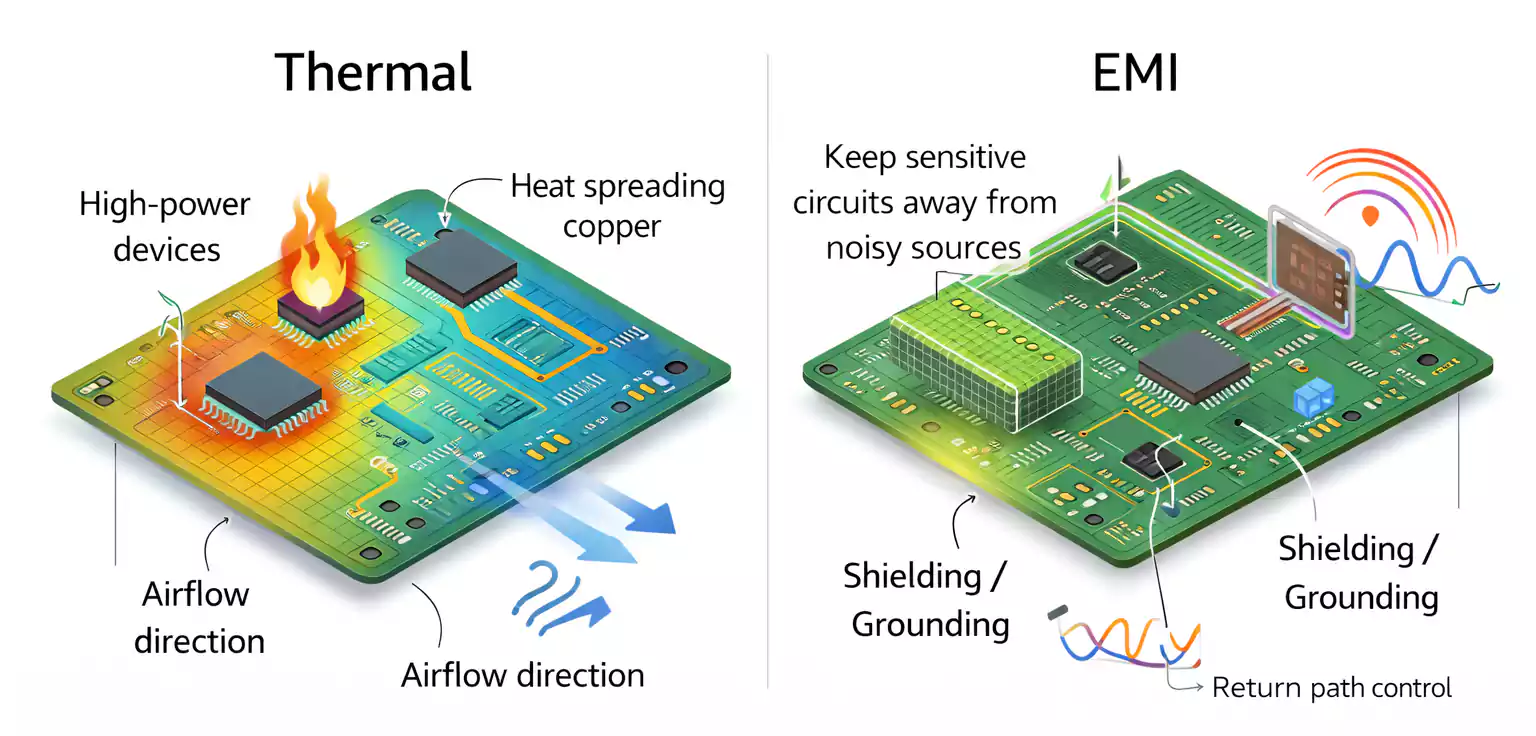

Ruído em PCB Signal Integrity: Ruído Interno vs. Interferência Externa

Nem todo ruído tem a mesma causa, e tratar todo problema de ruído do mesmo jeito leva a mitigação ineficaz. Uma abordagem mais limpa de PCB signal integrity é separar o ruído em duas categorias.

1) Ruído Interno do Sistema (Intrínseco)

Inclui:

- Ruído térmico (thermal noise)

- Ruído de comutação (switching noise)

- Ruído intrínseco de sinal (intrinsic signal noise)

O ruído interno faz parte do comportamento normal do circuito. Não dá para eliminá-lo totalmente, mas ele pode ser gerenciado melhorando a relação sinal-ruído e controlando a implementação física, incluindo caminhos de retorno (return paths), desacoplamento (decoupling) e gerenciamento de edge rate.

2) Interferência Externa (Acoplada / Ambiental)

Esse ruído se origina fora do circuito imediato e pode ser especialmente prejudicial em áreas sensíveis: analógico, RF-adjacent e mixed-signal.

Mitigações típicas incluem:

- Blindagem (shielding)

- Melhorias na estratégia de aterramento (grounding)

- Isolamento físico de blocos sensíveis

- Redes de filtro (filter networks)

- Design de interface controlada (controlled interface design)

Entender se o problema é intrínseco ou externo ajuda a escolher a correção certa e acelera o debug.

Se o Timing ou a SI Falhar: Revisar Placement e Topologia (Antes do Roteamento)

Se a modelagem inicial revelar:

- Atraso excessivo

- Margem de timing baixa

- Reflexões significativas

- Distorção de borda ou ringing

A resposta correta não é “roteia e vê”. Em high-speed PCB design, este é o momento de revisar placement e topologia.

Ações corretivas comuns incluem:

- Aproximar componentes críticos

- Encurtar caminhos de sinal prioritários

- Revisar a topologia (point-to-point vs. multi-drop)

- Adicionar, remover ou realocar terminação

- Ajustar o stackup para suportar as constraints

Em sistemas digitais na faixa de GHz — especialmente em placas fisicamente grandes — comprimento de layout e topologia impactam diretamente o comportamento global de timing. Iterar aqui aumenta a chance de first-pass success e evita reroutes tardios.

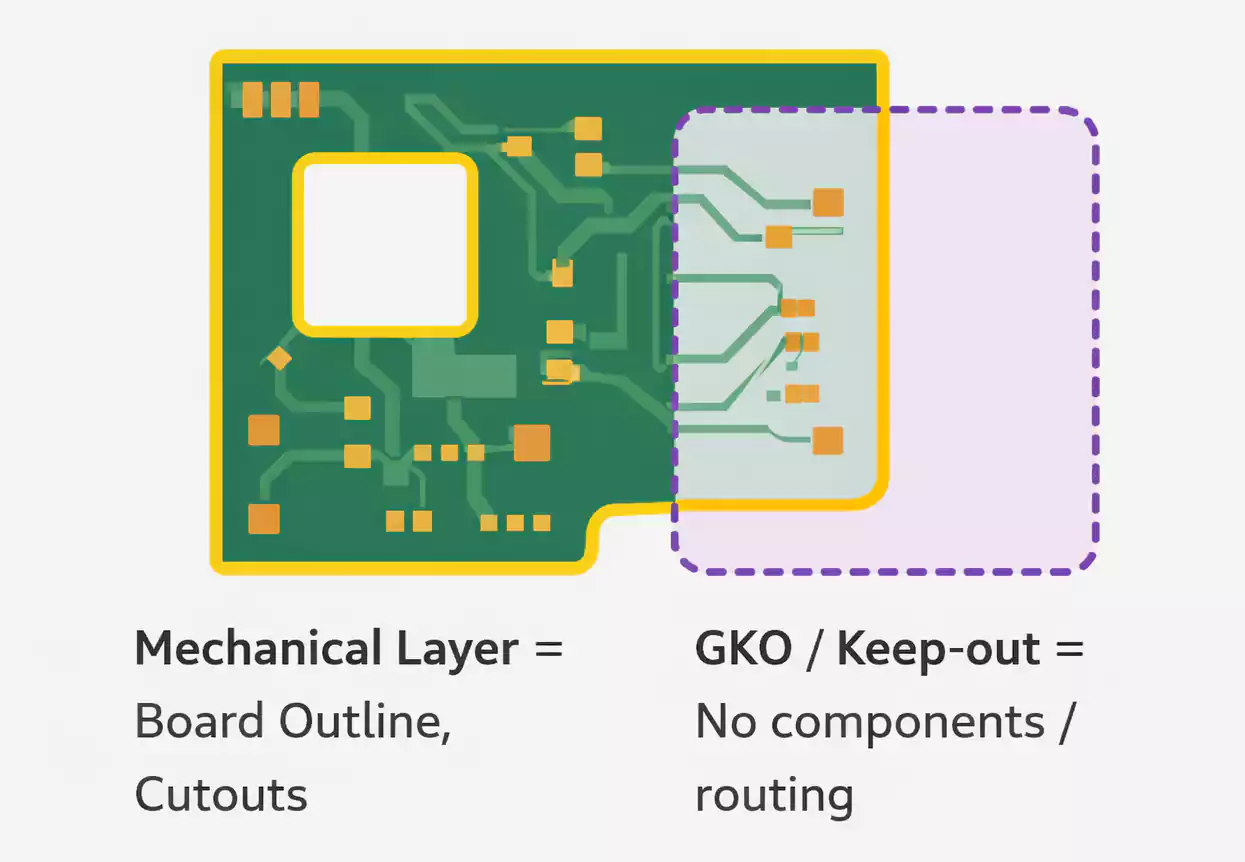

PCB Routability Analysis: Confirmar se Dá para Roteiar a Placa que Você Posicionou

Muitos projetos falham não por erros elétricos, mas por subestimar recursos de roteamento. Por isso, PCB routability analysis deve acontecer antes do roteamento detalhado.

Os checks de routability devem responder:

- Há camadas de sinal suficientes?

- O espaçamento do placement é realista para o fanout esperado?

- Onde estão os hot spots de congestionamento?

- Canais críticos estão bloqueados por restrições mecânicas ou keepouts?

- O floorplan suporta o stackup e a estratégia de vias planejados?

As ferramentas EDA modernas oferecem métricas de congestionamento e checks de viabilidade. Se a routability estiver fraca, a correção certa geralmente é revisar placement/camadas — não forçar um roteamento comprometido.

Essa etapa é especialmente importante em placas multilayer de alta densidade e layouts mixed-signal, onde as PCB routing constraints reduzem o espaço útil de roteamento.

High-Speed PCB Routing: Executar Dentro das Constraints, Não Contra Elas

Quando placement, PCB timing analysis e PCB routability analysis estão em boa forma, começa o high-speed PCB routing detalhado.

O roteamento deve obedecer às constraints definidas anteriormente, incluindo:

- Regras de largura e espaçamento de trilhas

- Casamento de comprimentos e controle de skew

- Requisitos de impedância

- Acoplamento e simetria de pares diferenciais

- Continuidade do caminho de retorno

- Limites de crosstalk e classes de espaçamento

Na prática, equipes de alto desempenho normalmente usam:

- Roteamento manual para nets críticas de alta velocidade

- Roteamento controlado para caminhos de distribuição de energia

- Roteamento automático para sinais não críticos

- Limpeza e otimização pós-roteamento

Um “playbook” de roteamento — política de camadas, regras de via, prioridades de net class e critérios de revisão — melhora a consistência e reduz churn de revisão em projetos com vários engenheiros.

Post-Route Verification: Fechar o Ciclo em SI, Timing e Conectividade

Terminar o roteamento não significa que o design acabou; agora, comprimentos e geometrias reais exigem revalidação.

Checks pós-roteamento normalmente incluem:

1) Rechecar PCB Signal Integrity e PCB Timing Analysis

- Confirmar margens de timing usando comprimentos reais

- Rechecar comportamento de reflexões e qualidade de borda

- Avaliar riscos de acoplamento entre nets agressoras/vítimas

2) Verificação de Netlist / Conectividade

- Garantir que não houve alterações de conectividade não intencionais

- Verificar se não foram introduzidos opens/shorts durante edições

3) Fabricabilidade e Conformidade de Regras

- Confirmar conformidade de largura/espaçamento

- Validar clearances de solder mask

- Garantir que pads não estejam expostos ou cobertos por engano

- Confirmar que estruturas de impedância são fabricáveis

É aqui que muitos problemas do tipo “funcionou no CAD” são evitados antes de virarem “falhou na fabricação/montagem”.

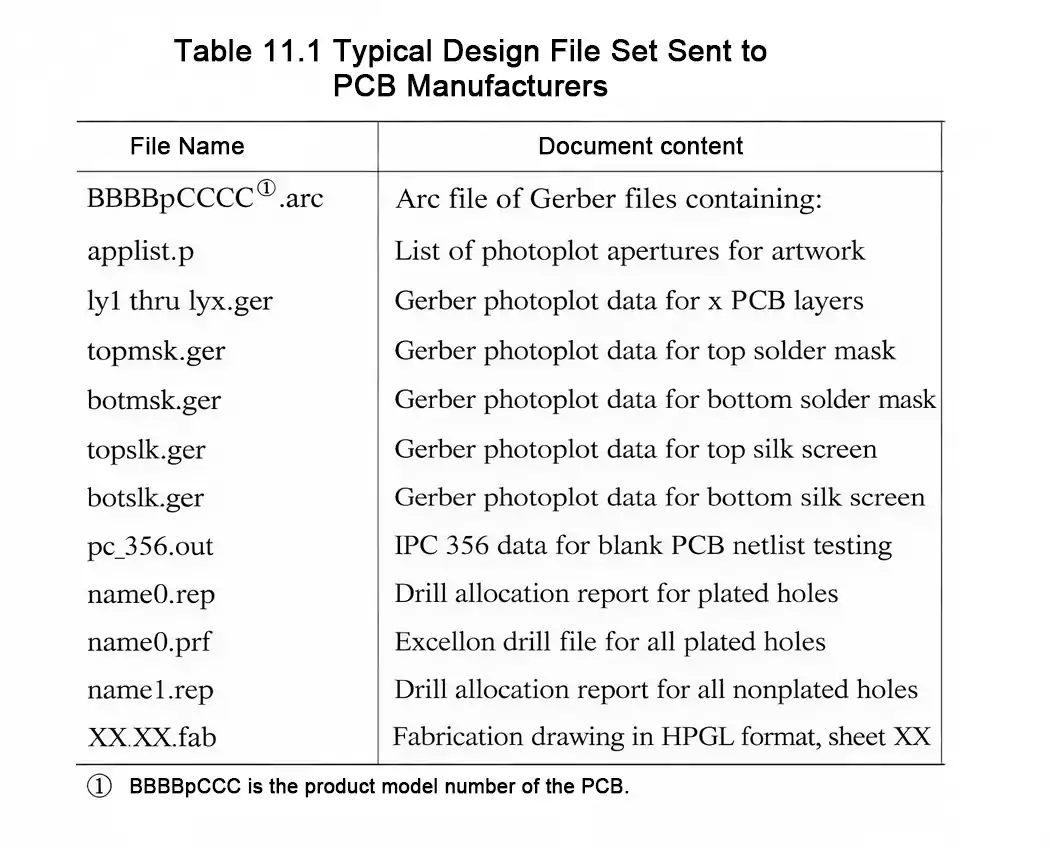

PCB Manufacturing Files: Do Banco de Dados do Design à Liberação Pronta para Produção

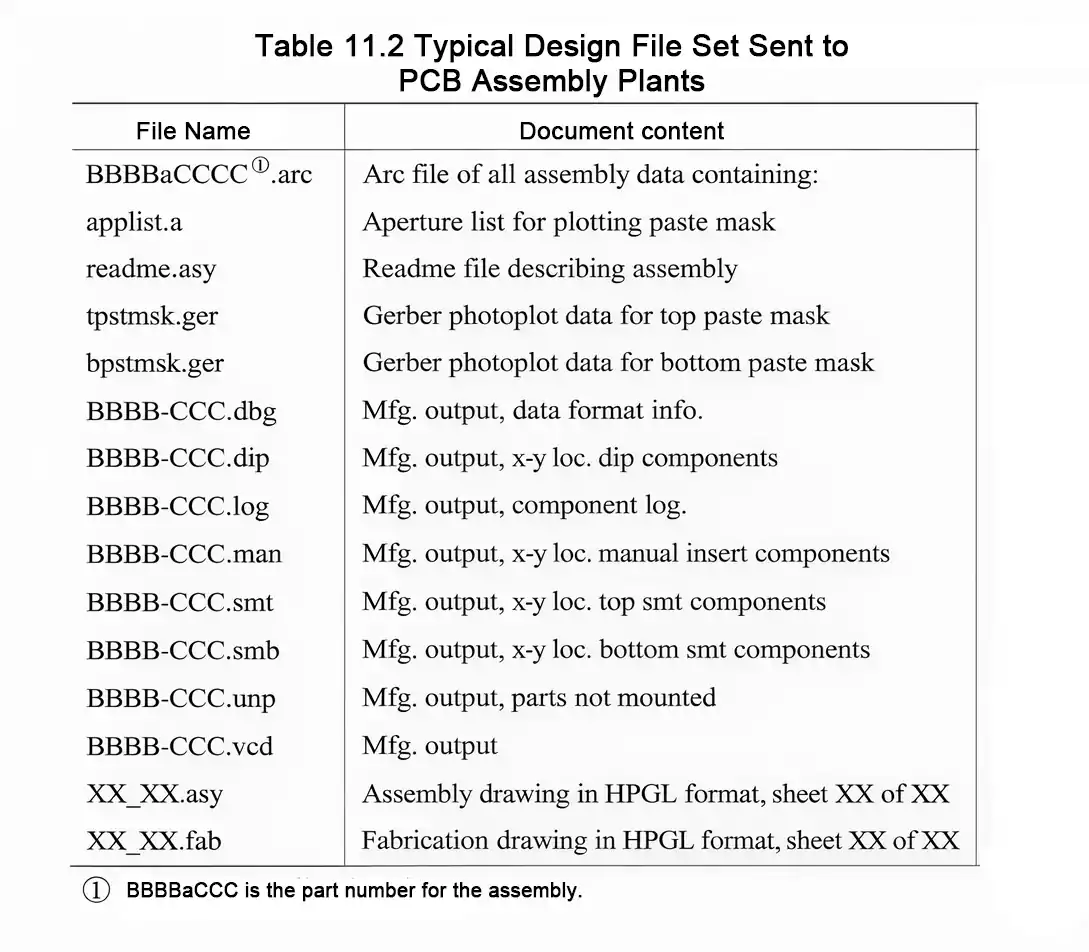

Depois que a verificação termina, o PCB design flow passa para a liberação de fabricação. Um pacote completo normalmente inclui:

- Saídas de fabricação (Gerber ou ODB++)

- Arquivos de furação (drill files)

- Dados de pick-and-place

- Desenhos de montagem (assembly drawings)

- Dados de teste de placa nua (se aplicável)

- Documentação de teste funcional (se aplicável)

- BOM completa e validada

Esses PCB manufacturing files são o que fabricantes e montadores realmente usam. Qualquer ambiguidade aqui causa atrasos, risco de sucata e perda de yield. Em hardware B2B, a clareza e a completude desses arquivos estão diretamente ligadas a lead time, repetibilidade e escalabilidade.

Design Archiving: Proteger o Ativo de High-Speed PCB Design

Etapa final: arquivamento estruturado.

Arquivar não é só fazer backup. Isso dá suporte a:

- Revisões futuras e ECOs

- Investigação de falhas em campo

- Rastreabilidade de versão

- Gestão de ciclo de vida

Um arquivo completo deve incluir o banco de dados nativo, saídas de fabricação, documentos de teste, histórico de revisão e notas de engenharia. Não conseguir reproduzir um design depois vira risco de negócio — não apenas inconveniente.

Considerações Finais: High-Speed PCB Design Depende de um PCB Design Flow Disciplinado

A segunda metade do PCB design flow define se um high-speed PCB design chega à produção de forma suave ou entra em um loop caro de debug.

Quando PCB routing constraints, PCB timing analysis, PCB routability analysis e high-speed PCB routing disciplinado são executados como um processo conectado — e verificados com dados físicos reais — o resultado é uma placa que:

- Fabrica de forma consistente

- Monta com confiabilidade

- Passa em testes com eficiência

- Escala para volume

- Dá suporte à manutenção de longo prazo

Essa é a diferença entre uma placa que funciona no laboratório e um produto que é enviado ao mercado com confiabilidade.