Una vez completadas la definición del sistema, la partición funcional, la simulación y el placement (colocación de componentes), el trabajo de diseño de PCB de alta velocidad entra en su fase más crítica.

En este punto, el objetivo ya no es únicamente demostrar que el esquema funciona. El objetivo es garantizar que el diseño físico pueda soportar edge rates reales, densidad de ruteado, límites de fabricación y repetibilidad en producción. En otras palabras, aquí es donde el PCB design flow pasa de la intención de diseño a una realidad fabricable.

Esta guía cubre la segunda mitad del flujo de diseño de PCB para PCB de alta velocidad, con foco en high-speed PCB routing, PCB signal integrity, PCB timing analysis, PCB routing constraints, PCB routability analysis y la entrega de un conjunto completo de PCB manufacturing files.

PCB Routing Constraints: La Integridad de Señal Empieza Antes del High-Speed PCB Routing

En diseños de baja velocidad, la conectividad lógica suele ser suficiente. En PCB de alta velocidad, no.

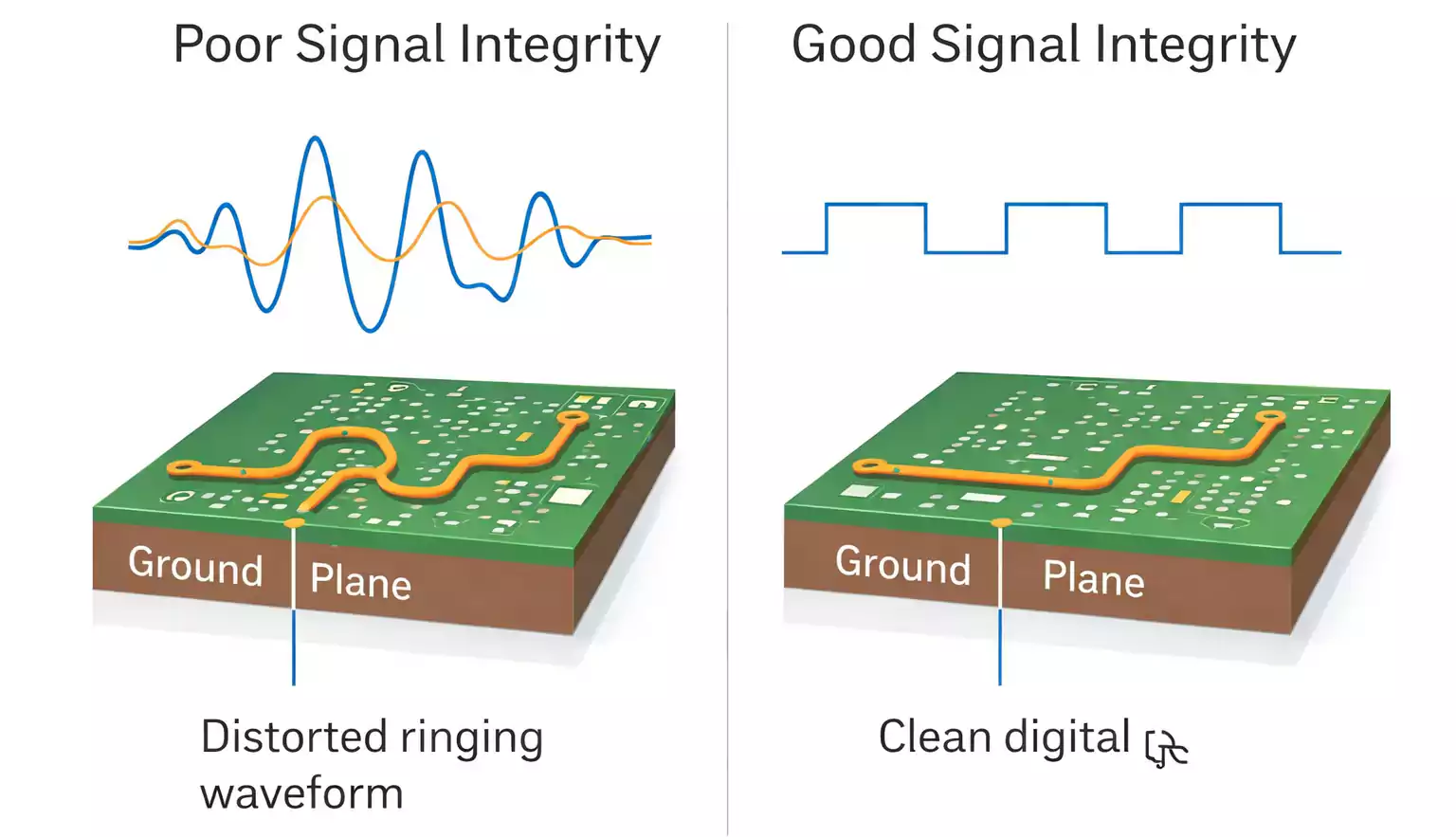

A medida que aumentan los edge rates y los retardos de interconexión se vuelven significativos, las pistas (traces) se comportan como líneas de transmisión. Es entonces cuando la geometría del layout impacta directamente en la integridad de señal (PCB signal integrity). Fallos comunes incluyen:

- Reflexiones

- Crosstalk (diafonía)

- Ringing (oscilación)

- Overshoot y undershoot

- Conmutaciones falsas / errores de umbral (false switching / threshold errors)

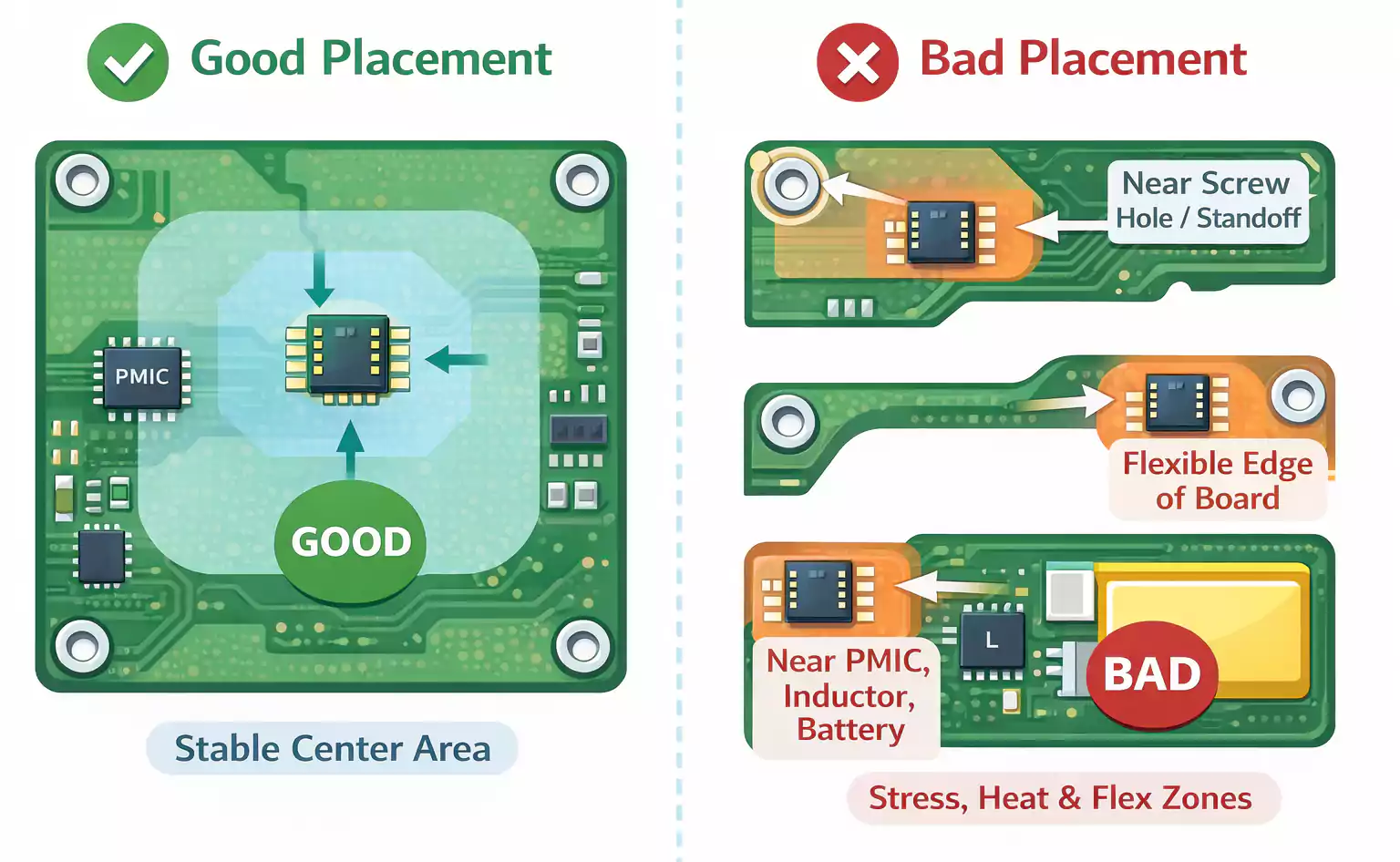

Por ello, define y revisa las routing constraints inmediatamente después del placement, antes del ruteado detallado de alta velocidad.

Las restricciones clave suelen incluir:

- Topología driver-to-load

- Estrategia de terminación y ubicación

- Orden de nodos a lo largo de la red (net)

- Control de longitud y límites de skew

- Consistencia de impedancia (single-ended y diferencial)

El objetivo es un comportamiento de transmisión predecible antes de “cerrar” el cobre. En backplanes de alta velocidad y plataformas de computación, estas restricciones son esenciales: pequeñas decisiones físicas pueden provocar inestabilidad significativa.

PCB Timing Analysis y Modelado de Línea de Transmisión: Predecir Antes de Rutar

Cuando el placement está estabilizado, las posiciones físicas y los corredores aproximados de ruteado ya son conocidos. Incluso antes del ruteado detallado, esto permite un PCB timing analysis temprano y un modelado de línea de transmisión basado en:

- Longitudes estimadas y tiempos de vuelo (flight times)

- Suposiciones de topología (point-to-point vs. multi-drop)

- Señales tempranas de riesgo de reflexiones y distorsión de borde

Como las coordenadas de los nodos y el orden de conexión están definidos, los diseñadores pueden simular el comportamiento probable e identificar problemas de margen de timing cuando los cambios aún son sencillos.

El valor es directo: corregir problemas de integridad de señal después del ruteado es caro; identificarlos antes del high-speed PCB routing es más eficiente y controlable. Para equipos maduros de diseño de PCB de alta velocidad, el modelado temprano de timing e interconexión es un paso estándar de reducción de riesgo dentro del PCB design flow.

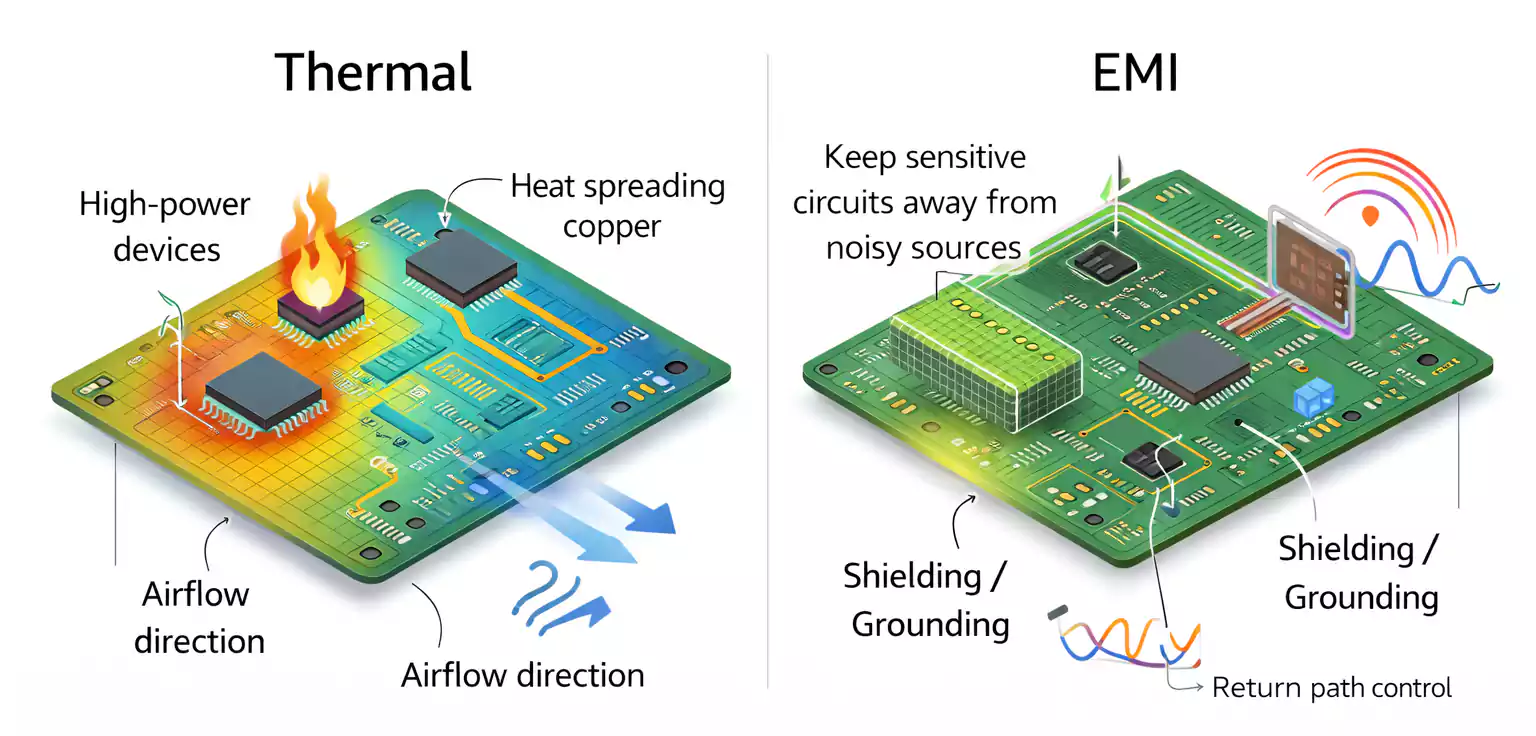

Ruido en PCB Signal Integrity: Ruido Interno vs. Interferencia Externa

No todo el ruido tiene la misma causa, y tratar todos los problemas de ruido igual conduce a mitigaciones ineficaces. Un enfoque más limpio de integridad de señal es separar el ruido en dos categorías.

1) Ruido Interno del Sistema (Intrínseco)

Incluye:

- Ruido térmico (thermal noise)

- Ruido de conmutación (switching noise)

- Ruido intrínseco de señal (intrinsic signal noise)

El ruido interno forma parte del comportamiento normal del circuito. No se puede eliminar, pero se puede gestionar mejorando la relación señal/ruido y controlando la implementación física, incluyendo caminos de retorno (return paths), desacoplo (decoupling) y gestión del edge rate.

2) Interferencia Externa (Acoplada / Ambiental)

Este ruido se origina fuera del circuito inmediato y puede ser especialmente dañino en áreas sensibles: analógico, RF-adjacent y mixed-signal.

Mitigaciones típicas:

- Blindaje (shielding)

- Mejoras en la estrategia de masa/puesta a tierra (grounding)

- Aislamiento físico de bloques sensibles

- Redes de filtrado (filter networks)

- Diseño de interfaces controlado (controlled interface design)

Entender si el problema es intrínseco o externo ayuda a elegir la corrección adecuada y acelera la depuración.

Si Falla el Timing o la SI: Revisar Placement y Topología (Antes del Ruteado)

Si el modelado temprano revela:

- Retardo excesivo

- Margen de timing bajo

- Reflexiones significativas

- Distorsión de borde o ringing

La respuesta correcta no es “rutar y ver qué pasa”. En PCB de alta velocidad, aquí es donde se revisa placement y topología.

Acciones correctivas comunes:

- Acercar componentes críticos entre sí

- Acortar rutas de señal prioritarias

- Revisar la topología (point-to-point vs. multi-drop)

- Añadir, eliminar o reubicar terminación

- Ajustar el stackup para soportar las restricciones

En sistemas digitales en el rango de GHz —especialmente en placas físicamente grandes— la longitud del layout y la topología afectan directamente al comportamiento global de timing. Iterar en esta fase aumenta el éxito en la primera pasada y evita rerouteos tardíos.

PCB Routability Analysis: Confirmar que Puedes Rutar la Placa que Has Colocado

Muchos diseños fallan no por errores eléctricos, sino por subestimar los recursos de ruteado. Por eso, la routability analysis debe hacerse antes del ruteado detallado.

Los checks de routability deben responder:

- ¿Tienes suficientes capas de señal?

- ¿El espaciado del placement es realista para el fanout esperado?

- ¿Dónde están los puntos calientes de congestión?

- ¿Hay canales críticos bloqueados por restricciones mecánicas o keepouts?

- ¿El floorplan soporta el stackup y la estrategia de vías prevista?

Las herramientas EDA modernas ofrecen métricas de congestión y checks de viabilidad de ruteado. Si la routability es débil, lo correcto suele ser revisar placement/capas, no forzar un ruteado comprometido.

Este paso es especialmente importante en placas multilayer de alta densidad y layouts mixed-signal, donde las routing constraints reducen el espacio útil de ruteado.

High-Speed PCB Routing: Ejecutar Dentro de las Restricciones, No Contra Ellas

Cuando placement, PCB timing analysis y PCB routability analysis están en buen estado, empieza el high-speed PCB routing detallado.

El ruteado debe cumplir las restricciones definidas, incluyendo:

- Reglas de ancho y separación de pista

- Igualación de longitudes y control de skew

- Requisitos de impedancia

- Acoplamiento y simetría de pares diferenciales

- Continuidad del camino de retorno

- Límites de crosstalk y clases de espaciado

En la práctica, equipos de alto rendimiento suelen usar:

- Ruteado manual para nets críticas de alta velocidad

- Ruteado controlado para rutas de distribución de potencia

- Ruteado automático para señales no críticas

- Limpieza y optimización post-route

Un “playbook” de ruteado —política de capas, reglas de vías, prioridades de net class y criterios de revisión— mejora la consistencia y reduce el churn de revisión en diseños con varios ingenieros.

Post-Route Verification: Cerrar el Bucle en SI, Timing y Conectividad

Terminar el ruteado no significa que el diseño esté listo; ahora, longitudes y geometrías reales requieren revalidación.

Los checks post-route suelen incluir:

1) Revisión de PCB Signal Integrity y PCB Timing Analysis

- Confirmar márgenes de timing con longitudes reales

- Rechequear reflexiones y calidad de borde

- Evaluar riesgos de acoplamiento entre nets agresoras/víctimas

2) Verificación de Netlist / Conectividad

- Asegurar que no hubo cambios de conectividad no intencionados

- Verificar que no se introdujeron opens/shorts durante ediciones

3) Fabricabilidad y Cumplimiento de Reglas

- Confirmar cumplimiento de ancho/separación

- Validar clearances de solder mask

- Asegurar que pads no estén expuestos o cubiertos por error

- Confirmar que estructuras de impedancia son fabricables

Aquí es donde muchos problemas de “funcionó en CAD” se evitan antes de convertirse en “falló en el montaje”.

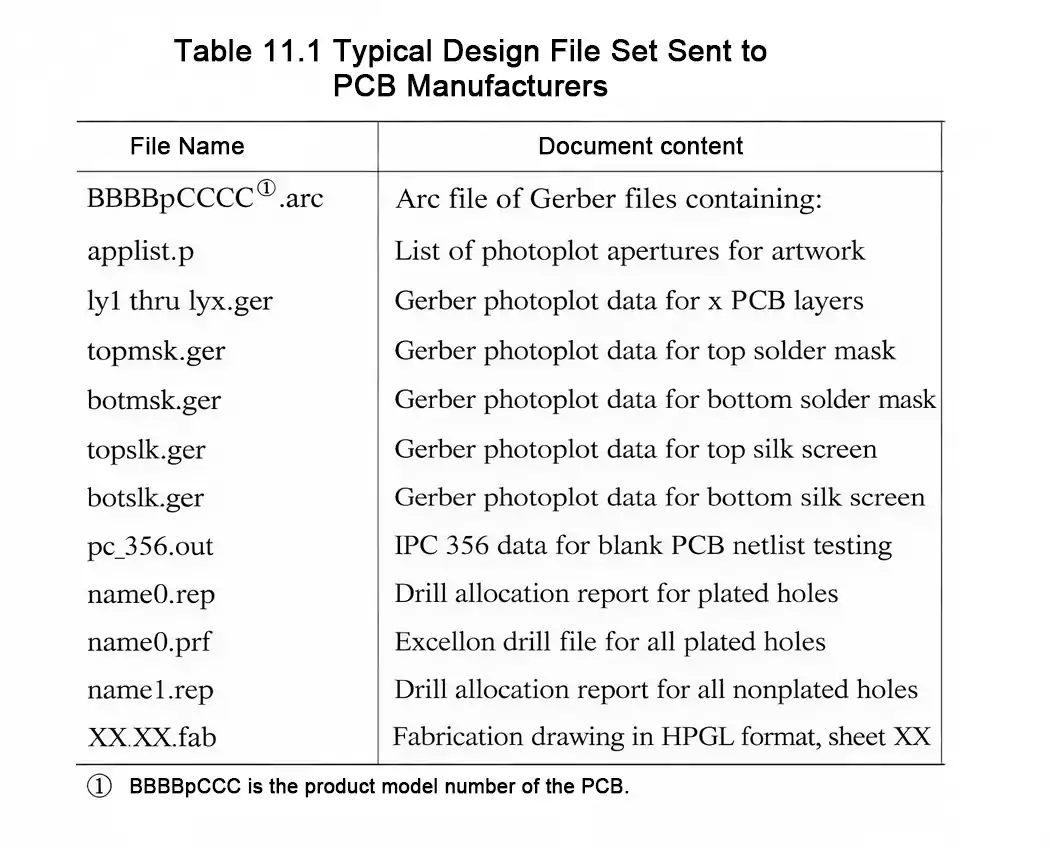

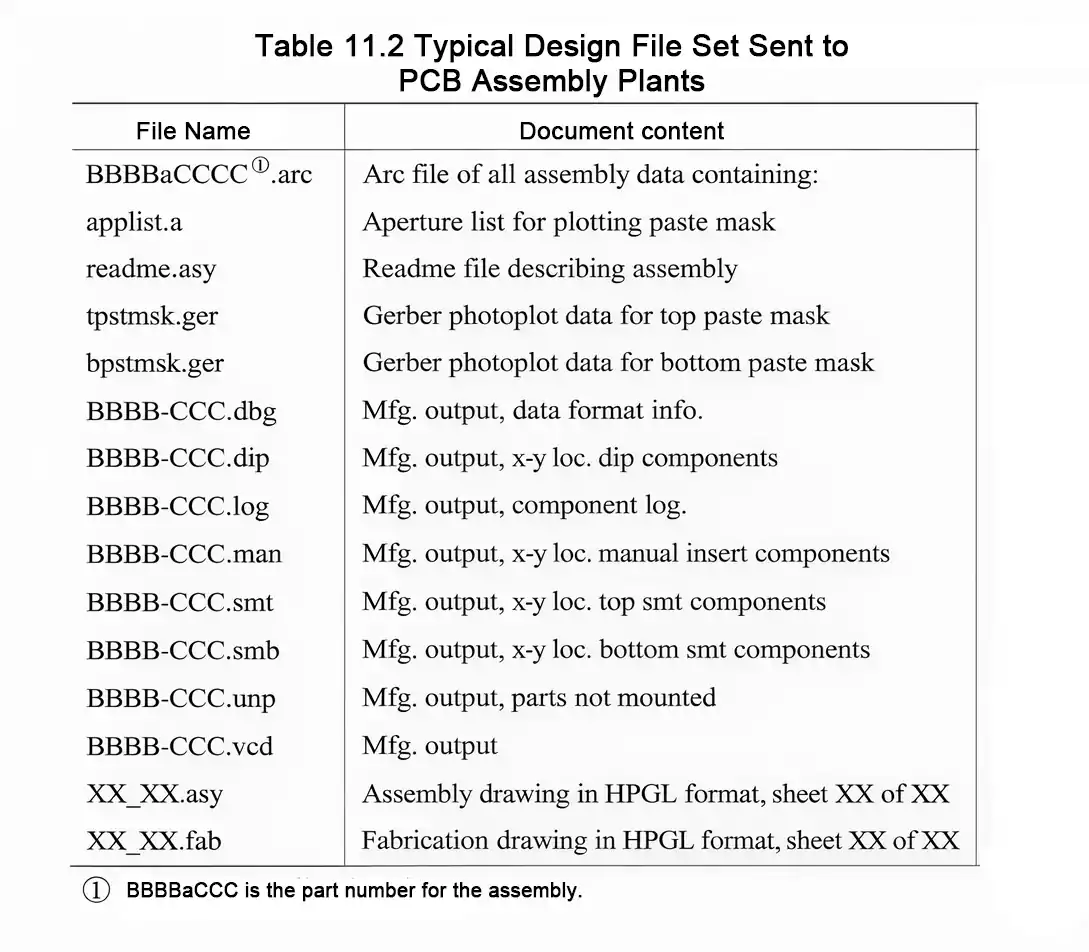

PCB Manufacturing Files: Del Diseño a un Paquete de Liberación Listo para Producción

Una vez completada la verificación, el PCB design flow pasa a la liberación para fabricación. Un paquete completo suele incluir:

- Salidas de fabricación (Gerber u ODB++)

- Archivos de taladrado (drill files)

- Datos de pick-and-place

- Planos de ensamblaje (assembly drawings)

- Datos de test de placa desnuda (si aplica)

- Documentación de test funcional (si aplica)

- BOM completa y validada

Estos PCB manufacturing files son los que usan realmente los fabricantes y montadores. Cualquier ambigüedad causa retrasos, riesgo de scrap y pérdida de yield. En hardware B2B, la claridad y completitud de los archivos están directamente ligadas al lead time, la repetibilidad y la escalabilidad.

Design Archiving: Proteger el Activo de High-Speed PCB Design

Último paso: archivado estructurado.

Archivar no es solo hacer backup. Da soporte a:

- Revisiones futuras y ECOs

- Investigación de fallos en campo

- Trazabilidad de versiones

- Gestión del ciclo de vida

Un archivo completo debe incluir la base de datos nativa, salidas de fabricación, documentos de test, historial de revisiones y notas de ingeniería. No poder reproducir un diseño en el futuro se convierte en un riesgo de negocio, no solo en un inconveniente.

Conclusión: El High-Speed PCB Design Depende de un PCB Design Flow Disciplinado

La segunda mitad del PCB design flow determina si un diseño de PCB de alta velocidad llega a producción sin problemas o entra en un costoso bucle de depuración.

Cuando PCB routing constraints, PCB timing analysis, PCB routability analysis y un high-speed PCB routing disciplinado se ejecutan como un proceso conectado —y se verifican con datos físicos reales— el resultado es una placa que:

- Se fabrica de forma consistente

- Se ensambla con fiabilidad

- Pasa test con eficiencia

- Escala a volumen

- Soporta mantenimiento a largo plazo

Esa es la diferencia entre una placa que funciona en el laboratorio y un producto que se entrega de forma fiable.