بعد الانتهاء من تعريف النظام، وتقسيم الوظائف، والمحاكاة، وتوزيع المكوّنات (Placement)، يدخل العمل في تصميم لوحات PCB عالية السرعة مرحلته الأكثر حساسية.

في هذه المرحلة لم يعد الهدف هو إثبات أن المخطط الكهربائي (Schematic) يعمل فحسب، بل التأكد من أن التصميم الفيزيائي قادر على تحمّل معدلات الحواف السريعة (Edge Rates)، وكثافة التوجيه، وحدود التصنيع، وقابلية التكرار في الإنتاج. بمعنى آخر، هنا ينتقل تدفّق تصميم PCB من “نية التصميم” إلى “واقع قابل للتصنيع”.

يغطي هذا الدليل النصف الثاني من تدفّق تصميم PCB الخاص بـ تصميم PCB عالي السرعة، مع التركيز على:

توجيه PCB عالي السرعة، وسلامة الإشارة (PCB Signal Integrity)، وتحليل التوقيت (PCB Timing Analysis)، وقيود التوجيه (PCB Routing Constraints)، وتحليل قابلية التوجيه (PCB Routability Analysis)، وإصدار ملفات التصنيع الكاملة (PCB Manufacturing Files).

قيود توجيه PCB: سلامة الإشارة تبدأ قبل توجيه PCB عالي السرعة

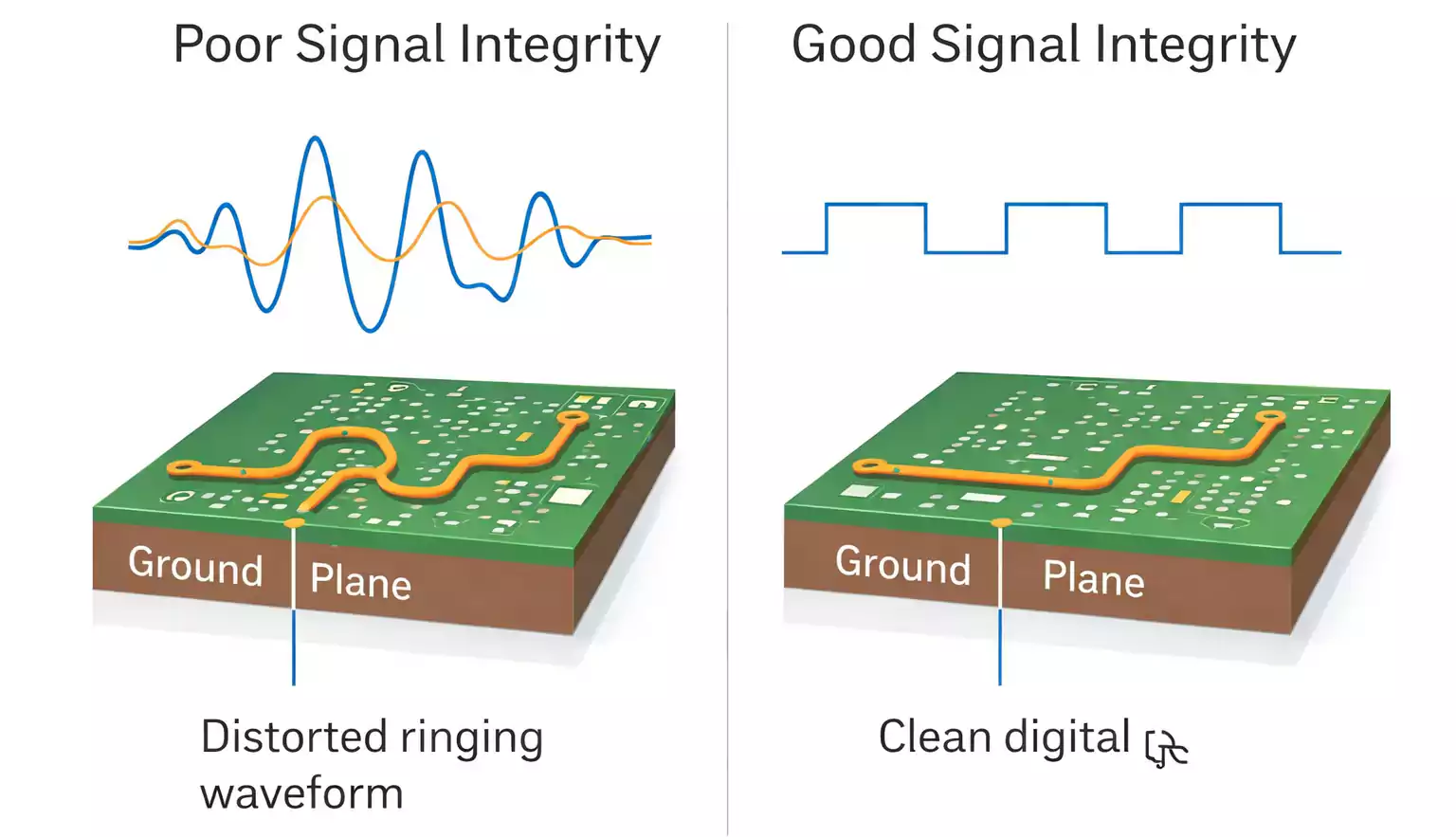

في التصاميم منخفضة السرعة، غالبًا ما تكون سلامة الاتصال المنطقي كافية. أما في تصميم PCB عالي السرعة فالأمر مختلف.

مع زيادة سرعة الحواف وارتفاع تأثير تأخيرات التوصيل، تتصرف المسارات (Traces) كخطوط نقل (Transmission Lines). وهنا تصبح هندسة التخطيط عاملًا مؤثرًا مباشرة في سلامة الإشارة. ومن الأعطال الشائعة:

- الانعكاسات (Reflections)

- التداخل المتبادل (Crosstalk)

- الرنين (Ringing)

- التجاوز والهبوط (Overshoot / Undershoot)

- تبديل خاطئ / أخطاء عتبات المنطق (False Switching / Threshold Errors)

لذلك يجب تعريف قيود التوجيه ومراجعتها مباشرة بعد التوزيع (Placement) وقبل البدء بالتوجيه التفصيلي عالي السرعة.

تشمل القيود الرئيسية عادةً:

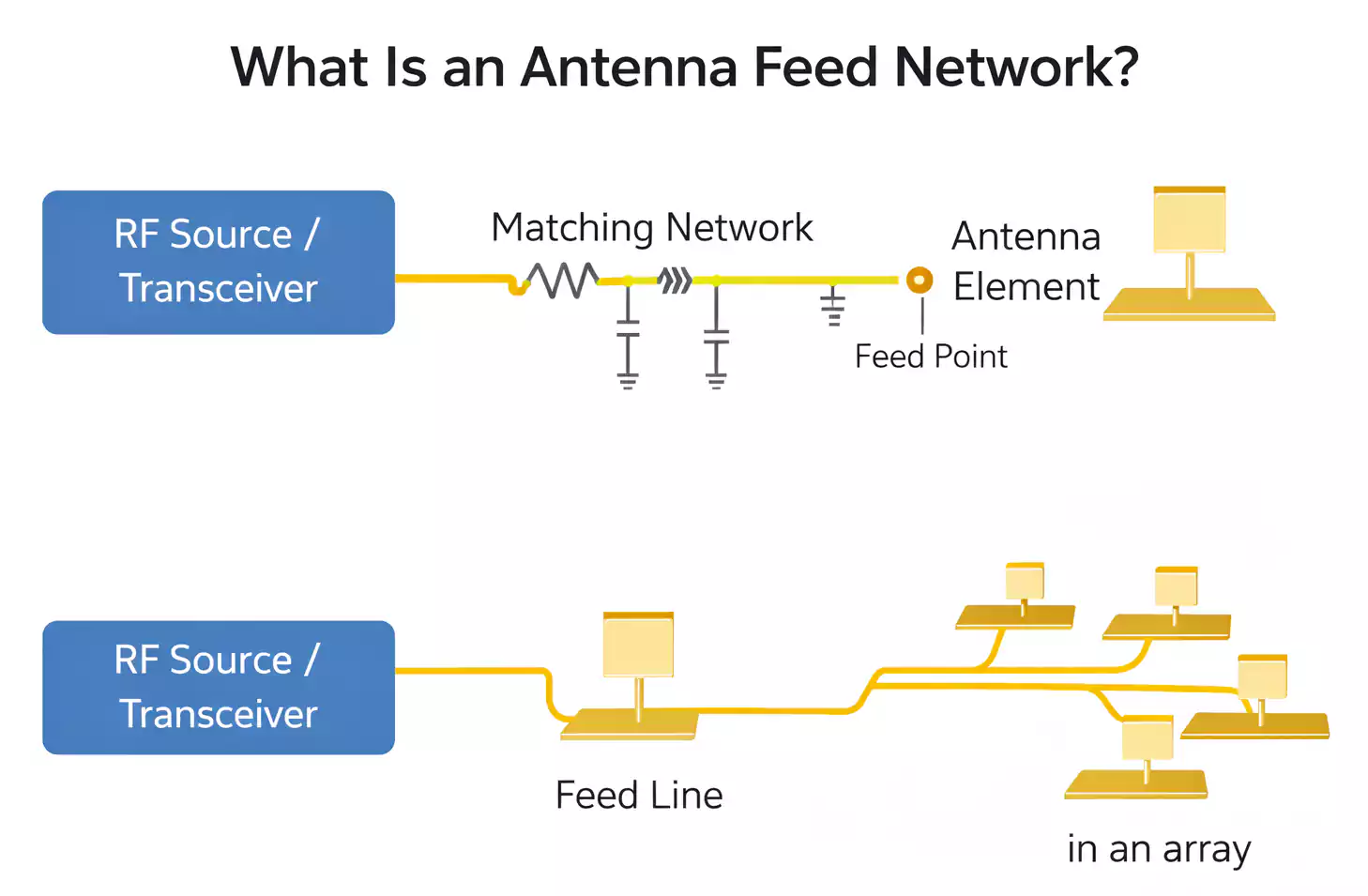

- طوبولوجيا الربط بين السائق والحمل (Driver-to-Load Topology)

- استراتيجية الإنهاء (Termination) وموقعها

- ترتيب العقد على الشبكة (Node Ordering)

- التحكم بطول المسار وحدود انحراف التوقيت (Skew Limits)

- ثبات الممانعة (Impedance) أحادي الطرف وتفاضليًا

الهدف هو ضمان سلوك نقل متوقع قبل “تثبيت النحاس” فعليًا على اللوحة. في لوحات الظهر عالية السرعة (Backplanes) ومنصات الحوسبة، هذه القيود أساسية—قرارات فيزيائية صغيرة قد تؤدي إلى عدم استقرار كبير.

تحليل التوقيت ونمذجة خطوط النقل: توقّع الأداء قبل التوجيه

عندما يصبح التوزيع ثابتًا، تكون مواقع المكوّنات ومسارات التوجيه التقريبية معروفة. حتى قبل التوجيه التفصيلي، يتيح ذلك إجراء تحليل توقيت مبكر ونمذجة خطوط النقل اعتمادًا على:

- تقدير أطوال المسارات وأزمنة انتقال الإشارة (Flight Times)

- افتراضات الطوبولوجيا (نقطة إلى نقطة مقابل متعدد التفرعات)

- مؤشرات مبكرة لاحتمالات الانعكاس وتشوه الحواف

وبما أن إحداثيات العقد وترتيب الاتصال معروفان، يمكن للمصممين محاكاة السلوك المتوقع واكتشاف مشاكل هامش التوقيت بينما لا تزال التعديلات سهلة.

القيمة هنا واضحة: إصلاح مشاكل سلامة الإشارة بعد التوجيه مكلف؛ بينما كشفها قبل توجيه PCB عالي السرعة أكثر كفاءة ويمكن التحكم به. بالنسبة لفرق تصميم PCB عالية السرعة الناضجة، يُعد تحليل التوقيت والنمذجة المبكرة خطوة معيارية لتقليل المخاطر ضمن تدفّق تصميم PCB.

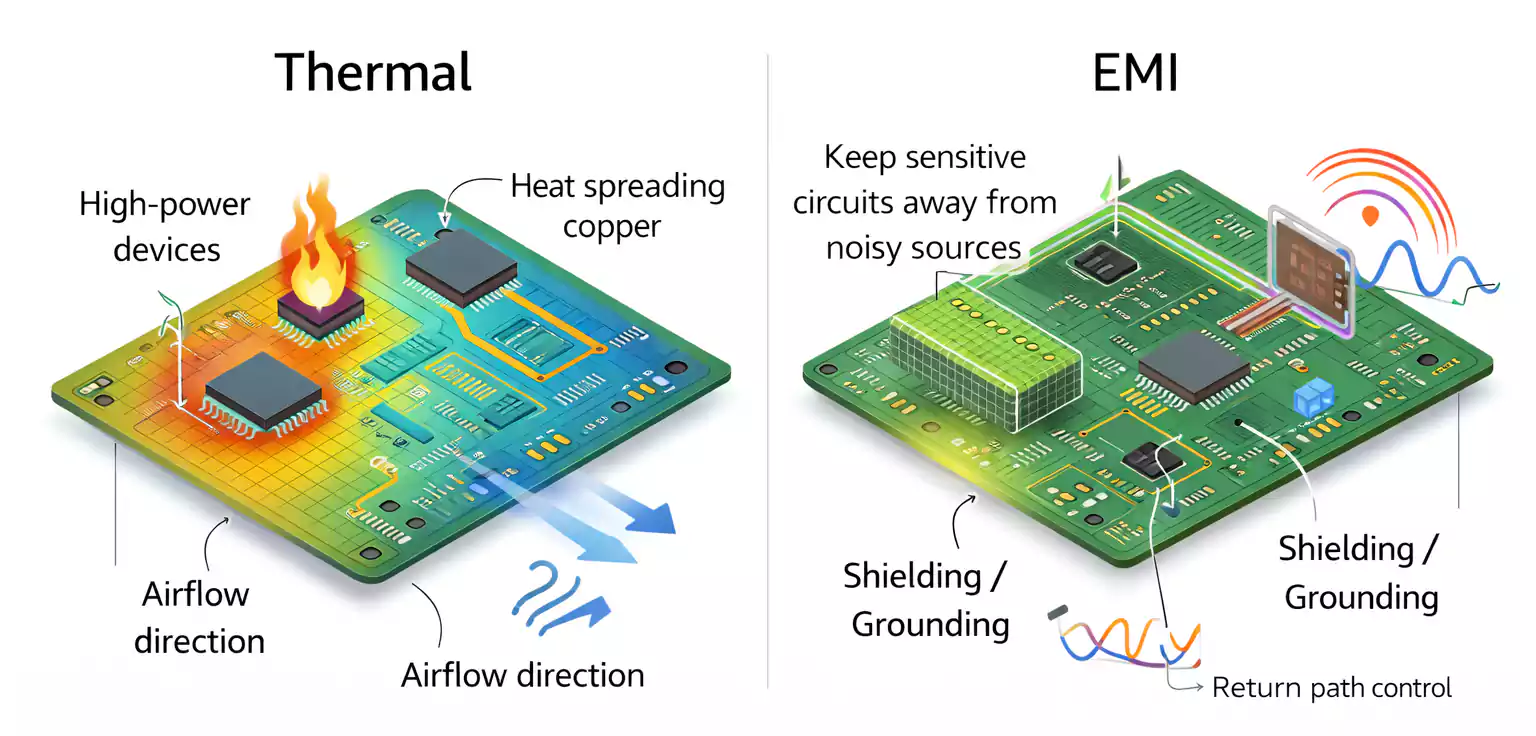

ضوضاء سلامة الإشارة: ضوضاء داخلية مقابل تداخل خارجي

ليست كل الضوضاء ناتجة عن السبب نفسه، والتعامل مع جميع مشاكل الضوضاء بالطريقة ذاتها يؤدي غالبًا إلى حلول غير فعّالة. الأفضل في سلامة الإشارة هو تقسيم الضوضاء إلى فئتين:

1) ضوضاء النظام الداخلية (Intrinsic)

وتشمل:

- الضوضاء الحرارية (Thermal Noise)

- ضوضاء التحويل (Switching Noise)

- ضوضاء الإشارة الذاتية (Intrinsic Signal Noise)

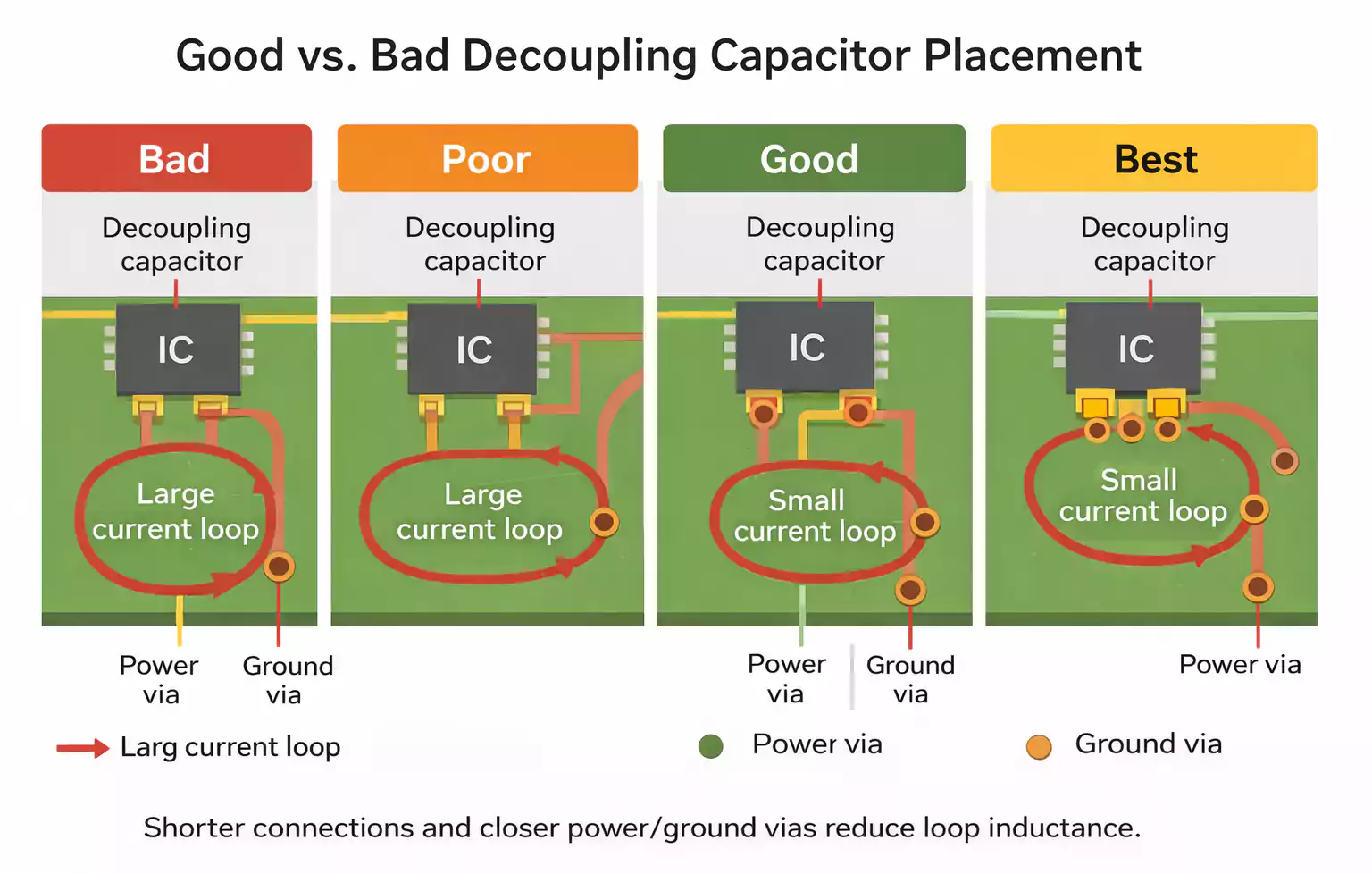

هذه الضوضاء جزء من سلوك الدائرة الطبيعي ولا يمكن إلغاؤها بالكامل، لكن يمكن إدارتها عبر تحسين نسبة الإشارة إلى الضوضاء والتحكم بالتنفيذ الفيزيائي، بما في ذلك مسارات العودة (Return Paths)، وإزالة التموجات (Decoupling)، وإدارة سرعة الحواف.

2) تداخل خارجي (Coupled / Environmental)

ينشأ خارج الدائرة المباشرة، وقد يكون شديد الضرر في الدوائر الحساسة، والأنظمة القريبة من RF، والأنظمة المختلطة (Mixed-Signal).

تخفيفه يتم عادة عبر:

- التدريع (Shielding)

- تحسين استراتيجية التأريض (Grounding)

- عزل المناطق الحساسة فيزيائيًا

- شبكات الترشيح (Filter Networks)

- تصميم واجهات مضبوط (Controlled Interfaces)

معرفة ما إذا كانت المشكلة داخلية أم خارجية يساعد في اختيار الحل الصحيح ويُسرّع عملية تتبع الأعطال.

إذا فشل التوقيت أو سلامة الإشارة: عد إلى التوزيع والطوبولوجيا (قبل التوجيه)

إذا أظهرت النمذجة المبكرة:

- تأخيرًا مفرطًا

- هامش توقيت ضعيف

- انعكاسات واضحة

- تشوهًا في الحواف أو رنينًا

فلا ينبغي أن تكون الاستجابة “لنوجّه ونرى”. في تصميم PCB عالي السرعة، هذه هي اللحظة التي يجب فيها تعديل التوزيع والطوبولوجيا.

إجراءات التصحيح الشائعة تشمل:

- تقريب المكوّنات الحرجة من بعضها

- تقصير المسارات ذات الأولوية

- تعديل الطوبولوجيا (نقطة إلى نقطة مقابل متعدد التفرعات)

- إضافة/إزالة/نقل عناصر الإنهاء (Termination)

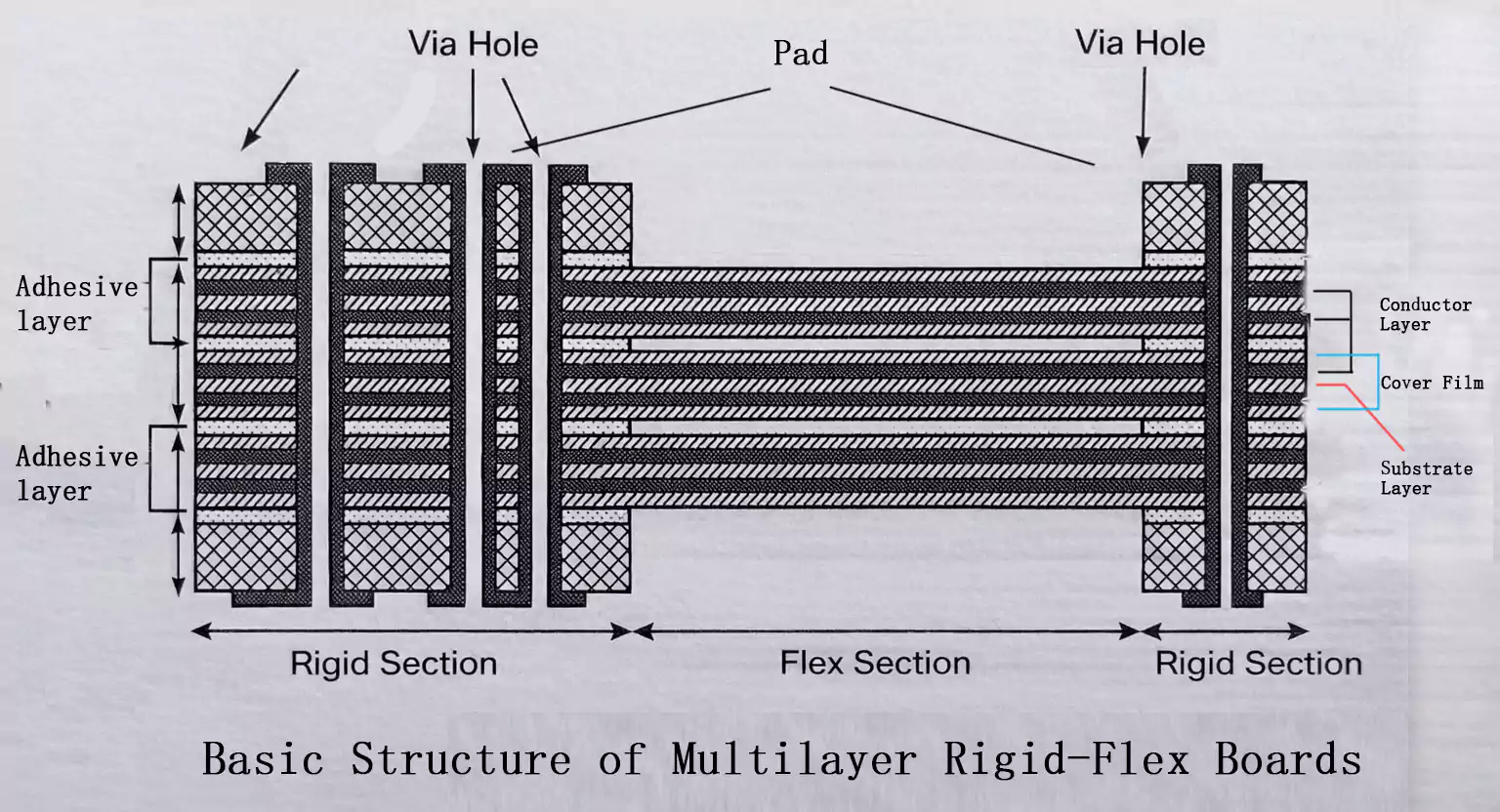

- تعديل طبقات اللوحة (Stackup) لدعم القيود

في الأنظمة الرقمية بترددات جيجاهرتز—خصوصًا على اللوحات الكبيرة—يؤثر طول التخطيط والطوبولوجيا مباشرة على سلوك التوقيت العام. التكرار والتحسين في هذه المرحلة يزيدان فرص نجاح أول نسخة ويمنعان إعادة توجيه متأخرة مكلفة.

تحليل قابلية التوجيه: تأكد أنك تستطيع توجيه اللوحة التي وزّعتها

تفشل كثير من التصاميم ليس بسبب أخطاء كهربائية، بل بسبب التقليل من موارد التوجيه. لذلك يجب إجراء تحليل قابلية التوجيه (Routability) قبل التوجيه التفصيلي.

أسئلة يجب أن يجيب عنها التحليل:

- هل لديك عدد كافٍ من طبقات الإشارة؟

- هل المسافات بين المكوّنات واقعية بالنسبة لتشعب الأرجل (Fanout)؟

- أين مناطق الازدحام (Congestion Hot Spots)؟

- هل هناك قنوات حرجة محجوبة بقيود ميكانيكية أو مناطق منع (Keepouts)؟

- هل يدعم تقسيم اللوحة (Floorplan) الطبقات واستراتيجية الثقوب (Via Strategy) المطلوبة؟

تقدم أدوات EDA الحديثة مؤشرات ازدحام وفحوصات جدوى التوجيه. إذا كانت القابلية ضعيفة، فالحل الصحيح غالبًا هو تعديل التوزيع/الطبقات، وليس إجبار المسارات على حلول سيئة.

هذه الخطوة مهمة جدًا في اللوحات متعددة الطبقات عالية الكثافة، واللوحات المختلطة، حيث تقلل قيود التوجيه من مساحة التوجيه المتاحة.

توجيه PCB عالي السرعة: نفّذ ضمن القيود لا ضدها

بعد التأكد من سلامة التوزيع، ونتائج تحليل التوقيت، وقابلية التوجيه، يبدأ التوجيه التفصيلي للـ PCB عالي السرعة.

يجب أن يلتزم التوجيه بالقيود المحددة سابقًا، مثل:

- قواعد عرض المسار والمسافات (Trace Width/Spacing)

- مطابقة الأطوال والتحكم بالانحراف (Length Matching / Skew)

- متطلبات الممانعة (Impedance)

- اقتران وتماثل الأزواج التفاضلية

- استمرارية مسار العودة (Return Path Continuity)

- حدود التداخل المتبادل والمسافات المصنّفة

عمليًا، الفرق عالية الأداء تعتمد عادة:

- توجيهًا يدويًا للشبكات الحرجة عالية السرعة

- توجيهًا مضبوطًا لمسارات توزيع الطاقة

- توجيهًا آليًا للإشارات غير الحرجة

- تنظيفًا وتحسينًا بعد التوجيه

كما أن وجود “دليل توجيه” (Routing Playbook)—يشمل سياسة الطبقات، وقواعد الـ Via، وأولويات فئات الشبكات، ومعايير المراجعة—يحسن الاتساق ويقلل وقت المراجعات في التصاميم متعددة المهندسين.

التحقق بعد التوجيه: إغلاق الحلقة على سلامة الإشارة والتوقيت والاتصال

إنهاء التوجيه لا يعني انتهاء التصميم؛ الآن أصبحت الأطوال والهندسة الفعلية معروفة، ويجب إعادة التحقق منها.

تشمل فحوصات ما بعد التوجيه عادة:

1) إعادة فحص سلامة الإشارة وتحليل التوقيت

- تأكيد هوامش التوقيت باستخدام الأطوال الفعلية

- إعادة فحص الانعكاسات وجودة الحواف

- تقييم مخاطر الاقتران بين شبكات معتدية/متضررة (Aggressor/Victim)

2) التحقق من الشبكة/الاتصال (Netlist / Connectivity)

- التأكد من عدم حدوث تغييرات اتصال غير مقصودة

- التحقق من عدم إدخال انقطاعات أو قصور أثناء التعديلات

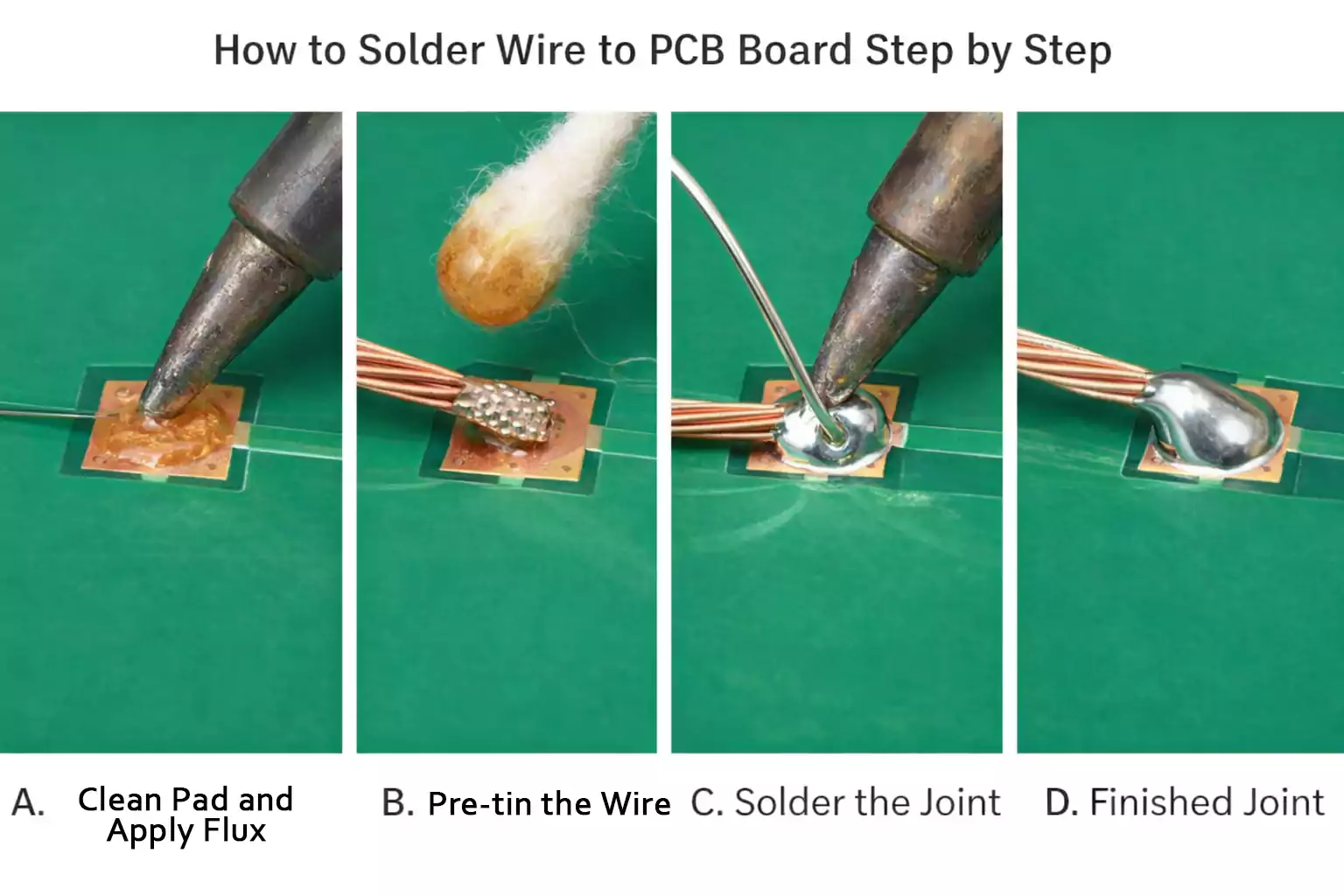

3) قابلية التصنيع والالتزام بالقواعد

- التأكد من الالتزام بعرض/مسافات المسارات

- التحقق من مسافات قناع اللحام (Solder Mask Clearances)

- التأكد من عدم كشف أو تغطية البادات بالخطأ

- التأكد من أن تراكيب الممانعة قابلة للتصنيع

هنا تُمنع كثير من مشاكل “نجح في CAD” من التحول إلى “فشل عند البناء”.

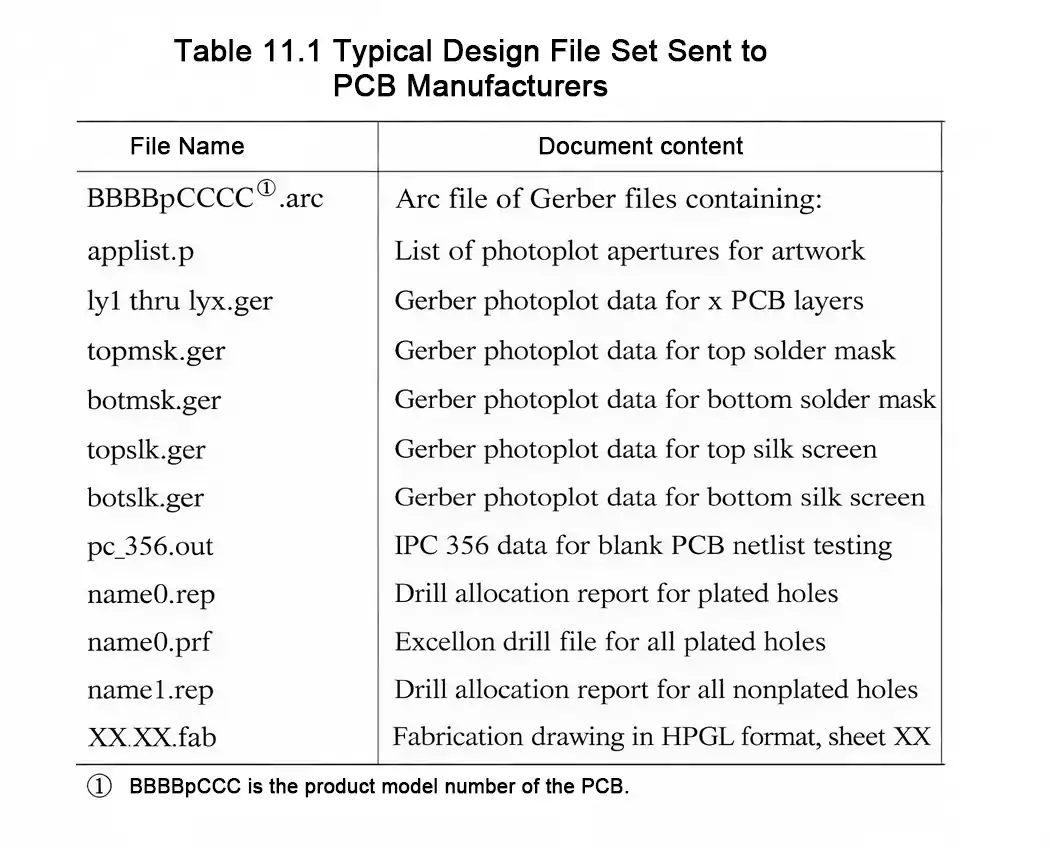

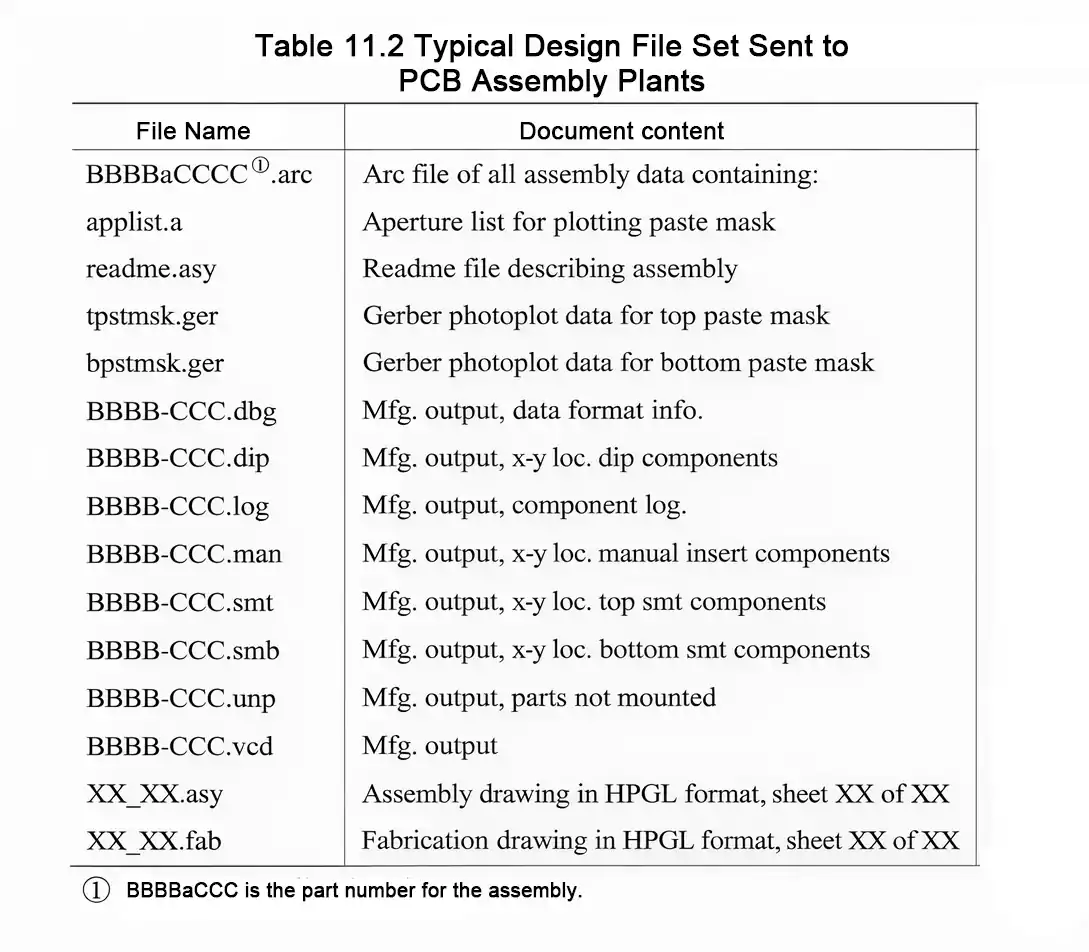

ملفات تصنيع PCB: من قاعدة بيانات التصميم إلى حزمة إنتاج جاهزة

بعد اكتمال التحقق، ينتقل تدفّق تصميم PCB إلى مرحلة إصدار التصنيع. غالبًا ما تشمل حزمة الإصدار:

- ملفات التصنيع (Gerber أو ODB++)

- ملفات الحفر (Drill Files)

- بيانات الالتقاط والوضع (Pick-and-Place)

- رسومات التجميع (Assembly Drawings)

- بيانات اختبار اللوحة العارية (حسب الحاجة)

- وثائق اختبار وظيفي (حسب الحاجة)

- قائمة مواد BOM مكتملة ومراجعة

هذه ملفات تصنيع PCB هي ما يستخدمه المصنعون وورش التجميع فعليًا. أي غموض هنا يؤدي إلى تأخير، وزيادة مخاطر الهدر، وانخفاض العائد (Yield). في مشاريع B2B، ترتبط وضوح هذه الملفات واكتمالها مباشرة بوقت التسليم، والتكرارية، وقابلية التوسع.

أرشفة التصميم: حماية أصل تصميم PCB عالي السرعة

الخطوة الأخيرة هي الأرشفة المنظمة.

الأرشفة ليست مجرد نسخ احتياطي، بل تدعم:

- التعديلات المستقبلية وأوامر التغيير (ECOs)

- التحقيق في أعطال الحقل (Field Failures)

- تتبع الإصدارات (Traceability)

- إدارة دورة حياة المنتج

يجب أن تتضمن الأرشفة الكاملة: قاعدة البيانات الأصلية، مخرجات التصنيع، وثائق الاختبار، سجل الإصدارات، والملاحظات الهندسية. عدم القدرة على إعادة إنتاج التصميم لاحقًا يتحول إلى خطر تجاري وليس مجرد إزعاج.

خلاصة: تصميم PCB عالي السرعة يعتمد على تدفّق تصميم منضبط

النصف الثاني من تدفّق تصميم PCB هو ما يحدد إن كان تصميم PCB عالي السرعة سيصل إلى الإنتاج بسلاسة أم سيدخل في حلقة تصحيح مكلفة.

عندما تُنفّذ قيود التوجيه وتحليل التوقيت وتحليل قابلية التوجيه وتوجيه PCB عالي السرعة بشكل مترابط—ويتم التحقق منها باستخدام بيانات فيزيائية حقيقية—تكون النتيجة لوحة:

- تُصنَّع باستقرار

- تُجمَّع بثبات

- تجتاز الاختبارات بكفاءة

- تتوسع للإنتاج الكمي

- تدعم الصيانة طويلة المدى

وهذا هو الفرق بين لوحة تعمل في المختبر ومنتج يُشحن بثقة في السوق.