После того как выполнены системные требования, функциональное разбиение, моделирование и размещение компонентов (placement), работа по высокоскоростному дизайну PCB входит в наиболее критическую фазу.

На этом этапе цель уже не в том, чтобы просто доказать работоспособность схемы. Цель — убедиться, что физический дизайн выдержит реальные крутизны фронтов (edge rates), плотность трассировки, ограничения производства и повторяемость в серии. Иными словами, именно здесь поток проектирования PCB (PCB design flow) переходит от проектного замысла к реально производимому изделию.

Этот материал охватывает вторую половину PCB design flow для high-speed PCB design и фокусируется на high-speed PCB routing, целостности сигнала (PCB signal integrity), временном анализе (PCB timing analysis), ограничениях трассировки (PCB routing constraints), анализе трассируемости (PCB routability analysis) и выпуске полного комплекта производственных файлов PCB (PCB manufacturing files).

Ограничения трассировки: целостность сигнала начинается до high-speed PCB routing

В низкоскоростных проектах зачастую достаточно логической связности. В высокоскоростном дизайне PCB — нет.

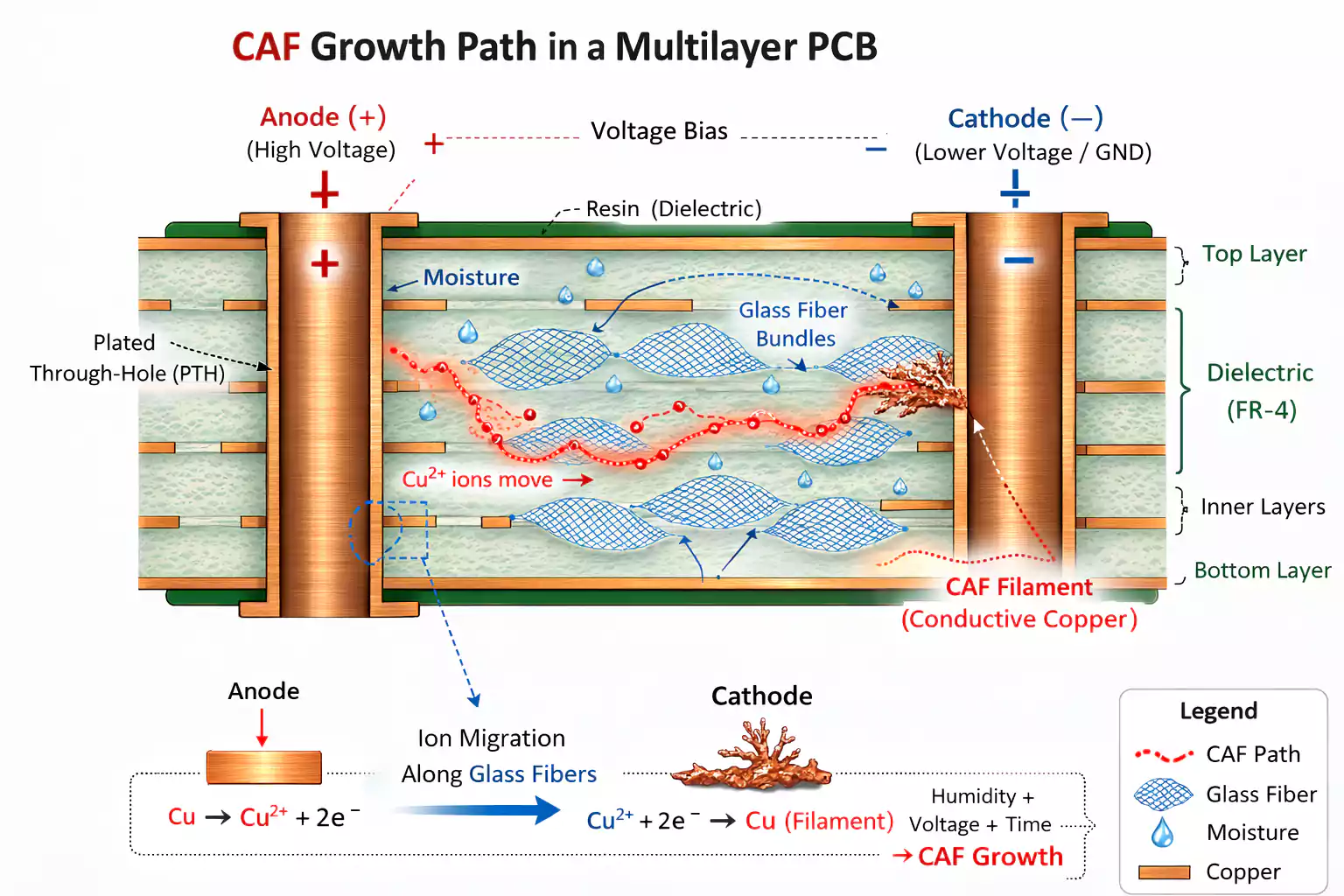

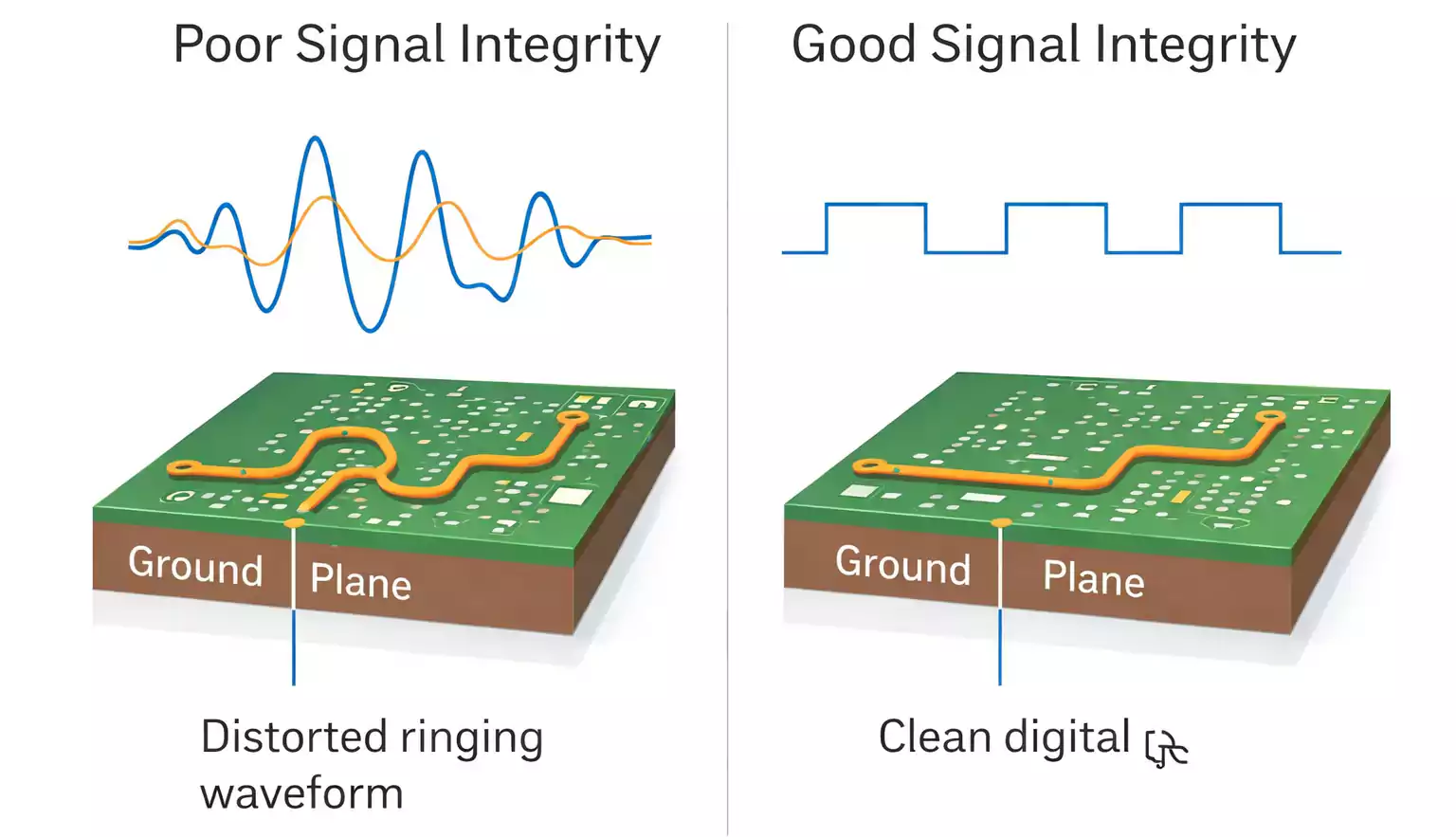

По мере роста крутизны фронтов и значимости задержек межсоединений (interconnect delays) дорожки начинают вести себя как линии передачи. Геометрия layout’а напрямую влияет на целостность сигнала. Типичные проблемы:

- Отражения (reflections)

- Перекрёстные наводки (crosstalk)

- Звон/колебания (ringing)

- Overshoot и undershoot

- Ложные переключения / ошибки порогов (false switching / threshold errors)

Поэтому ограничения трассировки нужно задавать и проверять сразу после размещения (placement) — до детальной высокоскоростной трассировки.

К ключевым ограничениям обычно относятся:

- Топология driver-to-load

- Стратегия и размещение терминаторов (termination)

- Порядок узлов вдоль сети (node ordering)

- Контроль длины и пределы skew

- Согласованность импеданса (single-ended и differential)

Цель — предсказуемое поведение линии передачи до того, как «зафиксирован» медный рисунок. В высокоскоростных бэкплейнах и вычислительных платформах эти ограничения критичны: небольшие физические решения способны привести к серьёзной нестабильности.

Временной анализ и моделирование линий передачи: прогноз до трассировки

Когда размещение стабилизировано, известны физические позиции и примерные коридоры трассировки. Ещё до детальной трассировки это позволяет выполнить ранний PCB timing analysis и моделирование линий передачи на основе:

- Оценочных длин и времён пролёта (flight times)

- Предположений по топологии (point-to-point vs multi-drop)

- Ранних признаков риска отражений и искажений фронтов

Так как координаты узлов и порядок соединений уже определены, можно смоделировать вероятное поведение и выявить проблемы по запасу времени, пока изменения ещё несложны.

Смысл прост: исправлять проблемы PCB signal integrity после трассировки дорого; выявлять их до high-speed PCB routing — эффективно и контролируемо. Для зрелых команд по высокоскоростному дизайну раннее моделирование тайминга и межсоединений — стандартный шаг снижения рисков в PCB design flow.

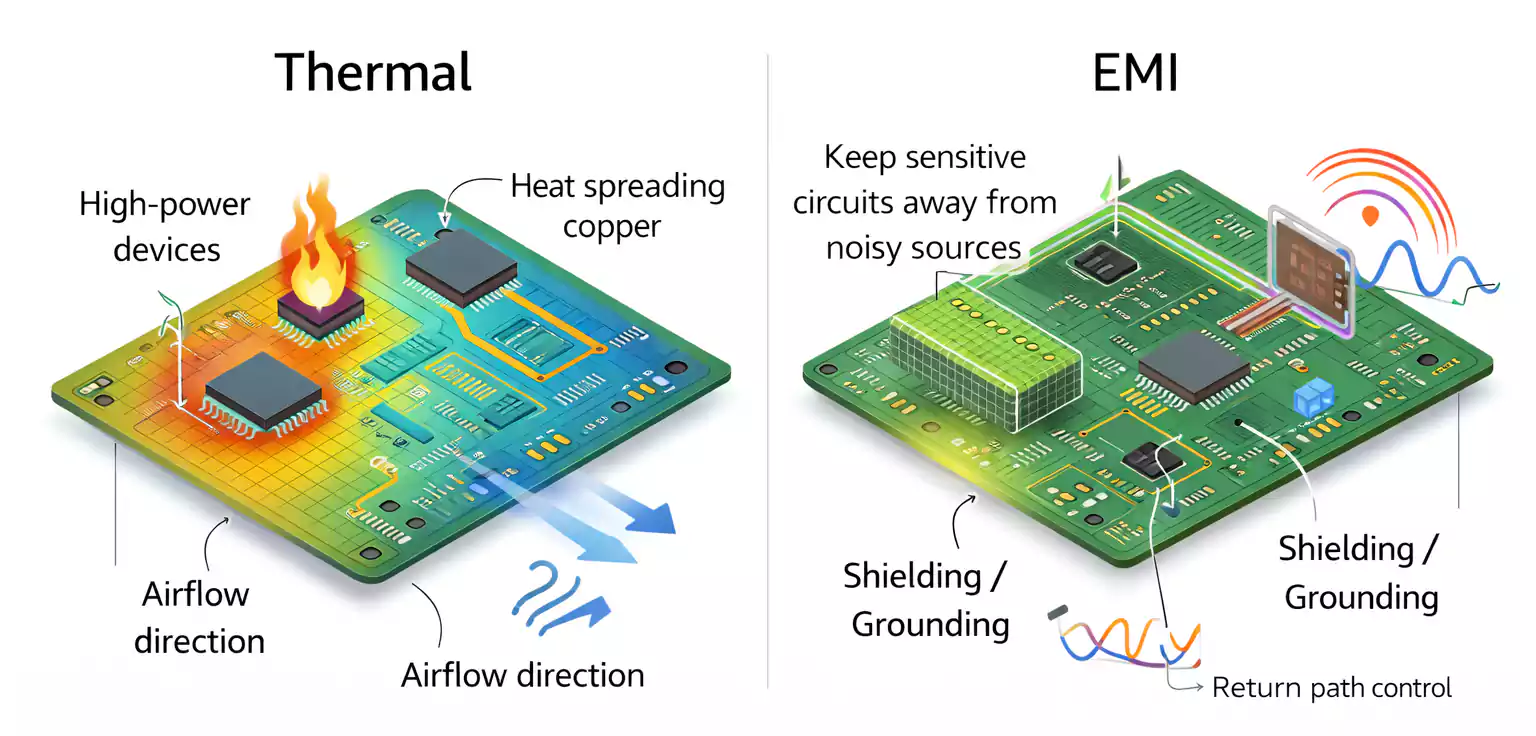

Шум в целостности сигнала: внутренний шум и внешние помехи

Не весь шум имеет одну и ту же природу, и одинаковый подход ко всем шумовым проблемам приводит к неэффективной компенсации. Более корректно в рамках PCB signal integrity разделять шум на две категории.

1) Внутренний шум системы (intrinsic)

Сюда относятся:

- Тепловой шум (thermal noise)

- Коммутационный шум (switching noise)

- Внутренний шум сигнала (intrinsic signal noise)

Внутренний шум — часть нормального поведения схемы. Его нельзя полностью устранить, но можно управлять им, повышая SNR и контролируя физическую реализацию: пути возврата (return paths), развязку (decoupling), управление крутизной фронтов (edge-rate management).

2) Внешние помехи (coupled / environmental)

Внешний шум возникает вне непосредственной схемы и особенно опасен в чувствительных аналоговых, RF-близких и смешанных (mixed-signal) областях.

Типичные меры:

- Экранирование (shielding)

- Улучшение стратегии заземления (grounding)

- Физическая изоляция чувствительных блоков

- Фильтрующие цепи (filter networks)

- Контролируемое проектирование интерфейсов (controlled interface design)

Понимание того, внутренний это шум или внешний, помогает выбрать правильное решение и ускоряет отладку.

Если timing или SI не проходят: пересмотрите размещение и топологию (до трассировки)

Если раннее моделирование показывает:

- Чрезмерные задержки

- Недостаточный запас по таймингу

- Значимые отражения

- Искажения фронтов или ringing

Правильная реакция — не «протрассируем и посмотрим». В high-speed PCB design это момент для корректировки размещения и топологии.

Типичные действия:

- Сближение критических компонентов

- Укорачивание приоритетных сигнальных путей

- Пересмотр топологии (point-to-point vs multi-drop)

- Добавление/удаление/перенос терминаторов

- Корректировка stackup для поддержки ограничений

В цифровых системах класса GHz — особенно на физически больших платах — длина трасс и топология напрямую влияют на глобальный тайминг. Итерации на этой стадии повышают вероятность успеха с первого запуска и предотвращают дорогостоящие поздние перетрассировки.

Анализ трассируемости (routability): убедитесь, что плату реально можно протрассировать

Многие проекты «падают» не из-за электрических ошибок, а из-за недооценённых ресурсов трассировки. Поэтому PCB routability analysis нужно выполнять до детальной трассировки.

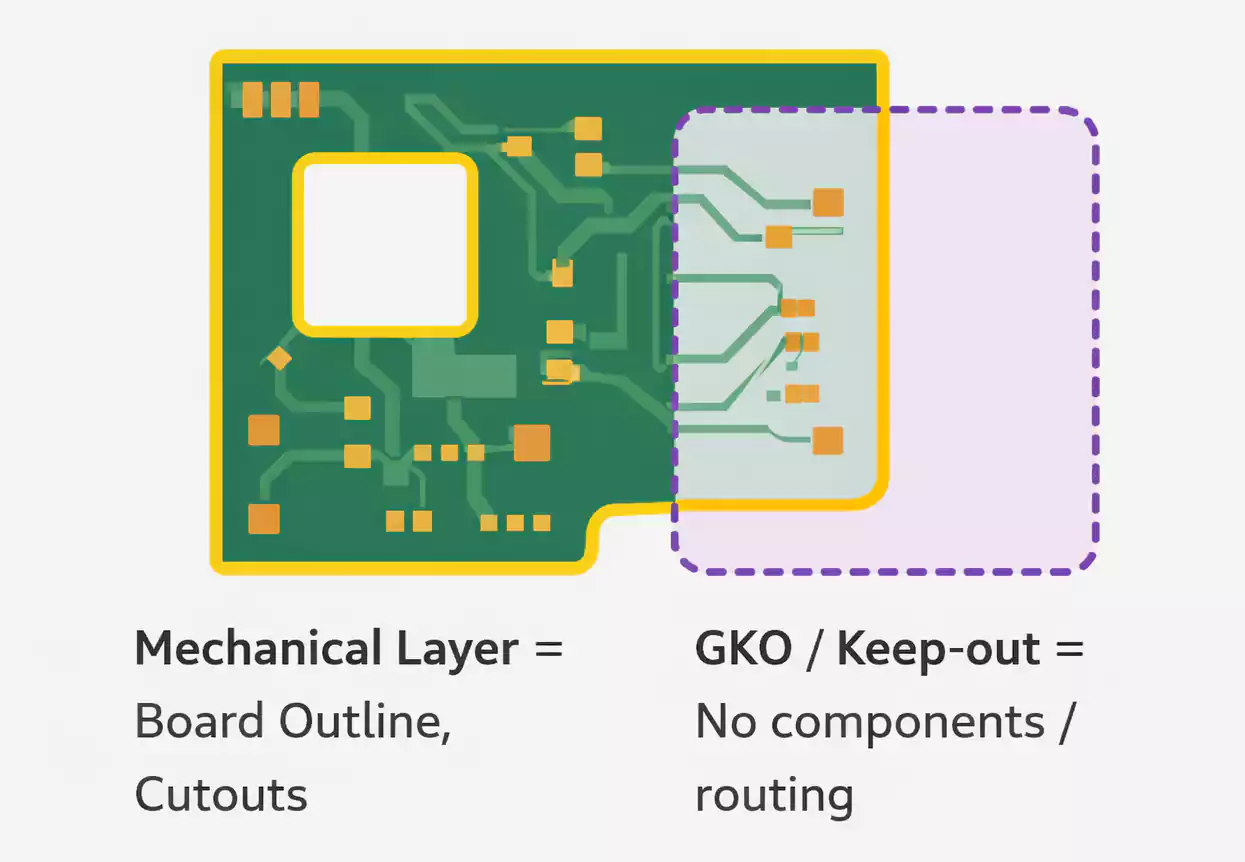

Проверки трассируемости должны отвечать на вопросы:

- Достаточно ли сигнальных слоёв?

- Реалистичны ли расстояния при размещении для ожидаемого fanout?

- Где зоны перегрузки (congestion hot spots)?

- Заблокированы ли критические каналы механикой или keepout-областями?

- Поддерживает ли floorplan выбранный stackup и via-стратегию?

Современные EDA-инструменты дают метрики перегрузки и проверку feasibility. Если трассируемость слабая, правильнее обычно пересмотреть размещение/слои, а не «продавить» компромиссную трассировку.

Эта стадия особенно важна для плотных многослойных плат и mixed-signal-layout’ов, где PCB routing constraints сокращают доступную трассировочную площадь.

High-speed PCB routing: работать в рамках ограничений, а не против них

Когда placement, PCB timing analysis и PCB routability analysis в порядке, начинается детальная high-speed PCB routing.

Трассировка должна соответствовать ранее заданным ограничениям, включая:

- Правила ширины и расстояний между дорожками

- Согласование длин и контроль skew

- Требования по импедансу

- Сцепление и симметрия дифференциальных пар

- Непрерывность пути возврата (return path continuity)

- Ограничения по crosstalk и классы расстояний

На практике сильные команды обычно используют:

- Ручную трассировку для критичных высокоскоростных сетей

- Контролируемую трассировку путей распределения питания

- Автотрассировку для некритичных сигналов

- Post-route очистку и оптимизацию

Routing-«playbook» — политика слоёв, правила via, приоритеты классов сетей и критерии ревью — повышает консистентность и снижает число циклов проверок в командных проектах.

Проверка после трассировки: замкнуть контур по SI, timing и связности

Завершение трассировки не означает завершения проекта: теперь реальные длины и геометрии требуют повторной валидации.

Post-route проверки обычно включают:

1) Повторная проверка PCB signal integrity и PCB timing analysis

- Подтверждение запасов по таймингу по реальным длинам

- Повторная оценка отражений и качества фронтов

- Анализ рисков наводок между aggressor/victim-сетями

2) Проверка netlist / связности

- Убедиться, что не появилось непреднамеренных изменений связности

- Проверить, что при правках не внесены opens/shorts

3) Производимость и соответствие правилам

- Соответствие ширины/зазоров

- Проверка зазоров solder mask

- Убедиться, что пэды не оголены или не закрыты ошибочно

- Проверить, что импедансные структуры технологичны

Именно здесь многие проблемы «в CAD работало» предотвращаются до того, как превратятся в «на сборке не взлетело».

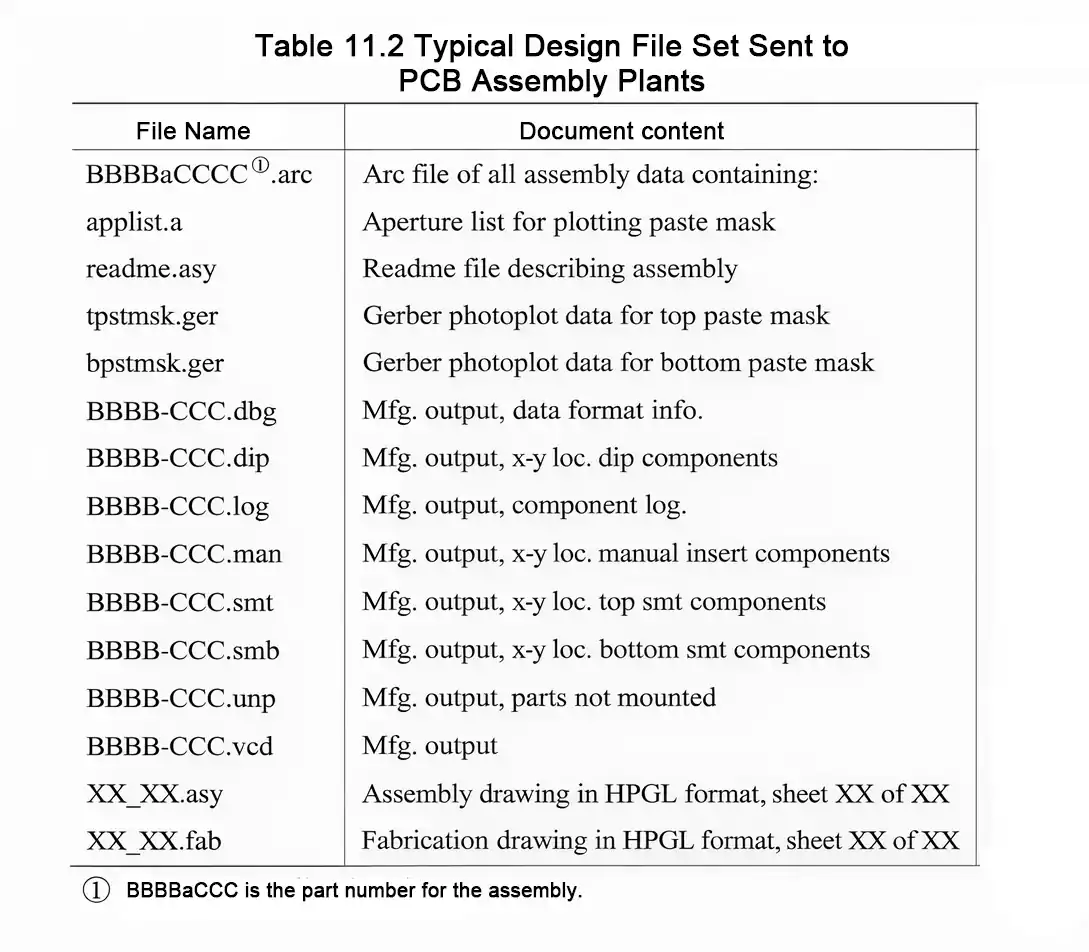

Производственные файлы PCB: от базы данных проекта к релизу в производство

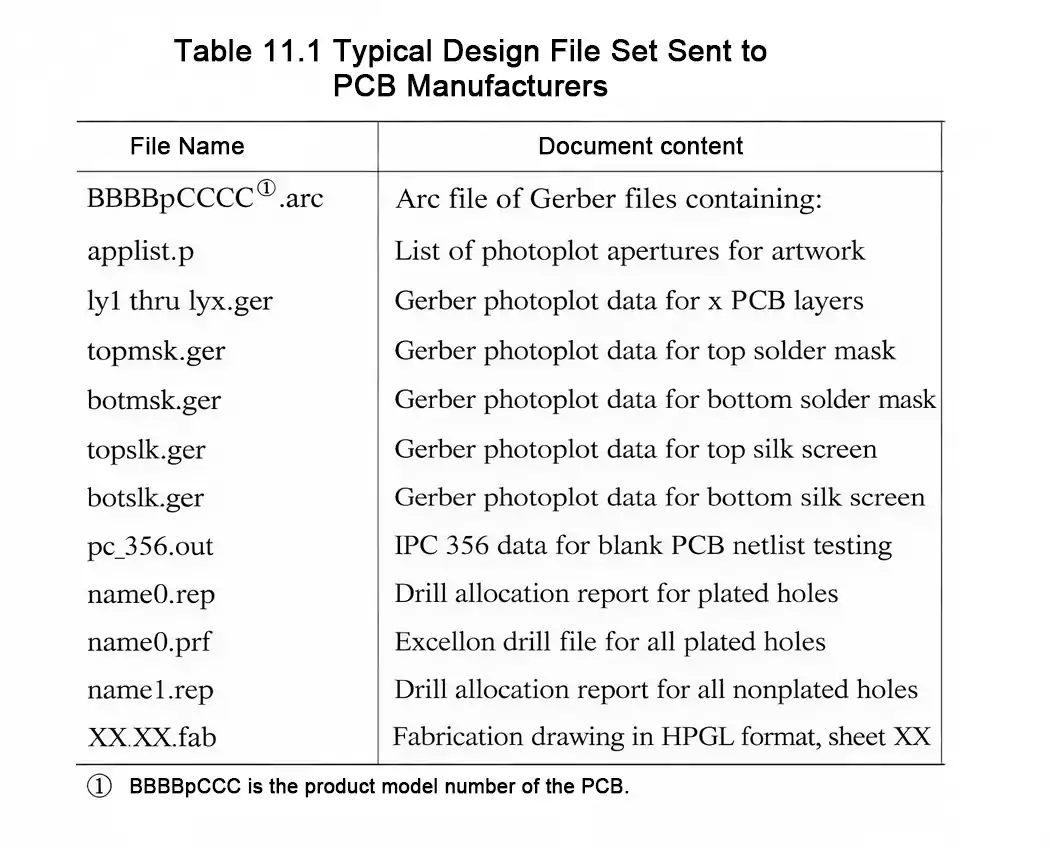

После завершения проверок PCB design flow переходит к manufacturing release. Полный пакет обычно включает:

- Файлы для производства (Gerber или ODB++)

- Drill-файлы

- Данные pick-and-place

- Сборочные чертежи (assembly drawings)

- Данные теста голой платы (при необходимости)

- Документацию функциональных тестов (при необходимости)

- Полную, проверенную BOM

Эти PCB manufacturing files — то, чем реально пользуются фабрика и сборка. Любая неоднозначность приводит к задержкам, риску брака и падению выхода годных. Для B2B-оборудования ясность и полнота файлов напрямую связаны со сроками, повторяемостью и масштабированием производства.

Архивация: защита актива high-speed PCB design

Последний шаг — структурированная архивация.

Архивирование — это не просто backup. Оно поддерживает:

- Будущие ревизии и ECO

- Расследование полевых отказов (field failure investigation)

- Прослеживаемость версий (version traceability)

- Управление жизненным циклом (lifecycle management)

Полный архив должен включать исходную базу проекта, производственные выходы, тестовую документацию, историю ревизий и инженерные заметки. Невозможность воспроизвести дизайн позже становится бизнес-риском, а не просто неудобством.

Итог: high-speed PCB design требует дисциплинированного PCB design flow

Вторая половина PCB design flow определяет, выйдет ли высокоскоростной PCB-дизайн в производство гладко или попадёт в дорогую петлю отладки.

Когда PCB routing constraints, PCB timing analysis, PCB routability analysis и дисциплинированное high-speed PCB routing выполняются как связанный процесс — и подтверждаются реальными физическими данными — получается плата, которая:

- Производится стабильно

- Надёжно собирается

- Эффективно проходит тестирование

- Масштабируется в серию

- Поддерживается в долгосрочной эксплуатации

Это и есть разница между платой, которая работает в лаборатории, и продуктом, который надёжно поставляется на рынок.