מבוא: למה תהליך שיטתי הוא קריטי

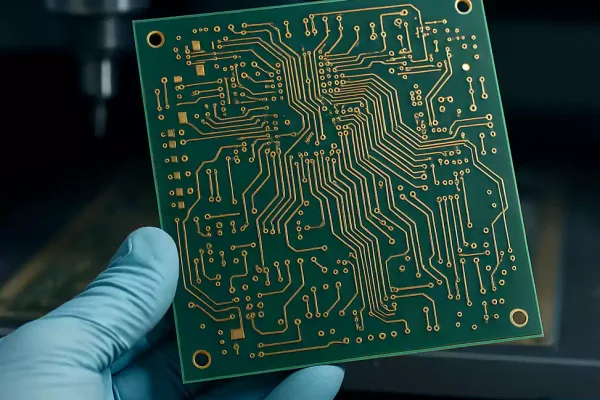

כאשר אנשים מחפשים "tecnograph process PCB", הם למעשה מחפשים תיאור ברור ומלא של איך לוח חשוף הופך לבסיס אמין להרכבה אלקטרונית. ביצוע נכון של התהליך מפחית סבבי פרוטוטייפ מיותרים, מייצב זמני אספקה ומונע הפתעות בבדיקת הקבלה. מדריך זה מציג את זרימת הייצור המודרנית של לוחות מודפסים—מסביר כל שלב, מדוע הוא חשוב, אילו נתונים דרושים ומהן הטולרנציות הקריטיות להצלחה כבר מהפעם הראשונה.

התוכן מיועד למהנדסי פיתוח, מנהלי רכש וסטארטאפים שזקוקים להבנה פרקטית ללא מונחים מסובכים.

סקירת תהליך: מהנתונים ועד למשלוח

תהליך Tecnograph PCB בנוי מרצף קבוע וברור:

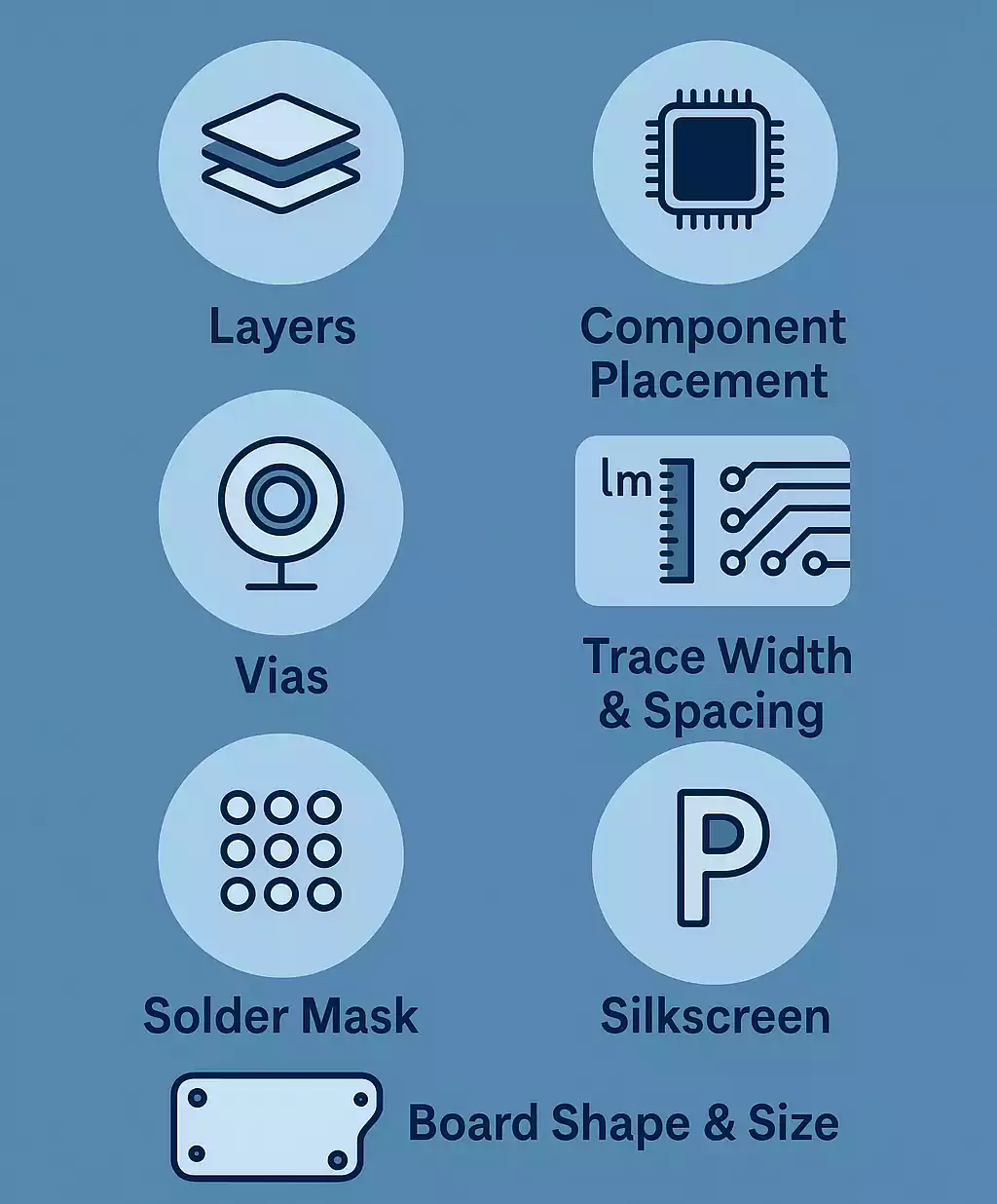

CAM & DFM → הדמיית שכבות פנימיות וחריטה → למינציה → קידוח (מכני/לייזר) → ציפוי נחושת (PTH) → תבנית שכבות חיצוניות וחריטה → מסיכת הלחמה (Solder Mask) → סילקסקרין/סימון → ציפוי שטח → בדיקות חשמליות וביקורת → חיתוך, ניקוי ואריזה

שני גורמים מחזיקים את כל התהליך הזה ביחד:

- נתוני ייצור ברורים וחד‑משמעיים

- הסכמה מראש על מטרות ייצור: רוחב/רווח מסילות, אסטרטגיית ויא, אימפדנס וגימור שטח

כאשר הדברים האלו מוגדרים מראש, שאר השלבים הופכים ליציבים וניתנים לניהול מדויק.

הנדסת Front‑End: CAM ו‑DFM שמאושרים בפעם הראשונה

הנדסת ה‑Front‑End ממירה את קבצי התכנון ללוח בר‑ייצור.

נתונים ופורמטים:

Gerber X2, ODB++ או IPC‑2581. יש לצרף: מבנה שכבות ברור, נתוני חומר, תקציר קידוחים, מטרות אימפדנס עם טולרנציות, וקובץ Netlist לבדיקה. אם נדרשת הרכבה—להוסיף קובץ Centroid ו‑BOM.

פאנליזציה:

פאנליזציה נכונה משפרת תשואה ויכולת ייצור. מומלץ להוסיף: פסי אחיזה, Fiducials כלליים, אזורי קופונים, ואסטרטגיית חיתוך (V‑Scoring או טאבים). עבור לוחות עם אימפדנס מבוקר—קופוני בדיקה חובה.

טולרנציות קריטיות:

התאם רוחב/רווח מינימלי למשקל הנחושת; הגדר מרחק נחושת‑לחור בהתאם לסטייה בקידוח; קבע חלון אימפדנס המתאים למבנה השכבות ולציפוי. אם העבודה כוללת HDI, BGA עדין או אימפדנס הדוק—חשוב להדגיש זאת ליצרן מראש.

חומרים ומבנה שכבות (Stack‑Up)

מבנה השכבות הוא ה‑DNA של ה‑PCB. הוא משפיע על אימפדנס, הפסדים, יציבות תרמית ושטיחות הלוח.

חומרי ליבה:

ליישומים דיגיטליים כלליים—נעשה שימוש ב‑FR‑4 מותאם Tg ו‑CTE. ליישומי High‑Speed/RF—נדרשים חומרים בעלי Dk/Df נמוכים. חשוב לציין ערכי Dk/Df בתדר העבודה בפועל.

משקל נחושת:

שכבות חיצוניות מתחילות דקות יותר ונבנות בגלוון; שכבות פנימיות משתמשות בפוילים מגולוונים. נחושת עבה יותר מגדילה זרם ויכולת תרמית אך משפיעה על רישום וחריטה.

סימטריה ומניעת עיוות:

שמור על סימטריה בין שכבות ועל איזון נחושת כדי למנוע כיפוף ועיוות בלמינציה.

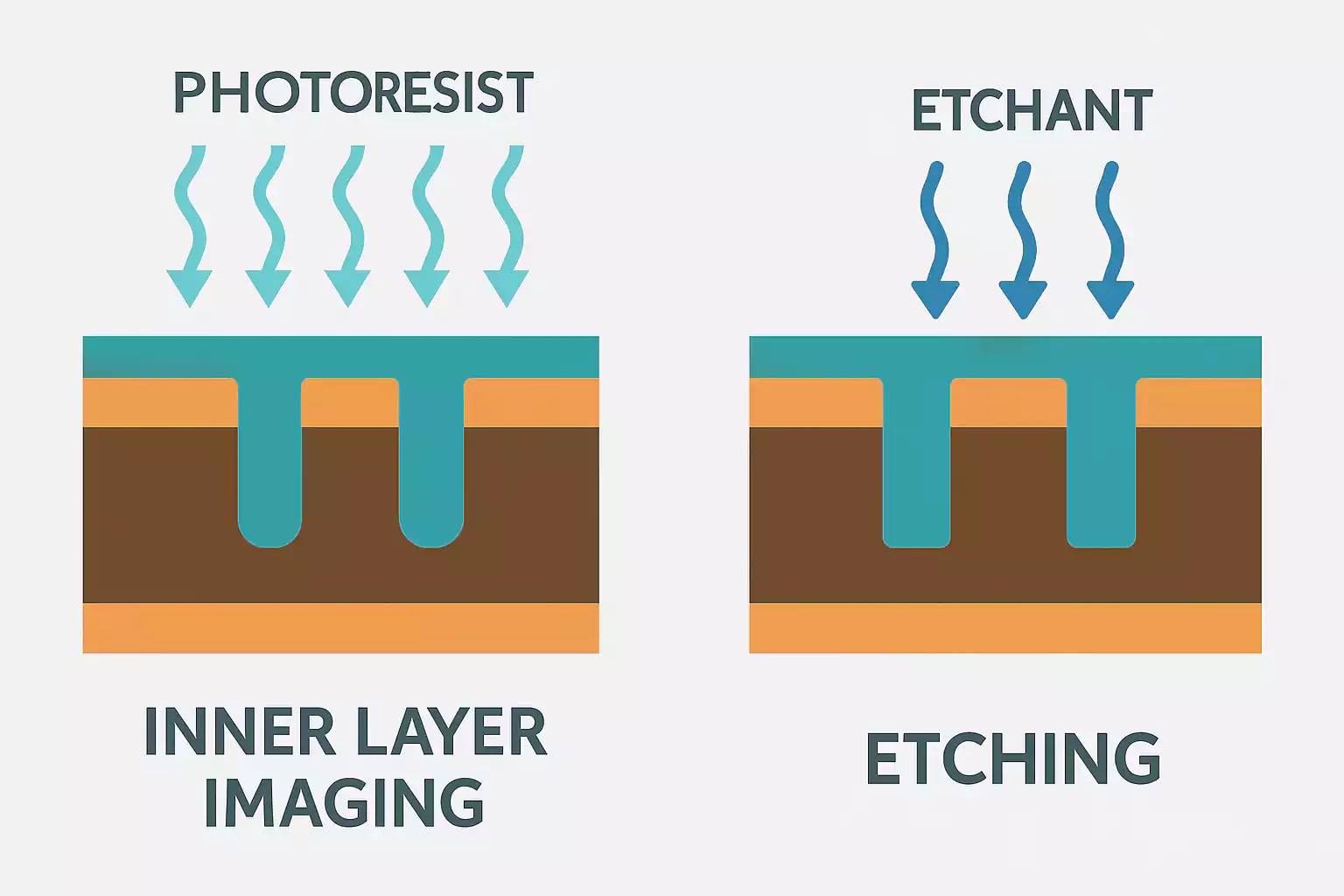

הדמיית שכבות פנימיות וחריטה

השכבות הפנימיות קובעות מסילות וקווי ייחוס עוד לפני הלמינציה.

הדמיה:

כיסוי פוטורזיסט וחשיפה בעזרת LDI לקבלת דיוק מיטבי. לאחר פיתוח מתקבל דפוס הנחושת הרצוי. יש להתייחס לפיצוי של התרחבות/התכווצות בשלב CAM.

חריטה:

הנחושת החשופה נחרטת בקצב שתלוי בטמפרטורה, כימיה ומהירות קו. יש להתחשב ב‑Undercut בצדדים. לאחר מכן AOI מוודא איכות וצורה נכונה.

נקודות סיכון:

חריטת יתר → מסילות דקות מדי ואימפדנס גבוה.

חריטה חסרה → whiskers של נחושת.

כל זיהום עלול להילכד בלמינציה וליצור תקלות עתידיות.

למינציה

למינציה מאחדת את השכבות הפנימיות בעזרת חום ולחץ.

זרימת רזין ומילוי:

הרזין חייב למלא חללים, אריגים, ו‑Vias קבורות. זרימה מוגזמת תזיז תכונות, זרימה חסרה תייצר חללים.

רישום ושטיחות:

מחזורי לחיצה, פינים ו‑Tooling קובעים דיוק יישור בין שכבות. מבנה סימטרי מפחית עיוות. ב‑HDI רב‑שלבי—תכנון סדר יצירת המיקרו‑וויה קריטי.

תכונות תרמיות:

Tg גבוה מונע מעבר פאזה בלחימות. התאמה ב‑CTE בין חומרים מפחיתה עומס על ויאים ופאדים.

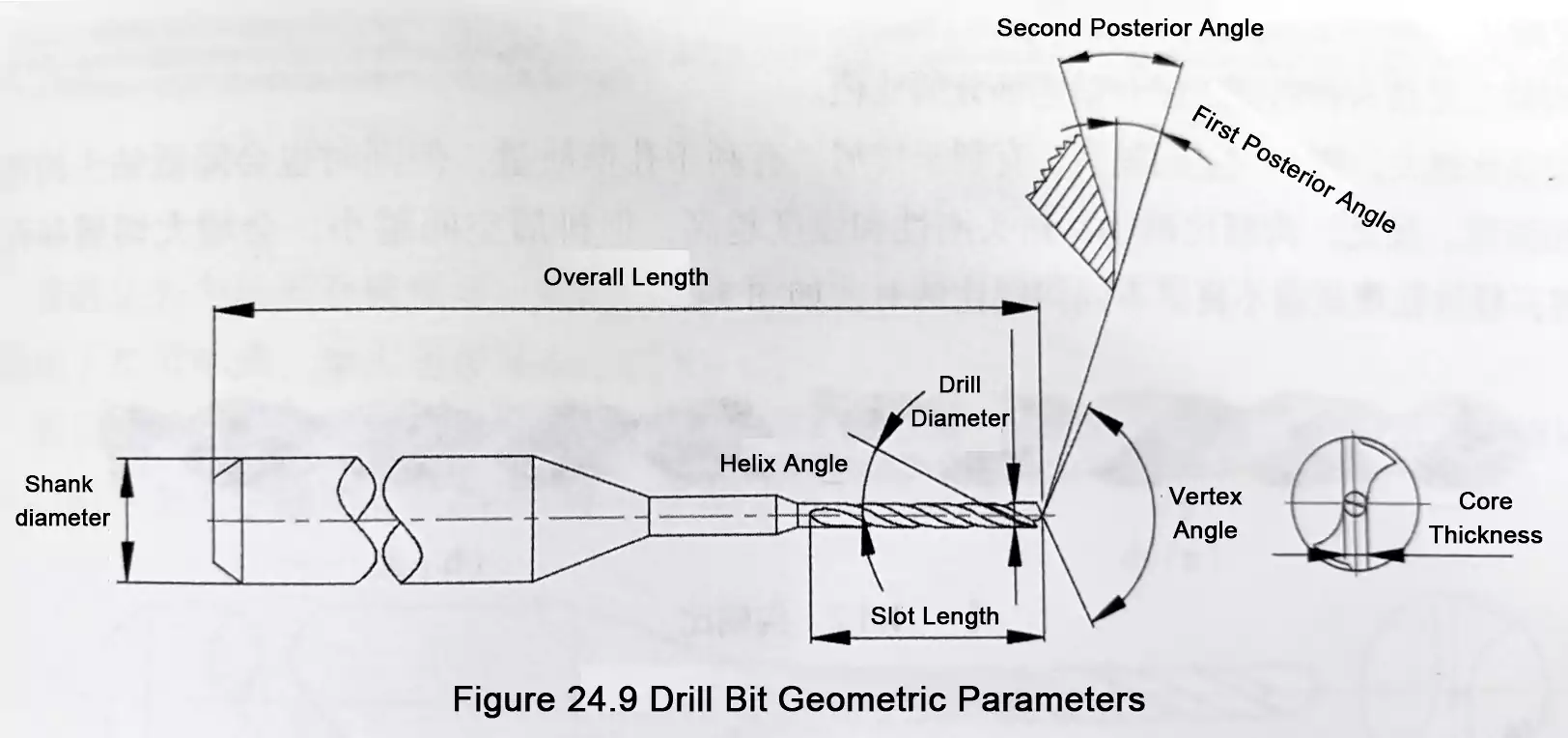

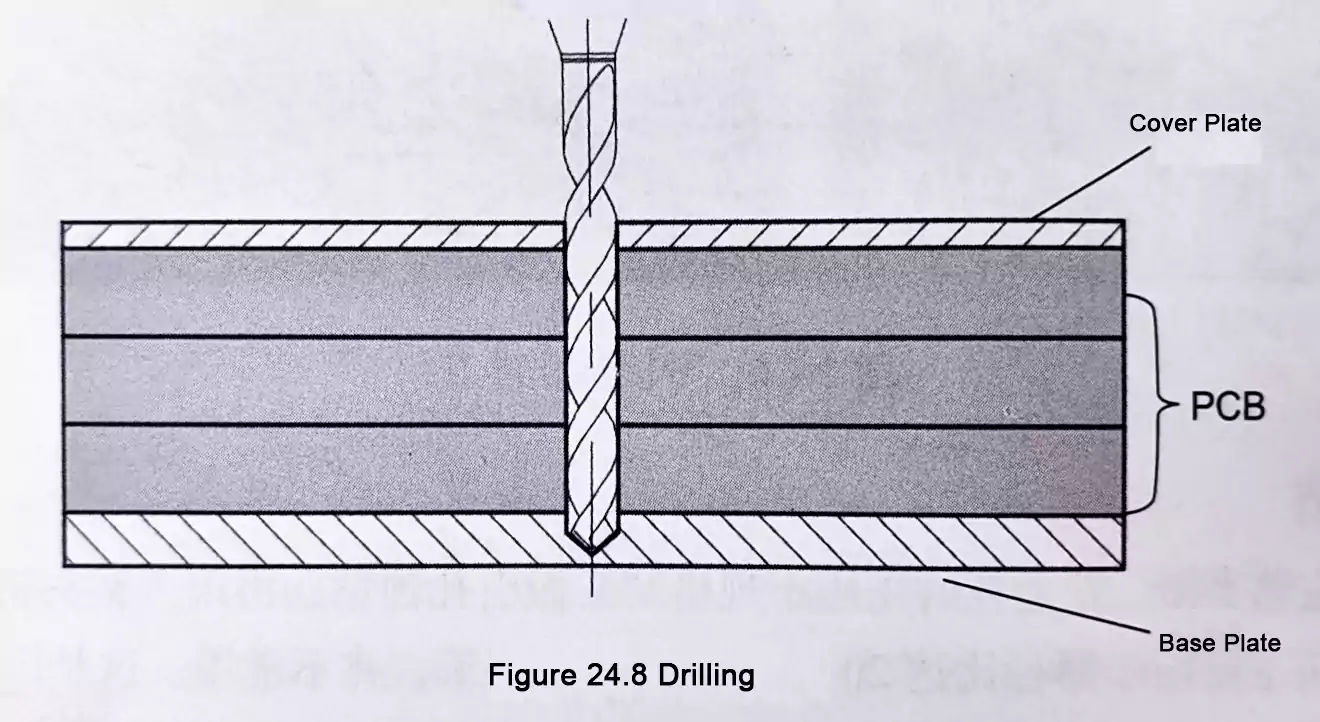

קידוח ואסטרטגיית Vias

סוגי חורים:

- Through‑Hole: אמין וזול

- Blind/Buried Via: מפנה מקום ומאפשר ניתוב צפוף

- Microvia בלייזר (≤ 0.1 מ"מ): חובה עבור BGA צפוף, ניתן לערום או לדרג בהתאם ליכולת היצרן

שליטה בתהליך:

קידוח מכני דורש מהירויות מתאימות למניעת Smear. לייזר דורש אנרגיה מבוקרת שלא פוגעת בנחושת. חשוב לשמור טבעת נחושת (Annular Ring) מספקת.

החלטות תכנון:

Via‑in‑Pad מקצר מסלולים ומשפר SI/PI אך מחייב מילוי נחושת ויישור פני השטח. Cover/Tenting של Vias משפיע על בדיקות וניקיון.

PTH וציפוי נחושת

לאחר הקידוח הדפנות אינן מוליכות. בתהליך PTH הופכות למוליכות.

רצף העבודה:

Desmear → אקטיבציה ב‑Palladium → ציפוי כימי → גלוון בנחושת. במקרים מסוימים—תוספת Plating לפאדים לפני החריטה.

מדדי איכות:

אחידות בעובי הנחושת היא מפתח לאמינות תרמית. נבדק ע"י זרם, ערבוב, איכות האלקטרוליט. חתכי מיקרו (Microsections) מוודאים היעדר חללים או סדקים.

ניהול סיכונים:

Dog‑boning בקצוות פאדים או Nodule‑Growth יכולים לפגוע באימפדנס ובלחימות.

הדמיית שכבות חיצוניות וחריטה

שכבות החוץ דורשות התחשבות בעובי הנחושת המצופה.

הדמיה ו‑Pattern Plating:

Dry Film מגדיר את האזורים שיישארו. ניתן לחזק פאדים מסוימים בגלוון נוסף.

חריטה סופית:

הסרת הנחושת החשופה לקבלת גיאומטריה סופית. פיצוי CAM הכרחי לשמירת מדדי רוחב מסילה ואימפדנס.

תקלות נפוצות:

שאריות, הצטברות נחושת, חריטה חסרה—נתפסים ב‑AOI.

מסיכת הלחמה וסילקסקרין

אסטרטגיית מסיכה:

פתחים סביב פאדים ברוחב הנכון, שמירה על מרווחים בין פאדים צפופים, קביעת טיפול ב‑Vias לפי צורך בבדיקה או תיקון.

רישום וייצוב:

יישור מדויק ומעבר תרמי נכון מבטיחים היצמדות ועמידות.

סימון:

סילקסקרין או לייזר לתיאוג, סימון קוטביות וזיהוי רכיבים. להימנע מדיו על פאדים.

בחירת גימור שטח

| גימור | יתרונות | שיקולים |

|---|---|---|

| HASL / ללא‑עופרת | חזק, זול | לא הכי שטוח |

| OSP | שטוח וזול | חיי מדף קצרים |

| ENIG | שטוח, אמין | דורש בקרת תהליך—Black Pad |

| ENEPIG | מעולה לחיבורי Wire‑Bond | יקר יותר, איכות גבוהה |

| Imm. Tin/Silver | לוח שטוח ולחיץ | רגישות לחמצון ואחסון |

התאם את הגימור לרגישות הרכיבים, דרישות אמינות וזמן האחסון.

בדיקות, ביקורת ו‑DFT

בדיקות חשמליות:

- Flying‑Probe—מהיר וגמיש לניסויים

- Bed‑of‑Nails—יעיל לייצור סדרתי

בדיקות AOI/X‑Ray:

AOI לאימות תבניות, X‑Ray לבדיקת ויאים וקווים קבורים.

תכנון לבדיקות (DFT):

נקודות בדיקה, רווחים למגעי בדיקה, התאמת Netlist. לדרישת אימפדנס—קופוני בדיקה (TDR).

חיתוך, ניקוי ואריזה

חיתוך:

V‑Scoring לקווים ישרים וצפיפות גבוהה; טאבים לצורות מורכבות או הגנה על רכיבים.

ניקוי:

הסרת יונים ופסולת לשיפור הלחימות.

אריזה:

שקיות MBB, סופחי לחות, מדדי לחות, תיוג Lot/Revision—חשוב במיוחד ל‑OSP/כסף.

שלושה תרחישים מעשיים ומה לבחור

פרוטוטייפים וסדרות קטנות:

מהירות וגמישות—בדיקות Flying‑Probe, גימור ENIG/OSP, פאנליזציה פשוטה.

ייצור סדרתי ואופטימיזציית עלויות:

ניצול פאנל גבוה, Fixture‑Test, בחירת גימור לפי זמן‑מחזור: OSP או HASL ללא‑עופרת.

High‑Speed / RF / HDI:

חומרים Low‑Loss, שליטה בחספוס נחושת, אסטרטגיית Microvia ריאלית. קופוני אימפדנס חובה.

סיכום ושלבים הבאים

תהליך Tecnograph PCB מסודר הופך כוונת תכנון לחומרה אמינה: חומרים נכונים, הדמיה וחריטה מבוקרות, ויאים אמינים, גימור מתאים ותוכנית בדיקות מותאמת ליישום.

כאשר הנתונים ברורים והטולרנציות ריאליות—התשואה עולה, זמני הייצור מתקצרים ומתמזערות טעויות יקרות בשלבים המאוחרים.

אם אתם מוכנים לאמת את התכנון או לקבע Stack‑Up, שלחו את קבצי ה‑PCB לבדיקה ולהצעת מחיר מהירה ומדויקת.