מהו HDI PCB?

HDI הוא קיצור של High-Density Interconnect (קישורים בצפיפות גבוהה).

בלוח HDI משתמשים במסלולים דקים, microvias ובשכבות Build-Up מרובות כדי להשיג צפיפות חיווט גבוהה יותר מאשר בלוחות מרובי-שכבות רגילים.

לפי IPC-2226, לוח HDI כולל בדרך-כלל:

- רוחב/מרווח מוליך קטן מ-100 µm (≈ 4 mil)

- Microvias קטנים מ-150 µm (≈ 6 mil)

- יותר מ-20 Pads לסמ״ר של שטח הלוח

בפשטות: טכנולוגיית HDI מאפשרת יותר רכיבים בשטח קטן, מסלולים קצרים יותר וביצועים חשמליים טובים יותר—מתאים במיוחד לסמארטפונים, לבישים, רדאר רכב ומכשור רפואי.

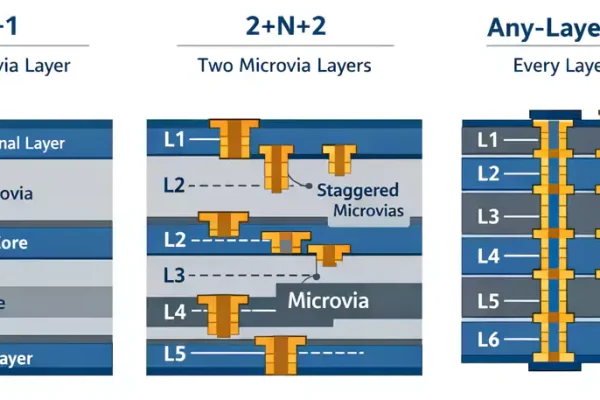

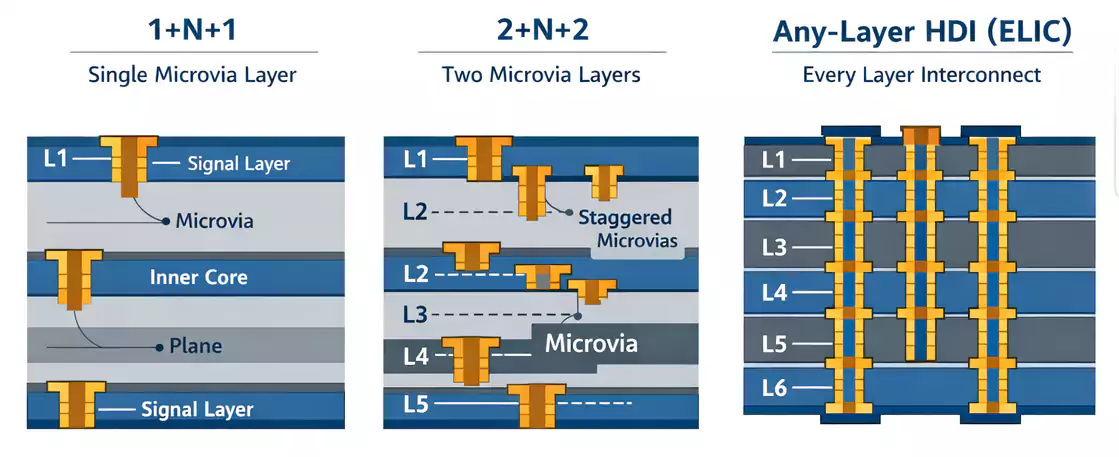

סוגי מבנה HDI

מבנה HDI מוגדר לפי מספר שכבות המיקרו-ויה שנבנות מעל ה-Core.

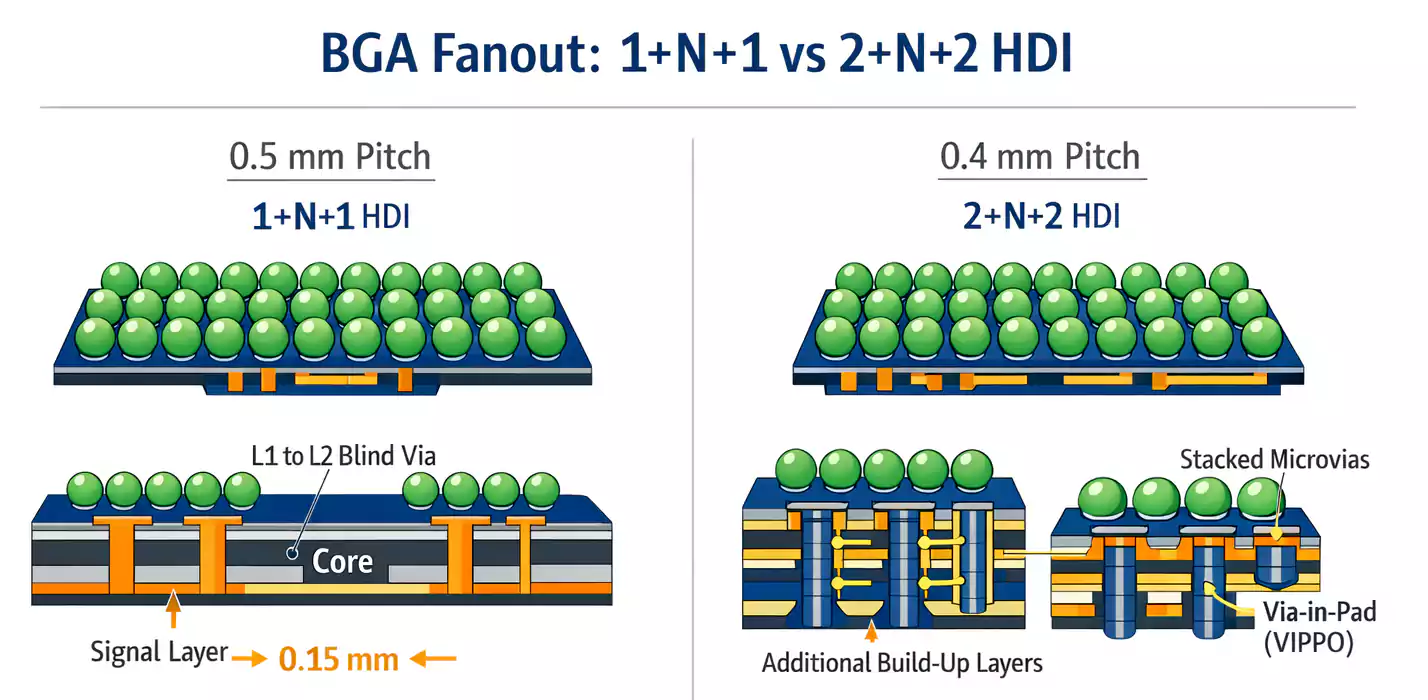

- Type I (1+N+1): שכבת microvia אחת בכל צד של ה-Core. שימוש טיפוסי: סמארטפונים ולוחות IoT.

- Type II (2+N+2): שתי שכבות microvia מוערמות בכל צד. שימוש: Fan-out צפוף של BGA.

- Type III / ELIC (Any-Layer): microvias מוערמות בין כל השכבות. שימוש: שבבים עם מספר פינים גבוה מאוד.

Microvias מוערמות (Stacked) מיושרות שכבה-מעל-שכבה; מדורגות (Staggered) מוזחות בין השכבות. מדורגות קלות וזולות יותר לייצור; מוערמות חוסכות מקום אך דורשות ציפוי נחושת חזק יותר ובקרה קפדנית.

Stack-ups נפוצים ובקרת אימפדנס

- 1+N+1: שכבת microvia אחת למעלה ואחת למטה, מחוברות ל-Core סטנדרטי.

- 2+N+2: תוספת שכבת Build-Up נוספת בכל צד.

- Any-Layer (ELIC): קישור בין כל השכבות באמצעות microvias מוערמות לחופש תכן מלא.

כיוון שב-HDI משתמשים בדיאלקטריים דקים, בקרת האימפדנס קריטית. נהוג לצמד שכבות אות לשכבות ייחוס (GND/PGND) צמודות כדי לשמור על אימפדנס מבוקר לאותות מהירים (PCIe, SerDes וכו׳).

תכן Microvia ו-Via-in-Pad

Microvias הם חורים עיוורים זעירים (טיפוסית < 0.1 מ״מ) המחברים שכבות סמוכות בלבד (למשל L1→L2).

סוגי ויה עיקריים ב-HDI:

- Blind Via: מהשכבה החיצונית לפנימית.

- Buried Via: בין שכבות פנימיות בלבד.

- Via-in-Pad (VIP/VIPPO): הויה יושבת בתוך ה-Pad לחיסכון במקום.

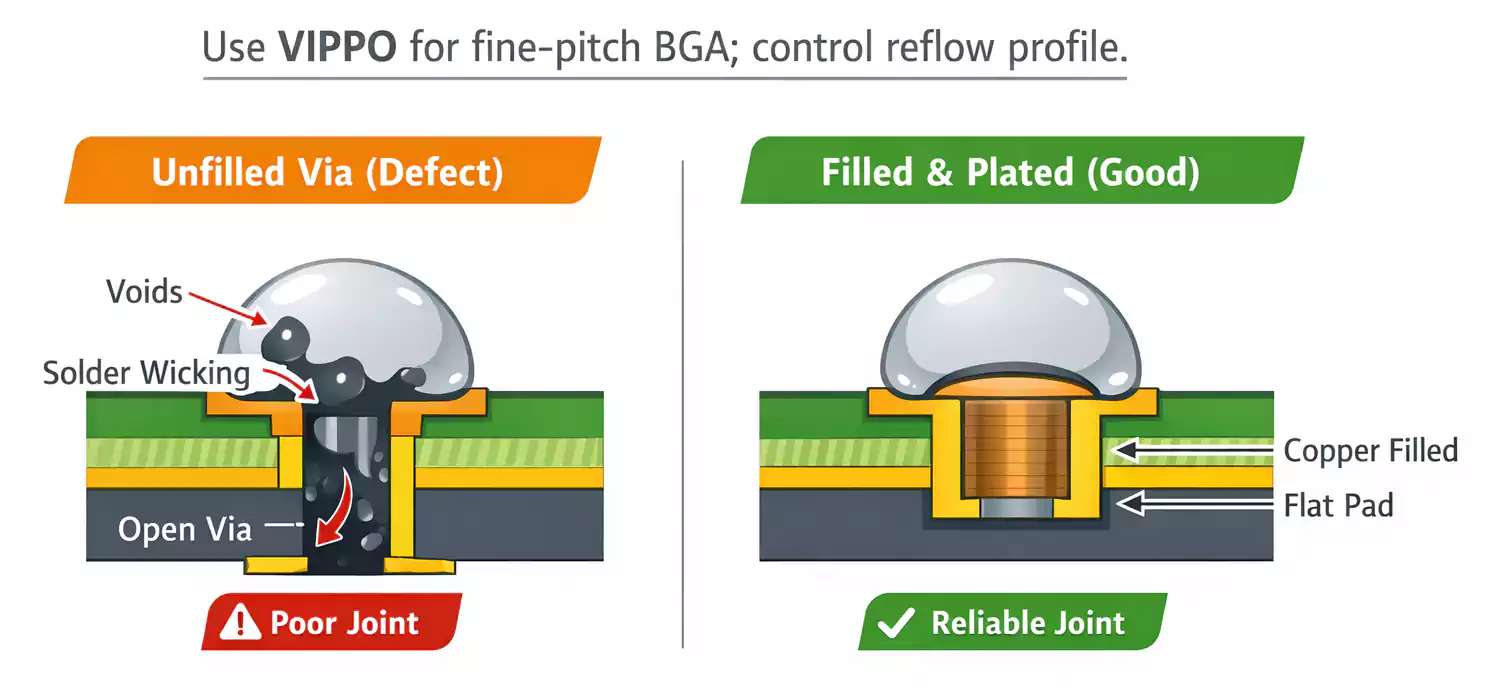

VIP נפוץ ב-BGA עם פיץ׳ ≤ 0.4 מ״מ. ממלאים בנחושת/אפוקסי ומצפים עד פני-שטח שטוחים לקבלת הלחמה חלקה.

דגשים למתכננים:

- ויות לא ממולאות עלולות ליצור משיכת בדיל בזמן Reflow.

- ערימות microvia רבות מדי מעלות סיכון לסדקי ציפוי במחזורי חום.

סקירת תהליך ייצור HDI

הבנייה מתבצעת בשלבים – Sequential Build-Up (SBU):

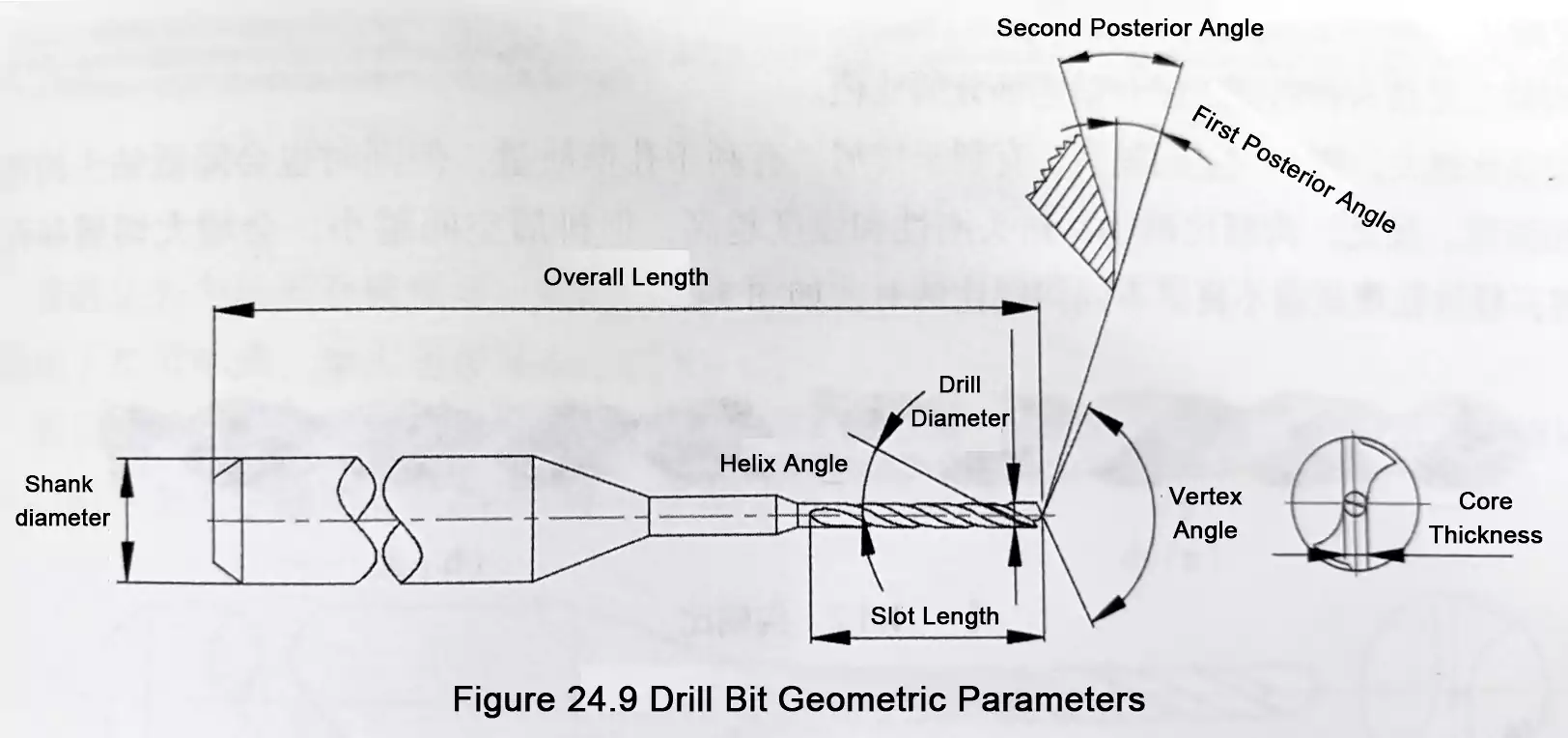

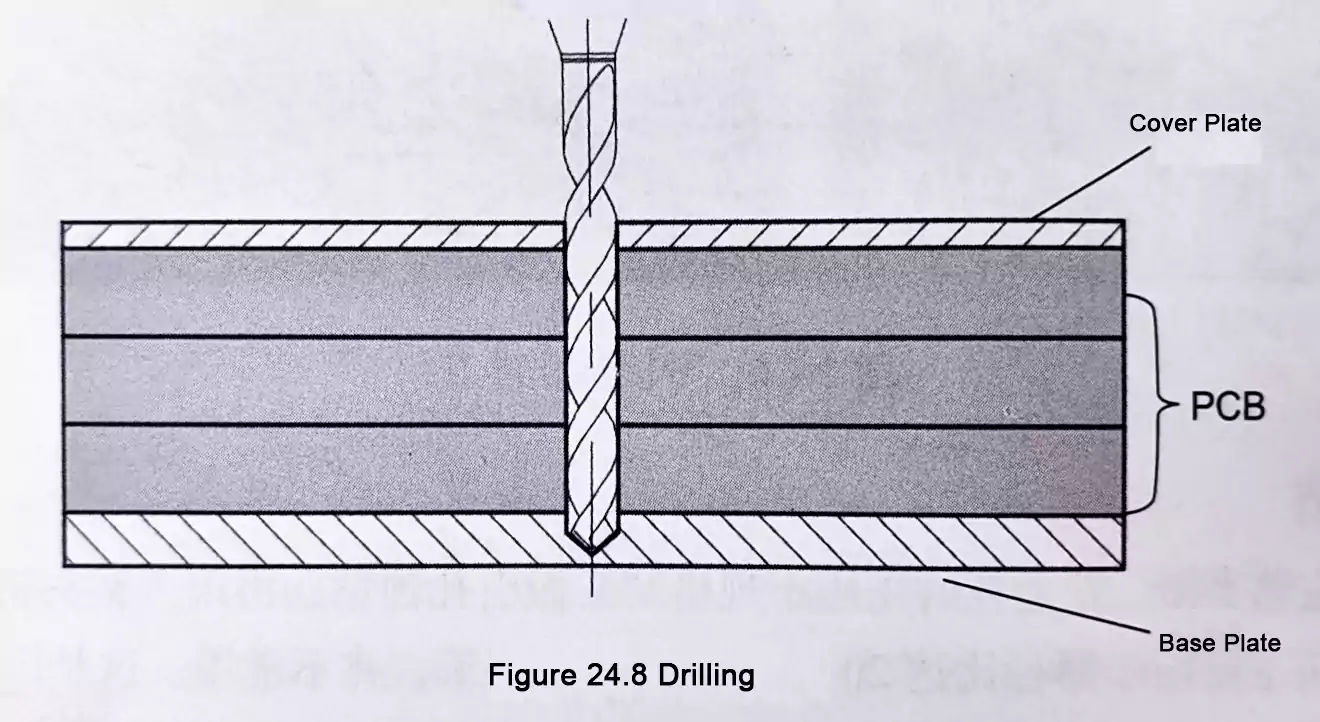

- הכנת Core: קידוח וציפוי חורים מעבר של הליבה.

- שכבות Build-Up: הוספת שכבות דיאלקטריות דקות (RCC או Prepregs ניתנים לקידוח לייזר).

- קידוח microvia (< 0.1 מ״מ).

- Desmear ומתכתת דפנות הויה.

- דימות LDI למסלולים דקים במיוחד.

- ציפוי נחושת וצריבה ליצירת דפוסי מוליכים.

- חזרה על בנייה ולמינציה לריבוי שכבות.

- מסכת הלחמה, גימור פני-שטח ובדיקות.

כל שלב Build-Up נוסף מגדיל עלות ומורכבות; לוחות חסכוניים עושים לרוב 1–2 Build-Ups לכל צד.

תהליכים מתקדמים כמו mSAP דוחפים קווי הולכה ל-< 30 µm עבור Ultra-HDI (מודולי 5G ומערכות RF קומפקטיות).

כללי DFM מרכזיים למתכנני HDI

(ערכי ייחוס—משתנים בין ספקים)

- קוטר microvia: 0.075–0.10 מ״מ

- יחס ממדים (Aspect Ratio): ≤ 0.8:1

- טבעת לכידה (Annular Ring): ≥ 0.10 מ״מ

- רוחב/מרווח מסלולים: 75–100 µm

- היסט בויות מוערמות: ≥ 50 µm בין ויות סמוכות

- עובי נחושת סופי: 18–35 µm אופייני

מומלץ להימנע מיותר מ-3 microvias מוערמות ברצף. כשאפשר—העדיפו Staggered או Skip-Vias (L1→L3) להפחתת סיכון ועלות.

שלמות אות והספק (SI/PI)

מסלולים קצרים ב-HDI מפחיתים פרזיטים ומשפרים את שלמות האות.

יתרונות:

- פחות Stubs → פחות החזרים

- מסלולי חזרה קצרים → שטח לולאה קטן

- זוגות Power-Ground צפופים יותר → רעש מופחת

טיפים לתכן:

- שמרו שכבות ייחוס רציפות מתחת למסלולים מהירים.

- הוסיפו Stitching Vias ליד חיתוכי מישורים או בקצוות.

- בזוגות דיפרנציאליים שמרו מרווח קבוע, גם מעל ויות.

- בצעו סימולציית אימפדנס מוקדמת; בדיאלקטריים דקים טולרנסים קטנים יותר.

אמינות ובדיקות

בגלל דיאלקטריים דקים וויות זעירות—נדרשת הסמכה קפדנית.

בעיות נפוצות:

- סדק צוואר ב-microvias מוערמות עקב עומס תרמי מחזורי.

- עייפות נחושת לאחר רפלואו מרובים.

- CAF (חוט אניוני מוליך) כאשר השרף והזכוכית אינם מותאמים.

שיטות אימות:

- IST (Interconnect Stress Test)

- הלם/מחזורי חום

- X-Ray וחתך מטלוגרפי

שוקי אמינות-גבוהה (רכב, תעופה/חלל, ביטחון) דורשים אישור נוסף לאיכות מילוי ויה וציפוי.

בחירת חומרים ל-HDI

החומר משפיע על כושר הייצור ועל ביצועי האות:

- RCC (Resin-Coated Copper): מאפשר דיאלקטריים דקים לקידוח.

- Prepregs לקידוח לייזר: משפרים היצמדות בין שכבות Build-Up.

- Spread-Glass: יציבות ממדית טובה יותר.

- חומרים בעלי הפסד נמוך (Df < 0.005): הכרחיים ל-SerDes > 10 GHz.

- העדיפו CTE מאוזן ו-Tg גבוה (> 170°C) לעמידות בלמינציות ורפלואו חוזרים.

שיקולי HDI בהרכבת SMT

- Via-in-Pad חייבת להיות ממולאת ומצופה עד פני שטח ישרים כדי למנוע חללים/משיכת בדיל.

- Solder-Mask Plugging מתחת ל-BGA מונע בועות אוויר.

- תכנון סטנסיל: Step-Stencil או פתחים קטנים יותר לרכיבים 0201/01005.

- פרופיל Reflow: שליטה בקצב החימום כדי למנוע עיוות של Cores דקים.

- ניהול תרמי חשוב בגלל צפיפות רכיבים והתפלגות נחושת צפופה.

טעויות תכן נפוצות ופתרונות

- יותר מדי microvias מוערמות → סדקי גלוון → השתמשו ב-Staggered או הפחיתו Build-Ups.

- VIP לא ממולאת → משיכת בדיל ומפרקים חלשים → VIPPO ממולא נחושת/אפוקסי ומצופה-ישר.

- טבעת לכידה קטנה → שבירה בקידוח → הגדלת Pad לכידה.

- Core דק ללא איזון → עיוות בלמינציה → שכבות איזון/Prepreg עבה יותר.

- מרווחי בידוד קטנים סביב microvias → קצרים לאחר צריבה → הגדלת Clearance או עדכון כללי התכן.

מונחים מרכזיים

- HDI – High-Density Interconnect

- Microvia – ויה זעירה המחברת שתי שכבות סמוכות

- Blind Via / Buried Via – ויה עיוורת / קבורה

- VIP / VIPPO – Via-in-Pad ממולאת ומצופה עד פני-שטח

- SBU – Sequential Build-Up

- ELIC – Every Layer Interconnect (Any-Layer HDI)

- mSAP – Modified Semi-Additive Process לקווים אולטרה-דקים

סיכום

טכנולוגיית HDI מאפשרת תכן קומפקטי ואמין.

באמצעות מסלולים דקים, Stack-ups מיטביים ומבני ויה מבוקרים—ניתן להשיג ביצועי מהירות גבוהים בשטח מוגבל.

ב-Fastturn PCB אנו מייצרים לוחות HDI עם קידוח מיקרו-מכני, דימות LDI ולמינציה רב-שכבתית ליישומי תקשורת, רכב ואלקטרוניקה צרכנית.

יכולות:

- קוטר ויה: 0.10 מ״מ (מכני)

- רוחב/מרווח מוליך: 0.075 מ״מ

- עד 20 שכבות

- מילוי ויה וציפוי פני-שטח זמינים

עם שותף ייצור אמין ומשמעת תכן נכונה, HDI מספקת ביצועים חשמליים מעולים ופורמ-פקטור קומפקטי—מוכנים לדור הבא של האלקטרוניקה.