Une fois la définition du système, le découpage fonctionnel, la simulation et le placement terminés, le travail de conception de PCB haute vitesse entre dans sa phase la plus critique.

À ce stade, l’objectif n’est plus simplement de prouver que le schéma fonctionne. Il s’agit de s’assurer que le design physique résiste aux temps de montée/descente réels (edge rates), à la densité de routage, aux limites de fabrication et à la répétabilité en production. Autrement dit, c’est ici que le flux de conception PCB passe de l’intention de conception à une réalité industrialisable.

Ce guide couvre la seconde moitié du PCB design flow pour la conception de PCB haute vitesse, avec un focus sur le routage de PCB haute vitesse, l’intégrité du signal (PCB signal integrity), l’analyse temporelle (PCB timing analysis), les contraintes de routage (PCB routing constraints), l’analyse de routabilité (PCB routability analysis), ainsi que la livraison d’un ensemble complet de fichiers de fabrication PCB (PCB manufacturing files).

Contraintes de routage PCB : l’intégrité du signal commence avant le routage haute vitesse

Sur des designs basse vitesse, la connectivité logique suffit souvent. En PCB haute vitesse, ce n’est plus le cas.

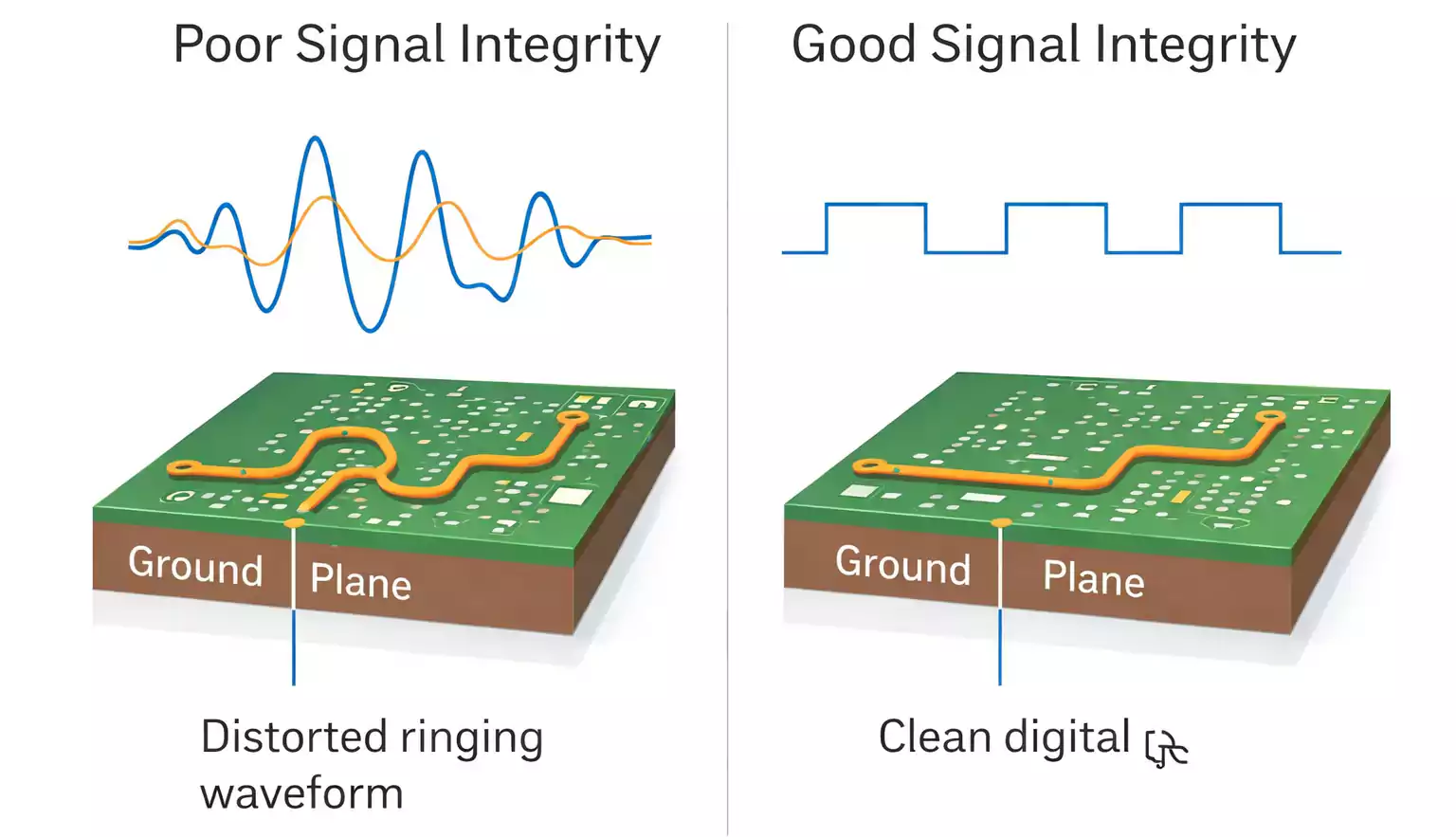

Lorsque les temps de montée/descente augmentent et que les délais d’interconnexion deviennent significatifs, les pistes (traces) se comportent comme des lignes de transmission. La géométrie du layout impacte alors directement l’intégrité du signal. Les modes de défaillance courants incluent :

- Réflexions

- Diaphonie (crosstalk)

- Oscillations (ringing)

- Dépassement et sous-dépassement (overshoot/undershoot)

- Commutations parasites / erreurs de seuil (false switching / threshold errors)

Il faut donc définir et revoir les contraintes de routage immédiatement après le placement, avant d’attaquer le routage haute vitesse détaillé.

Les contraintes clés incluent généralement :

- Topologie driver-vers-charges (driver-to-load topology)

- Stratégie de terminaison et emplacement (termination)

- Ordonnancement des nœuds sur le net

- Contrôle des longueurs et limites de skew

- Cohérence d’impédance (simple-extrémité et différentiel)

L’objectif est d’obtenir un comportement de transmission prévisible avant de figer le cuivre. Dans les backplanes haute vitesse et les plateformes de calcul, ces contraintes sont essentielles : de petits choix physiques peuvent provoquer une instabilité importante.

Analyse temporelle PCB et modélisation des lignes de transmission : anticiper avant de router

Une fois le placement stabilisé, les positions physiques et les couloirs de routage approximatifs sont connus. Avant même le routage détaillé, cela permet une analyse temporelle précoce et une modélisation des lignes de transmission basées sur :

- Estimation des longueurs et des temps de propagation (flight times)

- Hypothèses de topologie (point-à-point vs multi-drop)

- Signaux d’alerte précoces : réflexions et distorsion de fronts

Comme les coordonnées des nœuds et l’ordre de connexion sont définis, il est possible de simuler le comportement probable et d’identifier les problèmes de marge temporelle tant que les modifications restent simples.

La logique est directe : corriger des problèmes d’intégrité du signal après routage coûte cher ; les détecter avant le routage haute vitesse est plus efficace et maîtrisé. Pour des équipes expérimentées, l’analyse précoce du timing et de l’interconnexion est une étape standard de réduction des risques dans le flux de conception.

Bruit et intégrité du signal : bruit interne vs interférences externes

Tous les bruits n’ont pas la même origine, et traiter tous les problèmes de bruit de la même manière mène à des mitigations inefficaces. Une approche plus propre consiste à distinguer deux catégories.

1) Bruit interne du système (intrinsèque)

Cela inclut :

- Bruit thermique

- Bruit de commutation

- Bruit intrinsèque du signal

Le bruit interne fait partie du fonctionnement normal. Il ne peut pas être supprimé, mais il peut être maîtrisé en améliorant le rapport signal/bruit et en contrôlant l’implémentation physique : chemins de retour, découplage, gestion des fronts (edge-rate).

2) Interférences externes (couplées / environnementales)

Ces bruits proviennent de l’extérieur du circuit immédiat et peuvent être particulièrement destructeurs dans les zones analogiques sensibles, proches RF, et les architectures mixtes (mixed-signal).

Mitigations typiques :

- Blindage

- Amélioration de la stratégie de masse

- Isolation physique des blocs sensibles

- Réseaux de filtrage

- Conception d’interfaces contrôlées

Comprendre si le problème est intrinsèque ou externe aide à choisir la bonne solution et accélère le debug.

Si le timing ou l’SI échoue : revoir placement et topologie (avant routage)

Si la modélisation précoce révèle :

- Un délai excessif

- Une faible marge temporelle

- Des réflexions significatives

- Une distorsion des fronts ou du ringing

La bonne réponse n’est pas « on route et on verra ». En PCB haute vitesse, c’est le moment de revoir placement et topologie.

Actions correctives fréquentes :

- Rapprocher les composants critiques

- Réduire la longueur des chemins prioritaires

- Modifier la topologie (point-à-point vs multi-drop)

- Ajouter, retirer ou déplacer la terminaison

- Ajuster le stackup pour supporter les contraintes

Dans les systèmes numériques au GHz — surtout sur des cartes physiquement grandes — la longueur et la topologie influencent directement le comportement temporel global. Itérer à ce stade augmente la probabilité de succès du premier tour et évite des reroutages tardifs.

Analyse de routabilité : vérifier qu’on peut router la carte telle qu’elle est placée

Beaucoup de designs échouent non pas à cause d’erreurs électriques, mais parce que les ressources de routage ont été sous-estimées. L’analyse de routabilité doit donc intervenir avant le routage détaillé.

Elle doit répondre à des questions comme :

- Le nombre de couches signal est-il suffisant ?

- L’espacement du placement est-il réaliste pour le fanout attendu ?

- Où sont les zones de congestion ?

- Des canaux critiques sont-ils bloqués par des contraintes mécaniques ou des keepouts ?

- Le floorplan supporte-t-il le stackup et la stratégie de vias ?

Les outils EDA modernes fournissent des métriques de congestion et des checks de faisabilité. Si la routabilité est faible, la bonne solution est généralement de revoir placement/couches, plutôt que de forcer un routage dégradé.

Cette étape est particulièrement importante sur les cartes multilayers denses et les designs mixed-signal, où les contraintes réduisent fortement l’espace de routage utile.

Routage de PCB haute vitesse : exécuter dans les contraintes, pas contre elles

Une fois le placement, l’analyse temporelle et la routabilité validés, le routage haute vitesse détaillé commence.

Le routage doit respecter les contraintes définies, notamment :

- Règles de largeur et d’espacement des pistes

- Matching de longueur et contrôle du skew

- Exigences d’impédance

- Couplage et symétrie des paires différentielles

- Continuité des chemins de retour

- Limites de diaphonie et classes d’espacement

En pratique, les équipes performantes utilisent souvent :

- Routage manuel pour les nets haute vitesse critiques

- Routage contrôlé pour la distribution d’alimentation

- Routage automatique pour les signaux non critiques

- Nettoyage et optimisation post-routage

Un « playbook » de routage — politique de couches, règles de vias, priorités de classes de nets, critères de revue — améliore la cohérence et réduit les itérations de revue dans les équipes multi-ingénieurs.

Vérification post-routage : boucler sur SI, timing et connectivité

Le routage terminé ne signifie pas que le design est fini : les longueurs et géométries réelles doivent maintenant être revalidées.

Les contrôles post-routage incluent généralement :

1) Revalidation de l’intégrité du signal et du timing

- Confirmer les marges temporelles avec les longueurs réelles

- Recontrôler réflexions et qualité des fronts

- Évaluer les risques de couplage entre nets agresseur/victime

2) Vérification netlist / connectivité

- S’assurer qu’aucune connectivité non voulue n’a été introduite

- Vérifier l’absence d’open/short lors des modifications

3) Conformité fabrication et règles

- Vérifier largeur/espacement

- Valider les dégagements de solder mask

- S’assurer que des pads ne sont pas exposés ou recouverts par erreur

- Confirmer que les structures d’impédance sont fabricables

C’est à ce stade que beaucoup de problèmes « ça marche dans le CAD » sont évités avant de devenir « ça rate au build ».

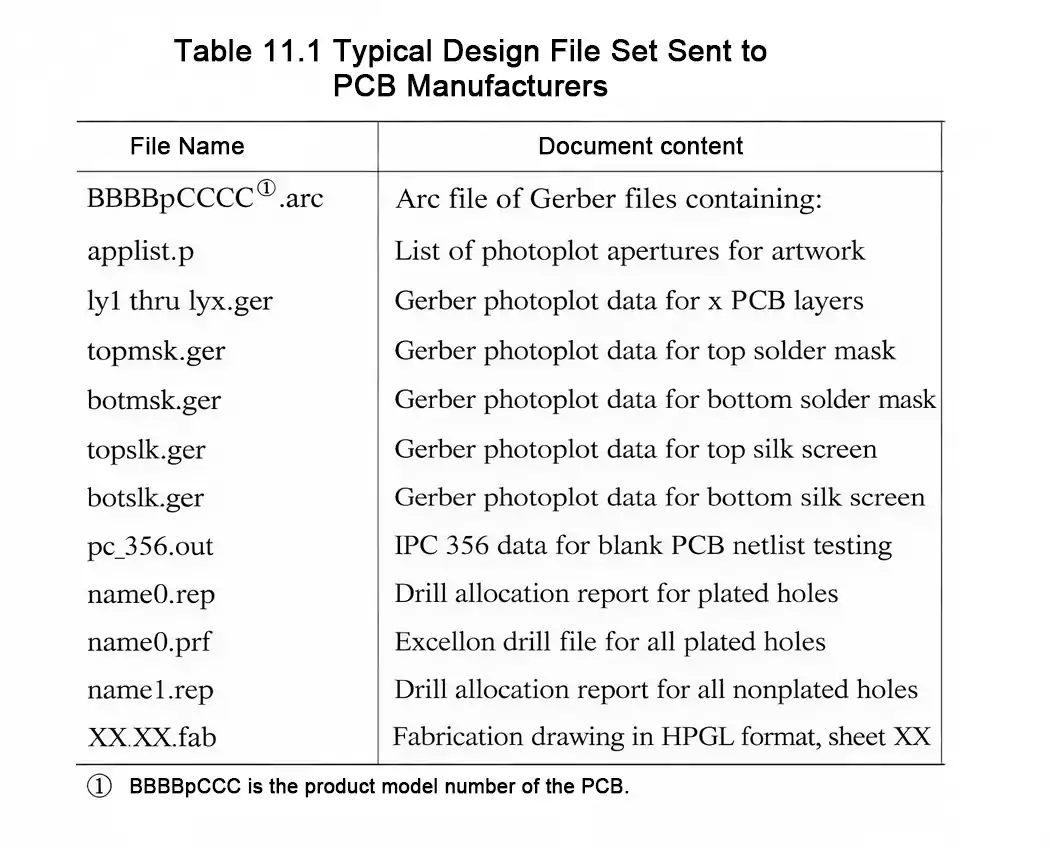

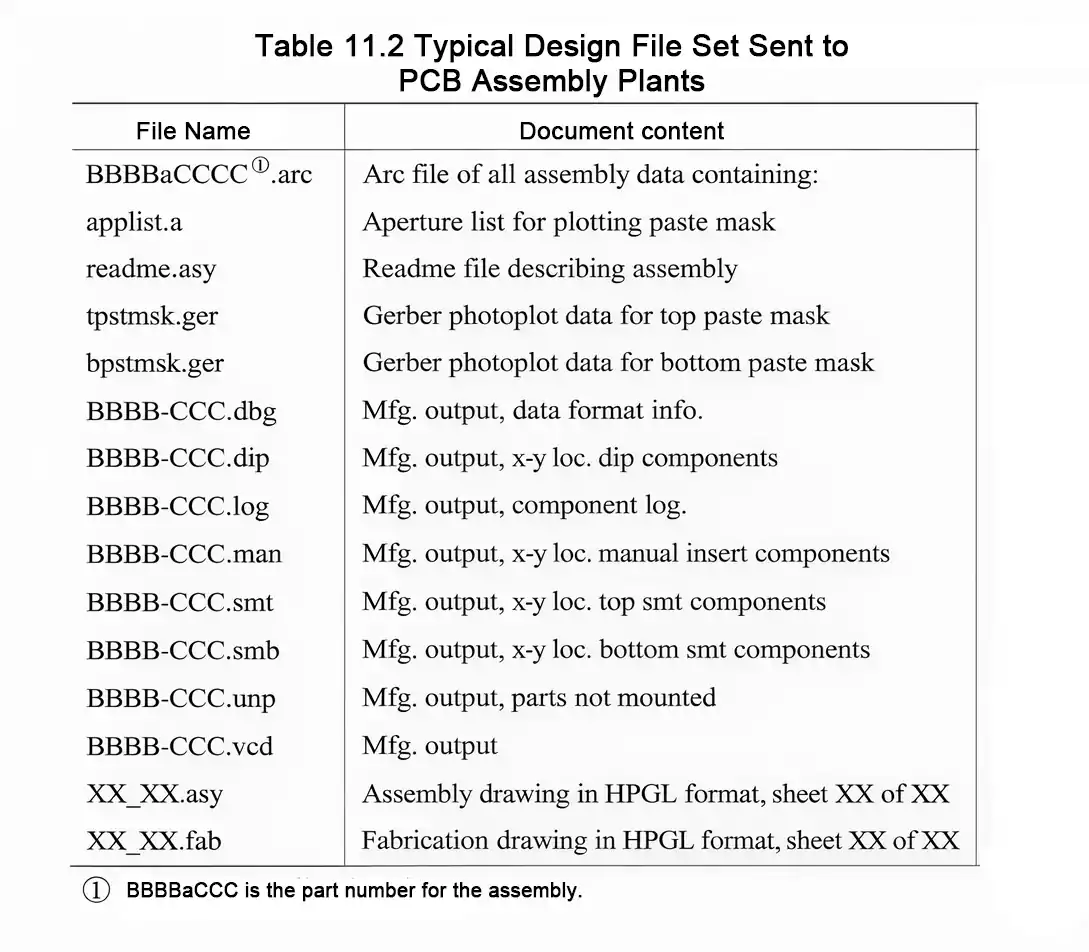

Fichiers de fabrication PCB : de la base de design au package production

Une fois la vérification terminée, le flux de conception passe à la mise en production. Un package de release complet inclut généralement :

- Sorties fabrication (Gerber ou ODB++)

- Fichiers de perçage

- Données pick-and-place

- Plans/assemblage (assembly drawings)

- Données de test carte nue (si nécessaire)

- Documentation de test fonctionnel (si nécessaire)

- BOM complète et validée

Ces fichiers de fabrication sont ceux que les fabricants et assembleurs utilisent réellement. Toute ambiguïté entraîne retards, risques de rebut et baisse de rendement. En B2B, la clarté et l’exhaustivité de ces fichiers sont directement liées aux délais, à la répétabilité et à la montée en volume.

Archivage : protéger l’actif “PCB haute vitesse”

Dernière étape : l’archivage structuré.

L’archivage ne sert pas seulement à sauvegarder. Il supporte :

- Révisions futures et ECO

- Investigation des pannes terrain

- Traçabilité des versions

- Gestion du cycle de vie

Une archive complète doit inclure la base native, les sorties fabrication, les documents de test, l’historique de révision et des notes d’ingénierie. Ne pas pouvoir reproduire un design plus tard devient un risque business, pas seulement un désagrément.

Conclusion : le PCB haute vitesse dépend d’un flux de conception rigoureux

La seconde moitié du flux de conception PCB détermine si un PCB haute vitesse ira en production sans heurts ou entrera dans une boucle de debug coûteuse.

Quand les contraintes de routage, l’analyse temporelle, la routabilité et un routage haute vitesse discipliné sont exécutés comme un processus cohérent — puis validés avec des données physiques réelles — on obtient une carte qui :

- Se fabrique de façon régulière

- S’assemble de manière fiable

- Passe les tests efficacement

- Monte en volume

- Reste maintenable sur le long terme

C’est la différence entre une carte qui marche au labo et un produit qui se livre de manière fiable.