Einleitung

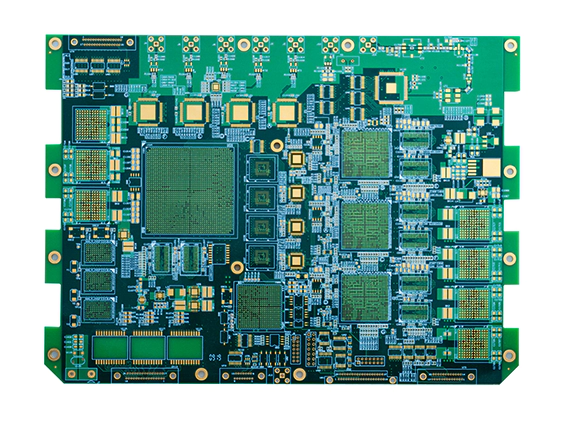

Die Oberflächenmontagetechnik (SMT) – oft auch SMT-PCB-Bestückung oder Surface-Mount-PCB-Assembly genannt – ist heute das Fundament der modernen Elektronikfertigung.

Indem winzige SMD-Bauteile (Surface-Mount Devices) direkt auf die Kupferpads der Leiterplatte gesetzt werden, ermöglicht SMT leichtere, schnellere und zuverlässigere Schaltungen als die Durchstecktechnik der Vergangenheit. Von Smartphones und Wearables über die industrielle Automatisierung bis hin zu Leistungssystemen für Elektrofahrzeuge: Nahezu jedes hochverdichtete Produkt, das Sie heute in der Hand halten, beruht auf präzisen SMT-Bestückungsverfahren.

Doch „SMT richtig machen“ bedeutet weit mehr, als Leiterplatten durch einen Bestückungsautomaten zu schicken. Erfolgreiche Projekte erfordern ein klares Verständnis der Design-for-Assembly-Regeln, die Auswahl von Schablone und Lötpaste, Reflow-Profilierung, Inline-Inspektion und Kostentrade-offs – und zwar bevor das erste Bauteil platziert wird.

Deshalb destilliert dieser Deep-Dive den gesamten SMT-Workflow in praxisnahe, ingenieurstaugliche Erkenntnisse, die Sie sofort umsetzen können.

SMT-Basics

1) Was ist SMT-Bestückung?

Bei der SMT-Bestückung werden SMD-Bauteile direkt auf die Pads einer Leiterplatte (PCB) gesetzt – ohne durchkontaktierte Bohrungen. Weil die Bauteile plan aufliegen, passt mit SMT mehr Funktionalität auf weniger Fläche; zugleich sind hochautomatisierte, schnelle Fertigungslinien möglich.

Begriff — Bedeutung — Einordnung

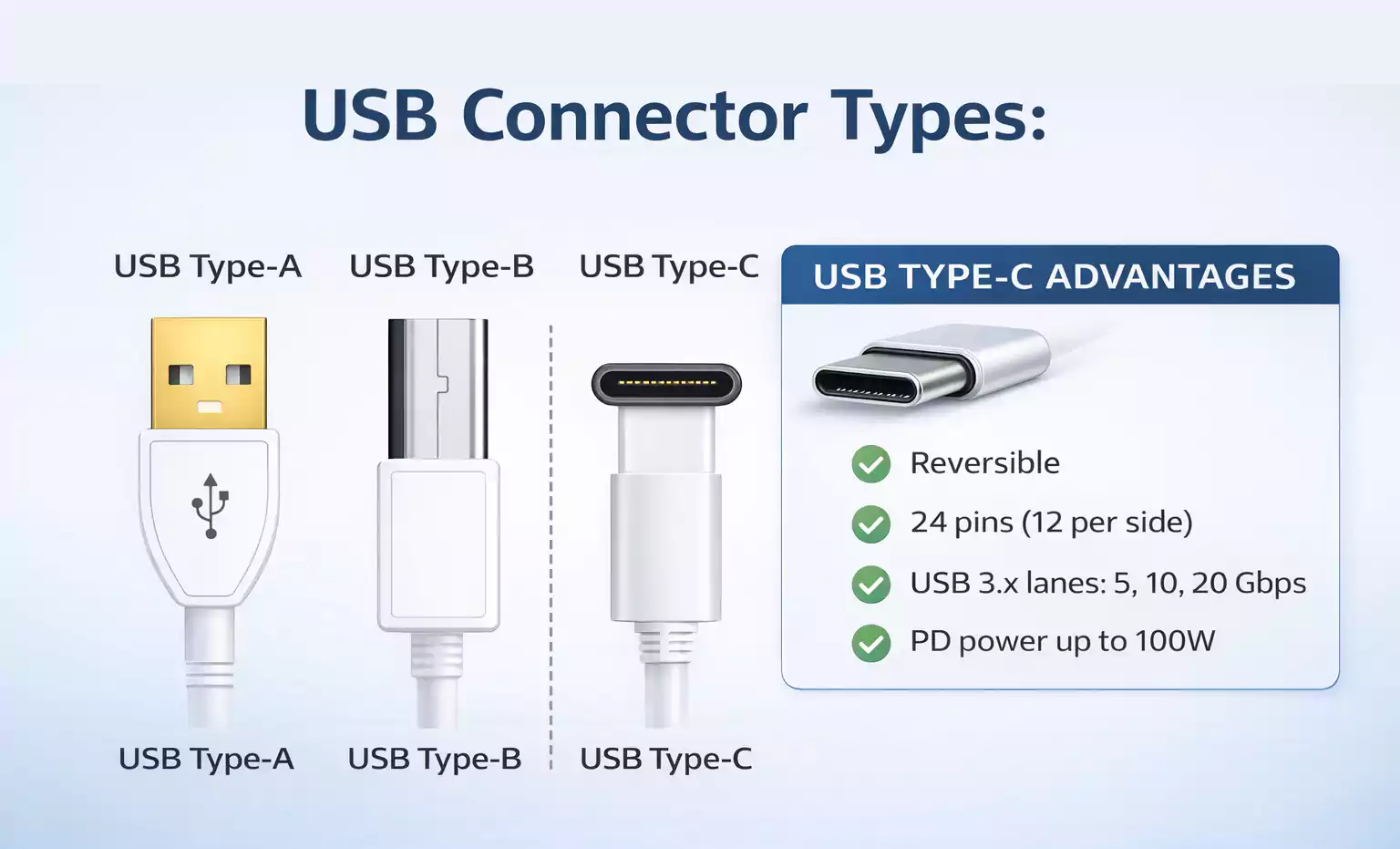

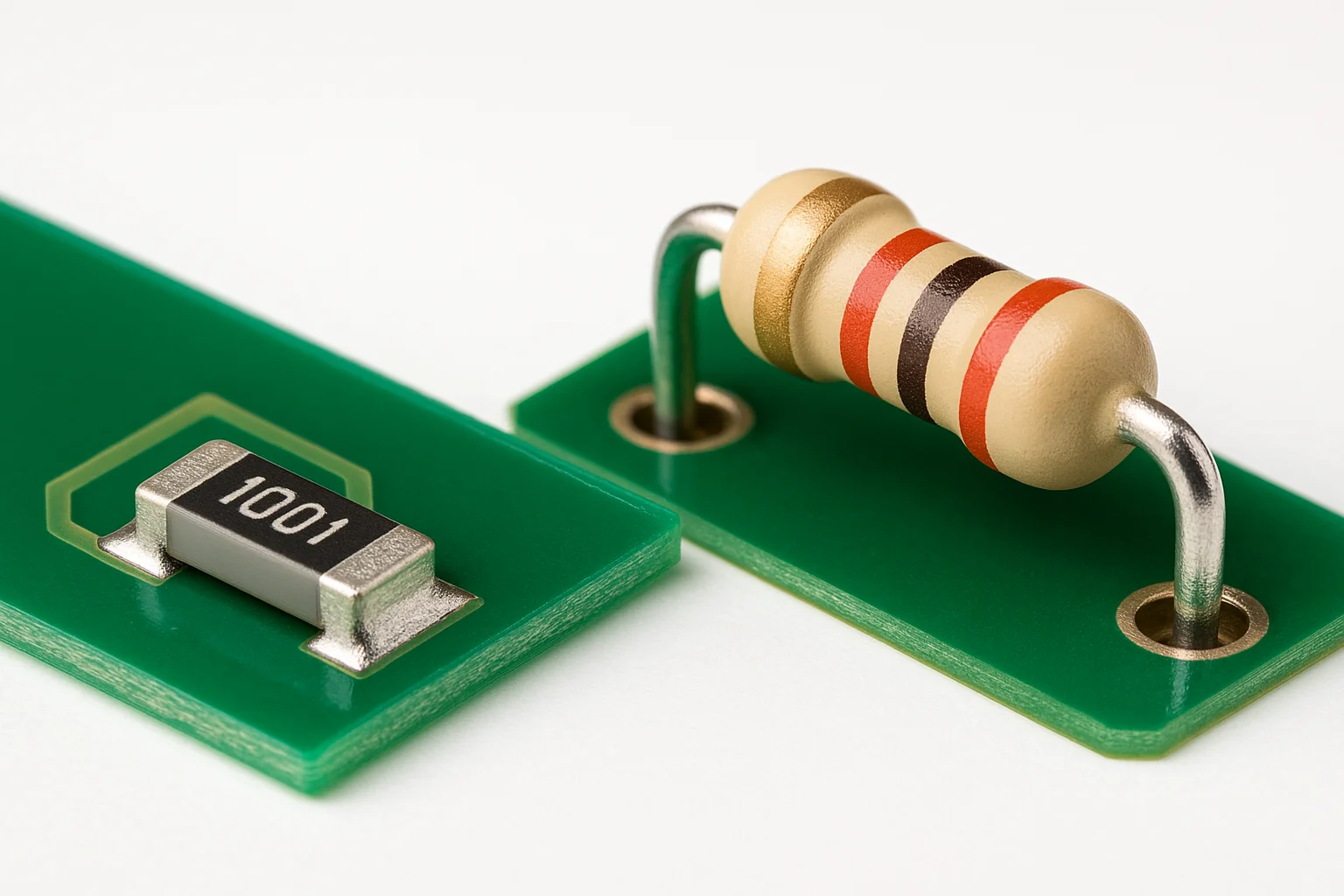

- SMD (Surface-Mount Device): Das einzelne Bauteil (Widerstand, IC, BGA usw.) — Baustein.

- SMT (Surface-Mount Technology): Die gesamte Fertigungsmethodik (Lötpastendruck, Bestückung, Reflow, Inspektion) — das „Wie“.

- SMT-Bestückung / Surface-Mount-PCB-Assembly: Fertig bestückte Leiterplatte ausschließlich (oder überwiegend) mit SMDs — das Ergebnis.

- THT (Through-Hole Technology): Klassische Technik mit bedrahteten Bauteilen durch Bohrungen und Wellen-/Handlöten — weiterhin üblich für Stecker, große Passivteile oder stark belastete Komponenten.

2) SMT in 60 Sekunden – Zeitleiste

- 1960er – frühe Versuche: IBM erprobt „planare Montage“, um Militärschaltungen zu verkleinern.

- 1980 – erste Massenadoption: 1206/0805-Bauformen in Videorekordern und Pagern reduzieren die Leiterplattenfläche um ~50 %.

- 1990er – Mobilboom: 0603/0402-Passivteile ermöglichen erste Klapphandys; BGA/CSP steigern I/O-Dichte.

- 2005–2015 – Miniaturisierungsrennen: 0201, dann 01005 befeuern Smartphones & Wearables; Reflow-Öfen mit Stickstoff reduzieren Voids.

- Heute: 0,3-mm-BGA-Pitch, eingebettete Passivteile und AOI/X-Ray mit KI drücken Fehlerraten in Hochvolumenlinien auf < 50 DPMO.

3) Warum SMT statt THT?

| Faktor | SMT-Bestückung | THT-Bestückung |

|---|---|---|

| Bauteildichte | 2–10× höher; beide Seiten nutzbar | Limitiert durch Lochdurchmesser & Abstände |

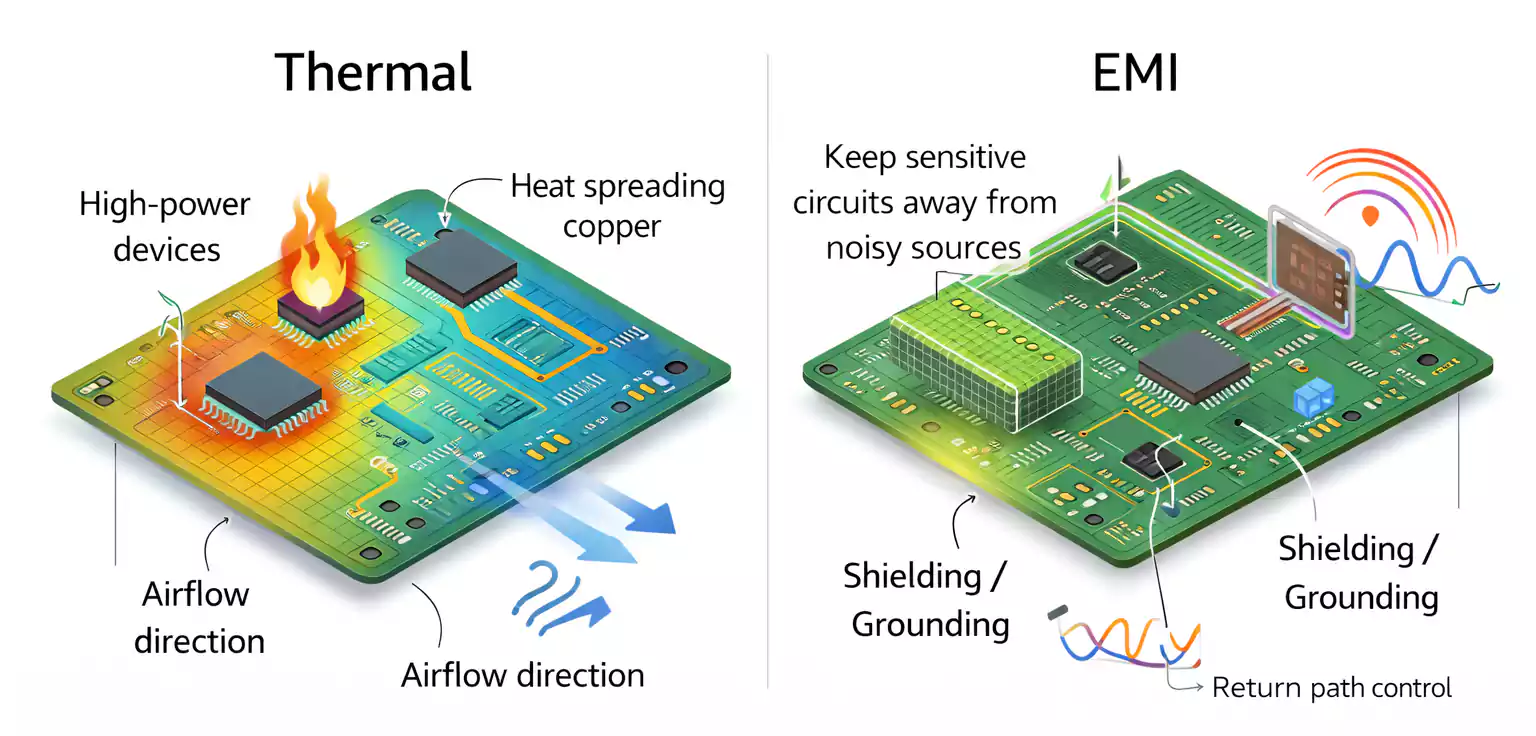

| Elektrische Performance | Geringere Parasitics → höhere Signalintegrität | Längere Anschlüsse → mehr Induktivität |

| Automatisierungsgeschwindigkeit | > 60 000 CPH* moderne Bestücker | 3 000–4 000 CPH mit Wellenlöt-Paletten |

| Thermik & Mechanik | Geringe thermische Masse; stoßfest | Drähte puffern, erhöhen aber Masse |

| Kosten bei Volumen | Kleinere Boards + Vollautomatik → geringere BOM & Arbeit | Bohren, manuelles Bestücken, Wellenlöten teurer |

*CPH = Components per Hour (Bauteile pro Stunde).

Mixed/Hybrid (SMT + THT) bleibt gängig für große Stecker, Transformatoren oder wärmeintensive Teile, die mechanische Grenzen von SMT überschreiten.

4) In einer SMT-Linie (5 kritische Stationen)

- Schablonendruck – Lötpaste mit ± 25 µm Genauigkeit aufbringen.

- SPI (Solder Paste Inspection) – 3D-Scan von Höhe/Volumen der Paste.

- Pick-and-Place – Kamerageführte Roboter platzieren SMDs mit bis zu 4 m/s.

- Reflow-Ofen – Mehrzonen-Profil schmilzt Paste und bildet Lötstellen.

- Post-Reflow-Inspektion – AOI, Röntgen und ggf. ICT finden Opens, Bridges & Voids.

Wer diese Stationen früh versteht, setzt richtige Padgeometrien, Fiducials und Panel-Regeln — und spart teure Re-Spins.

SMT vs. THT vs. Mischbestückung

Die Wahl der Methode ist ein Balanceakt aus Größe, Zuverlässigkeit, Kosten und Taktzeit.

| Kriterium | SMT | THT | Mischbestückung |

|---|---|---|---|

| Dichte | Höchste — beidseitig; bis 01005 & 0,3-mm-BGA | Niedrigste | Mittel: Kleinteile SMT, robuste THT |

| Signalqualität | Kürzere Interconnects → weniger L/C; ideal für RF & High-Speed | Längere Drähte → mehr Parasitics | Kritische Netze SMT; Power/Stecker THT |

| Mechanik | Gut bei Stoß/Vibration bei guter Leiterplattenabstützung | Drähte verankern — top für Zug/Drehmoment | THT gezielt als Zugentlastung |

| Geschwindigkeit | > 60k CPH; vollautomatisches Reflow | 3–4k CPH; oft manuelle Bestückung + Welle/Selektiv | Zwei Durchläufe (Reflow + Welle/Selektiv) |

| Tooling/NPI | Gering — keine Lochbohrungen für Pins; günstige Schablonen | Höher — Bohren, Wellenpaletten, Handarbeit | Höchstes Setup; zwei Lötprofile & Prüfungen |

| Boardfläche/Layer | Kleinere Boards oder weniger Lagen → günstiger | Größer; oft zusätzliche Lagen | Zwischenlösung |

| Test/Inspektion | AOI, SPI, X-Ray, ICT automatisiert | Häufig visuell + ICT; AOI bei Welle seltener | Dual: AOI nach Reflow; THT-Lötungen visuell/AOI |

| Thermische Zyklen | Gut bei optimiertem Reflow; geringe Masse → weniger ΔT-Stress | Exzellent — Drähte federn thermisch | Abhängig vom Lötverbund |

| Typische Anwendungen | Smartphones, IoT, Wearables, HF | Netzteile, Automotive-Stecker, Relais, Luft-/Raumfahrt | Haushaltsgeräte, LED-Licht, EV-Lader, Medizintechnik |

| Sauberkeit | Kontrollierte Reflow-Atmosphäre; No-Clean verbreitet | Flussmittelreste der Welle oft waschen | Chemieabgleich nötig (No-Clean + waschbar) |

Kern-Insights fürs Team:

- Dichte zuerst optimieren: Ist Produktgröße/-gewicht oder RF top-Priorität → reines SMT – weniger Lagen, kürzere Leitungen, Volumenautomation.

- THT einsetzen, wo Missbrauch absehbar ist: Hochstromstecker, Trafos, große Elkos, Schalter überstehen Drehmoment/Erwärmung/Steckzyklen besser.

- Hybrid-Kosten früh planen: Mixed spart Fläche, erhöht aber Tooling & zweite Prüfstrecke — im TCO-Sheet modellieren.

- Thermische Profile synchronisieren: THT muss Reflow-Peak (typ. 245 °C) überstehen; SMT darf bei Welle nicht überhitzen. Empfindliche Module clever platzieren.

BOM klar beschriften: Welche RefDes sind SMT, THT oder „entweder-oder“? Klare Fertigungshinweise reduzieren NPI-Zeit & Shopfloor-Unklarheit.

Der SMT-Prozess – 8 Schritte im Detail

Moderne SMT-Linien setzen bis zu 60 000 Bauteile/h bei Fehlerraten von nur wenigen ppm.

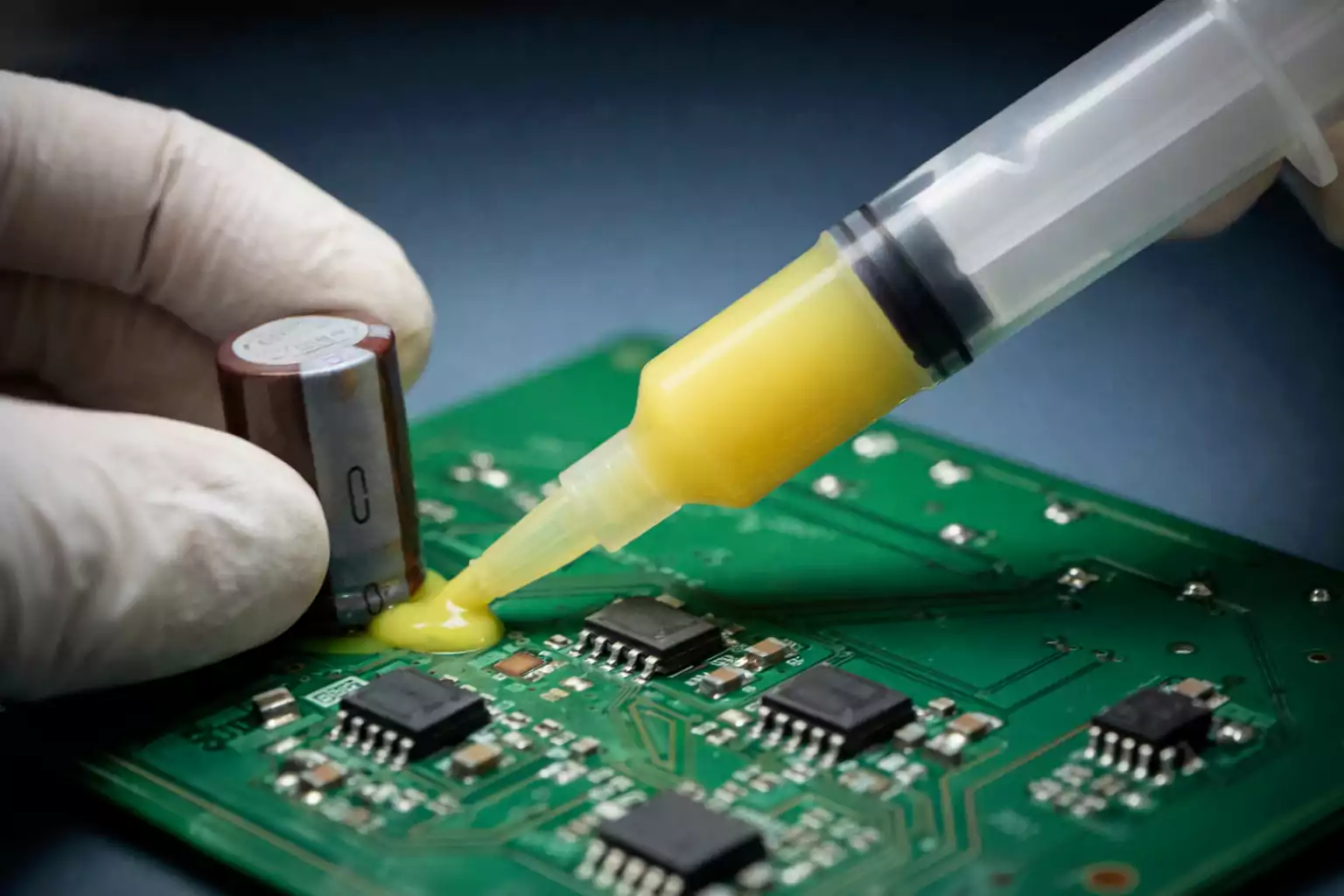

Schritt 1 – Schablonendruck (Lötpaste)

- Ziel: Exakt dosierte Pastenvolumina je Pad, ± 25 µm in XY, ± 15 % in Höhe.

- Hebel: Schablonendicke (100–150 µm), Aperturform (Home-/Inverted-Home-Plate, Window-Pane, Step), Rakelgeschwindigkeit/-druck, Pastenchemie (SAC, Bi-Sn).

- Best Practice: Laser-geschnittene, nano-beschichtete Edelstahlschablonen reduzieren Anhaftung & Brücken bei Fein-BGA.

- Typische Fehler: Zu wenig → Opens; zu viel → Shorts/Voids; verstopfte Aperturen → Tombstoning. SPI fängt hier > 80 % der Folgefehler ab.

Schritt 2 – 3D-SPI

- Ziel: Volumen/Fläche/Höhe verifizieren, bevor Bauteile verschwendet werden.

- KPIs: < 5 % Volumenabweichung Pad-zu-Pad; Cpk ≥ 1,33 für Höhe.

- Closed Loop: SPI-Daten regeln Ausrichtung/Rakeldruck der Drucker automatisch.

Schritt 3 – Pick-and-Place

- Ziel: Jede Platzierung innerhalb ± 30 µm bei > 30 000 CPH/Modul.

- Feeder-Strategie: Hohe Stückzahlen von Passiven auf Turret-Köpfen; Präzisionsdüsen für µBGA, 0201, QFN 0,4 mm.

- Design-Tipp: Globale/lokale Fiducials & Zielpads vorsehen, damit Vision Stretch/Skew in Echtzeit kompensiert.

Schritt 4 – Reflow-Löten

- Ziel: Glänzende, void-arme Lötstellen ohne Bauteilschäden.

- Profil:

Preheat (1–3 °C/s) → Soak (150–180 °C) → Peak (235–245 °C SAC; < 225 °C Low-Temp) mit 30–60 s über Liquidus → Cool (max. −3 °C/s). - Überwachung: Doppel-Thermoelemente an schwerster/leichtester thermischer Masse; TAL (Time Above Liquidus) 40–90 s.

Schritt 5 – AOI

- Ziel: Opens, Bridges, Polaritätsfehler, Lifted Leads direkt nach Reflow finden.

- Auflösung: Bis 10 µm/px, Schrägkameras gegen Schatten bei 01005.

- Programmierung: CAD-Netzliste importieren; Schwellwerte mit „Golden Board“ feinjustieren → False Calls < 200 ppm.

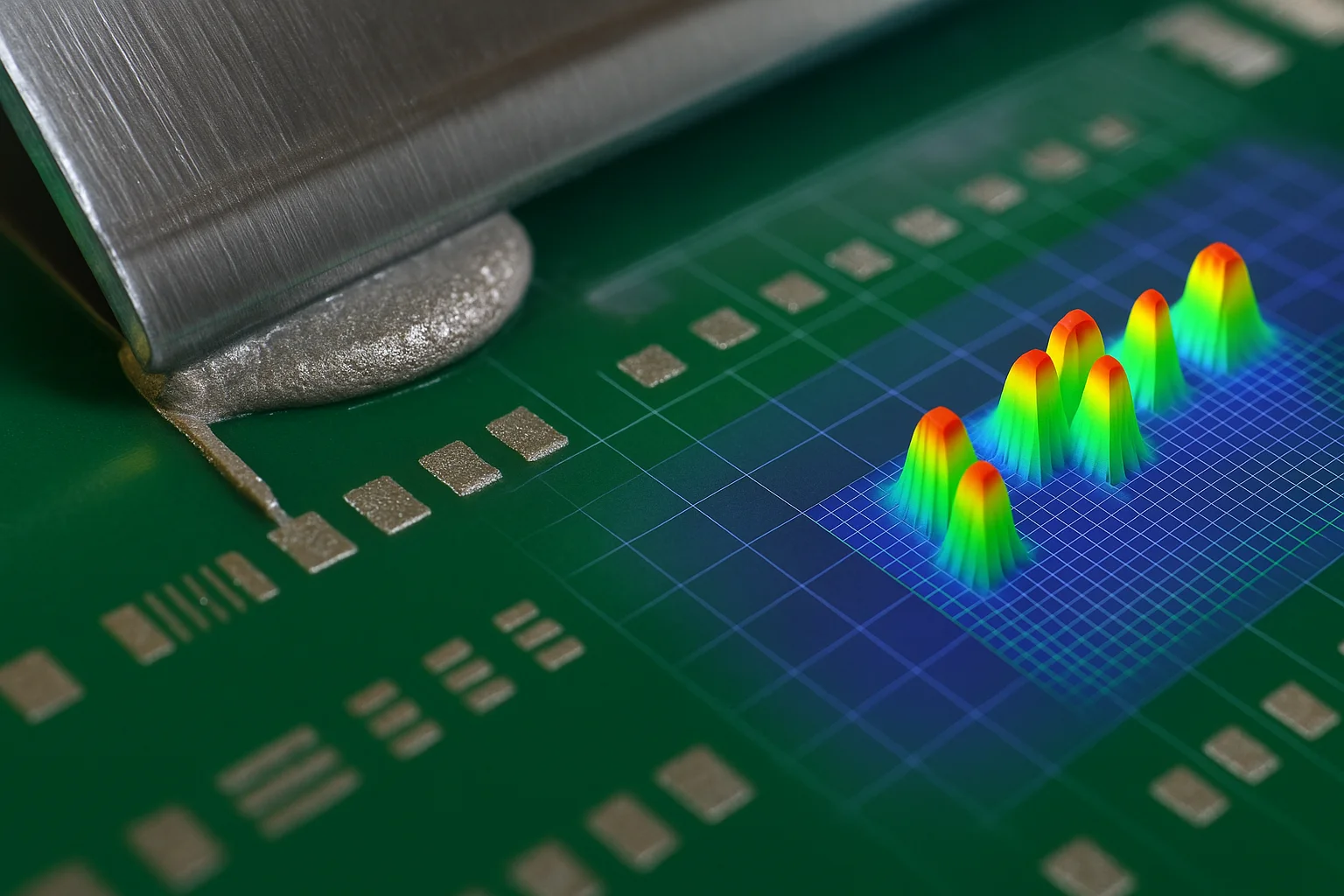

Schritt 6 – Röntgen (AXI/µCT) für verdeckte Lötstellen

- Wann: BGA, LGA, QFN (Bottom-Terminated), Leistungsmodule.

- Ziele: Void-Anteil < 25 % (Thermalpad), konsistente Ball-Stand-Offs, kein HIP/NWO.

- Advanced KPI: Automatisierte 3D-Voxel-Analyse korreliert Void-Ort mit Thermozyklus-Zuverlässigkeit.

Schritt 7 – ICT & FCT

- ICT: Nadelfeld prüft Kurzschluss/Unterbrechung, R/C/L, µC-Programmierung in < 1 s/Board.

- FCT: Echtbetrieb mit I/O; oft Boundary-Scan (JTAG) oder kundenspezifische Fixtures.

- DFT-Regeln: Testpads auf jeder Netz: Ø ≥ 0,9 mm, Pitch ≥ 1,3 mm; Lötstopp frei für Pogo-Pins.

Schritt 8 – Finish: Reinigen, Schutzlack, Verpackung

- Reinigung (falls nötig): Wässrig/semi-wässrig/Dampf; gemäß IPC-TM-650 Ionenkontamination ≤ 1,56 µg NaCl-Äq/cm².

- Conformal Coating/Potting: Für hohe Zuverlässigkeit/rauhe Umgebungen (IPC-CC-830).

- Laser-Mark & Serialisierung: Rückverfolgbarkeit bis Los/Datum und AOI/X-Ray-Daten.

- Verpackung: ESD-Trays, Tape-&-Reel oder Vakuumbeutel; Feuchteindikatorkarten für MSD.

Prozess-Takeaways

- Closed-Loop-Daten: SPI → Drucker und AOI/AXI → Pick-and-Place-Offsets verringern Drift, erhöhen Cpk schichtübergreifend.

- Profil-Verifikation: Jeden Reflow-Lauf aufzeichnen; Statistikbibliothek deckt Heizer-Drift früh auf.

- Yield-Mathe:

[Y=\left(1-\frac{\mathrm{DPMO}}{1,000,000}\right)^n,\quad n=\text{Bauteile/Board}.]

Selbst 99,9 % Platziergenauigkeit ergibt bei 250 Bauteilen nur 74 % — ergo: strenge Prüf-Gates sind Pflicht.

Design für SMT — DFM, DFT & Gehäusegrößen

Effiziente SMT beginnt in der CAD-Software.

1) DFM — Landpattern & Layout-Regeln

- Bibliothek: IPC-7351 (z. B. IPC-7351C „Density Level B“) als Basis; Pads nur für Spezial-Reflow anpassen.

- Kupfer-zu-Lötstopp-Abstand: ≥ 75 µm bei < 0,5 mm-Pitch (QFN/BGA); ≥ 100 µm bei Standardpassiven.

- Via-in-Pad: Microvias (≤ 0,3 mm) füllen & plattieren; ungefüllte Vias ≥ 0,5 mm Abstand zu Pads.

- Keep-Outs & Fiducials: 3 mm um globale, 1 mm um lokale (BGA-Ecke).

- Panelization: 3-seitige Tooling-Rails (≥ 5 mm), Sollbruch-„Mouse-Bites“ alle 75 mm; V-Nut ≥ 1 mm Abstand zum Kupfer.

Pro-Tipp: Gleiche Orientierung für polarisierte Teile (Tantal-C, LEDs) je Reihe — reduziert Feederwechsel und passt zur AOI-Polaritäsbibliothek.

2) Schablone & Paste optimieren

- Dicke: 0,10–0,12 mm für 0,5-mm-Pitch & 0201; Step-Up 0,15 mm unter großen Induktivitäten.

- Aperturen: Home-Plate (± invertiert) ~ −15 % Pastenvolumen an QFP-Spitzen → weniger Brücken; Window-Pane auf Pads > 3×3 mm → weniger Voids unter MOSFETs.

- Paste: SAC305 Standard; Bi-Sn Low-Temp für Flex/LED. Type 5-Pulver bei 0,4 mm-Pitch, Type 6 bei 0,3 mm-µBGA.

3) DFT — Design for Test

- Bed-of-Nails/ICT: Pads Ø 0,9 mm, Pitch ≥ 1,3 mm auf jedem Netz; 50-mil-Grid.

- Boundary-Scan/JTAG: 0-Ω-Links als Puffer; TRST/TCK fern von High-Speed.

- Kantentest (Edge-Connector): 3–5 mm „Dwell-Zone“ hinter den Kontakten; Goldflash.

- DFT für AOI: Polaritäsmarken von oben sichtbar (Tantal-Fase, Pin-1-Markierung); keine hohen Elkos direkt neben 0201.

Faustregel: Jeder 1 mm² für Testpads spart 10 Minuten Trouble-Shooting in der Produktion.

4) Gehäusegröße & Pitch

| Package | Pitch/Körper | empfohlene Pad-Länge (mm) | Schablonenöffnung (%) | Hinweise |

|---|---|---|---|---|

| 0603 (1608 metrisch) | — | 0,90 | 100 % | Einstieg; gut nachzuarbeiten |

| 0402 (1005) | — | 0,65 | 100 % | Häufig in IoT/Wearables |

| 0201 (0603) | — | 0,40 | 90 % | Type 5-Paste; Reinraum-SMT empfohlen |

| 01005 (0402) | — | 0,25 | 85 % | Reflow-ΔT < 3 °C; AOI ≤ 7 µm/px |

| µBGA 0,5 mm | 0,5 mm | 0,30 | 90 % | Dog-Bone Fan-Out, Microvias in Pad |

| µBGA 0,3 mm | 0,3 mm | 0,18 | 80 % | Laser-Microvias gefüllt/gekappt; Type 6 |

Grenze des Schrumpfens: Unter 01005 und 0,3-mm-Pitch sinkt der Yield deutlich — es sei denn, man nutzt Stickstoff-Reflow, Unterseiten-Schablonenreinigung alle 3 Drucke und SPI-Pixel ≤ 10 µm.

Qualität & Inspektion – Null-Fehler-SMT aufbauen

„Inspektionspyramide“

▲ Level 5 Umwelt & Zuverlässigkeit (Stichprobe)

│ Level 4 Funktion/Systemtest (100 % oder Stichprobe)

│ Level 3 ICT (100 %)

│ Level 2 Röntgen AXI/µCT (selektiv)

│ Level 1 AOI + SPI (100 % inline)

└────────── Prävention (DFM/DFT/SPC)Level 1–2 fangen > 80 % der Defekte früh ab; Level 3 validiert Schaltungsintegrität; Level 4–5 belegen Langzeitzuverlässigkeit.

Inline-Optik & Pasteninspektion

- SPI: Ziel Cpk ≥ 1,33, Höhe ± 15 %; 3D-Moiré, Z-Auflösung 10 µm; Apertur-Flächenverhältnis 0,66–0,75, Schablonenwisch alle 5 Drucke.

- AOI: False Calls < 200 ppm; Escapes < 20 ppm; 15-MP-Kameras, 10 µm/px, 8-Richtungs-Beleuchtung. Polaritäsmarken top-seitig sichtbar halten.

Röntgen (AXI/µCT)

- Wann: BGA/LGA/QFN & Leistung.

- Metriken: Voids < 25 % (Thermalpad), < 10 % (RF-Masse); HIP < 500 ppb.

- Trend 2025: KI-gestützte Voxel-Analyse erkennt Mikrorisse (unsichtbar in 2D) und spart ~ 40 % Analysezeit.

ICT & Funktionstest

- ICT: Kurz/Offen, R/C/L, Flash-Programmierung; Pads Ø 0,9 mm/1,27-mm-Grid; HV-Netze (> 50 V) isolieren.

- Boundary-Scan: TRST, TCK, TDI, TDO, TMS mit 0-Ω-Links; spart > 40 Prüfspitzen.

- Funktion/Burn-In: Volleinschalten, Loopback, Last; 3 mm Dwell-Zone am Kantenstecker; Gold-Finish.

Umwelt & Zuverlässigkeit

- Thermal Cycling (−40 ↔ 125 °C, 1000 Zyklen): ΔR/R < 5 %; keine Lötermüdung.

- Power Cycling (10 k Ein/Aus, 4 A): Hotspots durch Voids in MOSFET-Pads.

- HAST/Feuchte-Wärme (85 °C/85 % rF, 96 h): Keine Korrosion; ICT-Pass.

- Random Vibration (10–2 k Hz, 8 Grms): Keine Risse in MLCC, keine Kontaktabbrüche.

Profile gemäß JEDEC JESD22 oder IPC-9701 für die jeweilige Produktklasse wählen.

Defekt–Ursache–Gegenmaßnahme (Auszug)

- Tombstoning 0402: Unbalancierte Paste/thermische Asymmetrie — AOI — Rework Heißluft; Pad-Länge −10 %, Kupfer ausbalancieren.

- Short unter µBGA: Zu viel Paste/Schablonenversatz — AXI — Reballing Hot-Bar; Step-Down-Schablone, SPI-Cpk erhöhen.

- Head-in-Pillow: Schlechte Benetzung/Verzug — AXI — TAL +10 s; Low-Void-Paste.

- Opens nach Thermoschock: Via-in-Pad-Absaugung — ICT/Thermozyklus — Mikrolot-Patch; Microvias füllen/kappern, Dog-Bone-Anker.

Metriken & KVP

- DPMO < 25, FPY > 99,8 %, Cp/Cpk ≥ 1,33 (Druck/Platzierung).

Echtzeit-SPC-Dashboards auf SPI/AOI; Kaizen, wenn Cpk < 1,25 oder False Calls > 300 ppm.

Compliance-Check

- IPC-A-610 H Klasse 2/3 dokumentiert & gezeichnet.

- IPC-J-STD-001-Prozessjournale ≥ 10 Jahre archiviert.

- ISO 9001:2015, Automotive-Linien IATF 16949.

- Lote rückverfolgbar (RoHS/REACH), SDS verfügbar.

Bottom Line: Eine gestaffelte SMT-Inspektionsstrategie (SPI → AOI → AXI → ICT/FCT → Umwelt) reduziert COPQ um bis zu 70 % gegenüber rein reaktiven Ansätzen.

Kostentreiber & Angebotskalkulation

1) Was bewegt ein SMT-Angebot wirklich?

| Kostenblock | Typischer Bereich* | Haupthebel |

|---|---|---|

| NRE/Setup (Schablone, Programm, Umrüsten) | 80–400 US-$ je Lauf | Jobs/Tag, Schablonentyp, Programmierzeit |

| PCB-Fertigung | 0,05–0,25 US-$/cm² (2-lagig); ×2–3 bei 6 Lagen | Größe, Lagenzahl, HDI, Finish |

| Bauteile (BOM) | 40–70 % der Gesamtkosten | Preise, Alternativen, Verfügbarkeit |

| Platzierkosten (Maschine + Arbeit) | 0,02–0,10 US-$/SMT-Punkt; 0,08–0,15 US-$/THT-Pin | Pitch, Feederwechsel, BGA-Anteil |

| Sonderprozesse | +10–30 % | Reballing, Underfill, Selektivwelle, Schutzlack |

| Test & Inspektion | 0,50–5,00 US-$/Board | ICT-Fixture, AXI-Tiefe, Burn-In |

| Logistik & Overhead | 5–15 % | Fracht, Zoll, Yield-Puffer |

*APAC-Durchschnitte 2025; Westeuropa/USA meist ×1,3–1,6.

2) Universelle Kostenformel

Gesamtkosten = (PCB + BOM) + (Setup/Losgröße) + (Σ SMT-Punkte × Punktpreis) + (Σ THT-Pins × Pinpreis) + Test & Diverses.

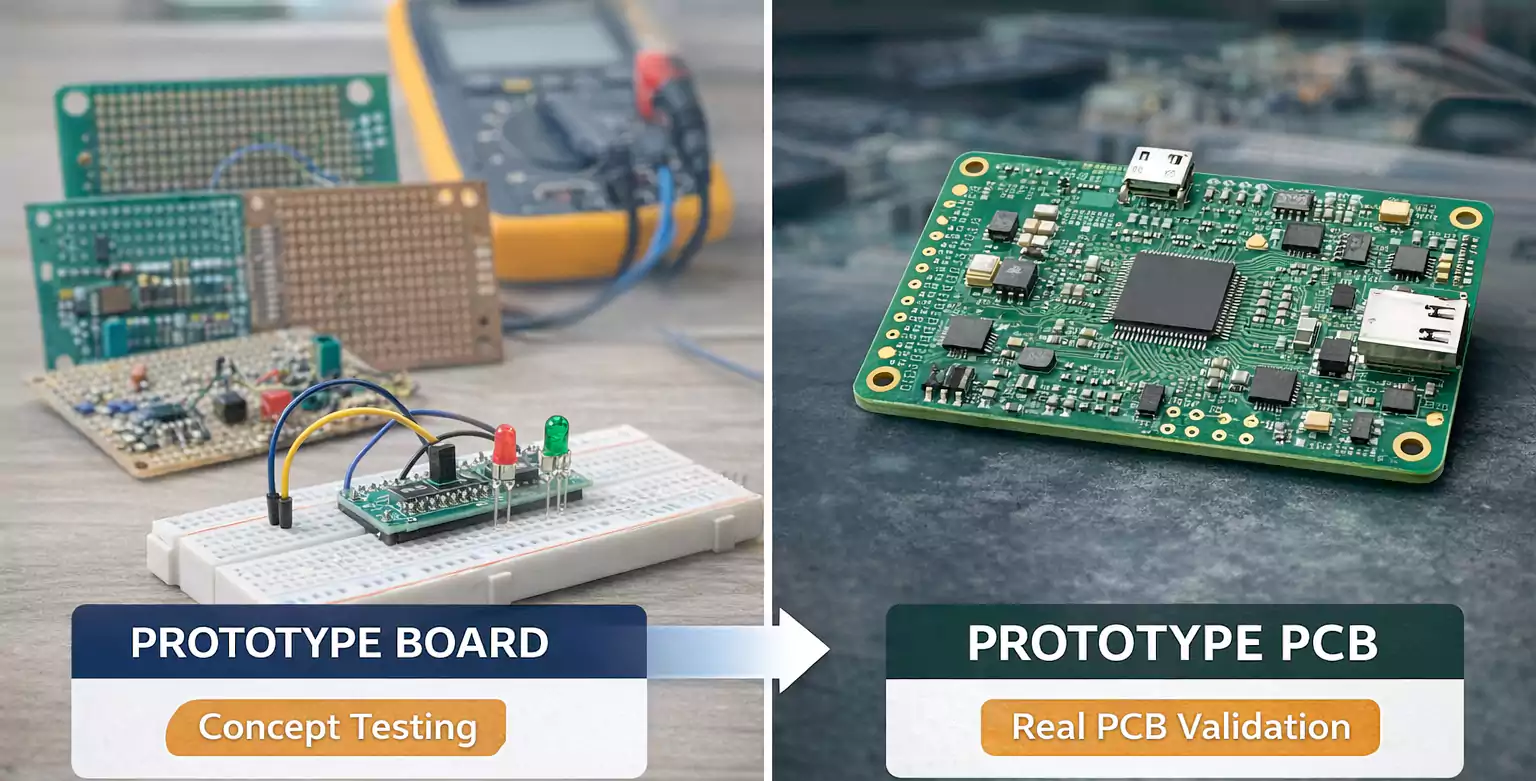

3) Zwei Szenarien

| Parameter | Prototyp | Mittelserie |

|---|---|---|

| Menge | 10 | 1 000 |

| Lagen/Größe | 4-lagig, 80 cm² | 4-lagig, 80 cm² |

| Bauteile/Board | 100 SMT, 5 THT | 100 SMT, 5 THT |

| PCB | 50 $ | 6 $ |

| BOM | 12 $ | 10 $ |

| Setup | 120 $ (einmalig) | 120 $ (amortisiert) |

| Platzierpreis | 0,12 $/Punkt | 0,03 $/Punkt |

| Test/Pack | 4 $ | 1,5 $ |

Kosten/Board:

- Prototyp: 50 + 12 + (120/10 = 12) + (100×0,12 = 12) + 4 = 90 US-$.

- Mittelserie: 6 + 10 + 0,12 + (100×0,03 = 3) + 1,5 = 20,62 US-$.

Takeaway: Setup & Platzierung dominieren bei kleinen Losen; ab 1 000+ Stück treibt die BOM die Kosten.

4) Fünf schnelle Sparhebel

- Panel-Effizienz: > 80 % Ausnutzung; weniger Starts → bessere Setup-Amortisation.

- BOM konsolidieren: Autorisierte Alternativen senken Preisvarianz um 10–15 %.

- Sonderprozesse minimieren: Via-in-Pad nur bei echter Dichtennot; +~10 % Overhead je Spezialschritt.

- Volumen-Breakpoints: ~20 % Stückpreis-Drop bei 250/500/1000 Stück durch Maschinen-Auslastung.

- Früh kalkulieren: Online-Kostenrechner mit Größe/Lagen/Count füttern, bevor das Schaltbild „eingefroren“ wird.

FAQ

Was unterscheidet SMT von THT?

SMT setzt Bauteile direkt auf Pads und ist vollautomatisiert, THT führt Drähte durch Bohrungen und lötet meist mit Welle/Hand. SMT → höhere Dichte, kleinere Boards, schnellere Fertigung; THT → stärkere mechanische Verankerung für große/hochbelastete Teile.

Wie klein sind heutige SMT-Bauteile?

State-of-the-Art-Linien platzieren routinemäßig 01005 (0,4×0,2 mm) und µBGA mit 0,3 mm Pitch mit Platziergenauigkeit besser als ± 30 µm — bei Type-6-Paste und SPI/AOI mit 10 µm/px.

Welche Dateien braucht ein genaues SMT-Angebot?

Vollständiges Gerber/ODB++ oder IPC-2581, XY-Centroid/Pick-and-Place, BOM mit freigegebenen Alternativen, Assembly Drawings (PDF) und Testanforderungen (ICT/FCT). Erwartete Menge & Zeitschiene beschleunigen die Kalkulation.

Wie lang sind typische Durchlaufzeiten?

Prototypen (≤ 20 Boards) in 3–5 Arbeitstagen, wenn Teile lagernd sind. Standardserien (100–5 000 Stk.) 10–15 Arbeitstage, abhängig von Bauteilverfügbarkeit & Schablonenfertigung.

Gibt es eine Mindestbestellmenge (MOQ)?

Viele EMS fertigen bereits 1–10 Stück (Prototyp), aber mit höheren Setup-Gebühren. Stückkosten fallen stark bei 100/250/1000+ Stk.

Wie senke ich SMT-Kosten?

> 80 % Panel-Nutzung, konsolidierte BOM mit gelisteten Alternativen, Sonderprozesse vermeiden, und Bestellungen an Volumenstufen koppeln.

Welche Inspektionen sichern Qualität?

Gestaffelt: SPI → AOI → (optional) AXI → ICT/Funktionstest. So werden > 99 % der Defekte vor Versand gefunden; Ziel DPMO < 25.

RoHS/REACH-Konformität?

Seriöse Anbieter verfolgen Lot-/Bauteil-Zertifikate bis zur Charge für RoHS 3/REACH. Verlangen Sie Konformitätszertifikate pro Lieferung.

Fazit & nächste Schritte

Sie haben jetzt eine 360°-Sicht auf SMT-Bestückung — von Grundlagen & Prozessfluss über Kostenmodelle & Lieferantenauswahl bis zum Ausblick mit 01005 und KI-gestützter Inspektion. Ob Sie das nächste Wearable schrumpfen, einen Industrie-Controller robust machen oder mit einem Startup-Prototyp zum Pitch sprinten: Mit konsequentem Design-for-Manufacture erreichen Sie:

- bis zu 30 % kleinere Leiterplatten durch engere Packages & ausgeglichene Kupferflächen,

- > 99,8 % First-Pass-Yield dank geschlossener Prüfketten SPI ⇒ AOI ⇒ ICT,

- 2–5× niedrigere Stückkosten, sobald Volumina die Schlüsselmarken 250 und 1000 überschreiten.