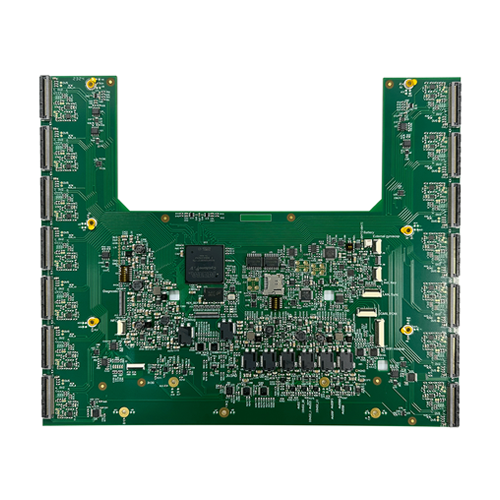

F1: Welchen Zweck hat die selektive Verwendung von ENIG und Hartgold?

A: Selektive Hartvergoldung wird in stark beanspruchten Kontaktbereichen wie Kantenverbindern eingesetzt, während ENIG andernorts zur Gewährleistung der Lötbarkeit und Kosteneffizienz eingesetzt wird.

F2: Was sind Blind- und Buried Vias und warum werden sie hier verwendet?

A: Blind Vias verbinden äußere mit inneren Lagen, Buried Vias hingegen nur innere Lagen. Sie reduzieren die Anzahl der Verbindungswege zwischen den Lagen und ermöglichen so eine höhere Dichte ohne Vergrößerung der Platine.

F3: Können Sie die Impedanzkontrolle für diese Leiterplatte unterstützen?

A: Ja. Die Impedanzkontrolle kann anhand der bereitgestellten Daten zu Stapelaufbau und Leiterbahnbreite/-abstand implementiert werden. Bitte reichen Sie Ihre Impedanzanforderungen mit Ihrem Design ein.

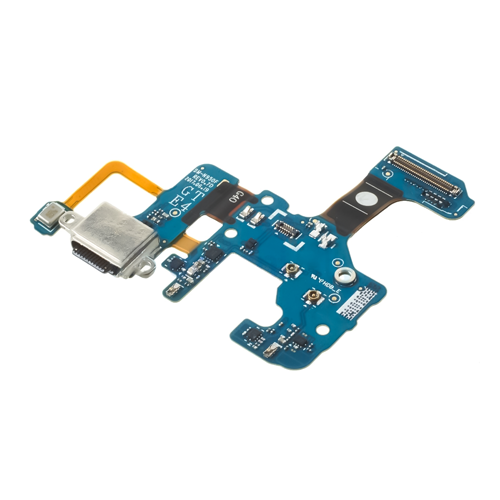

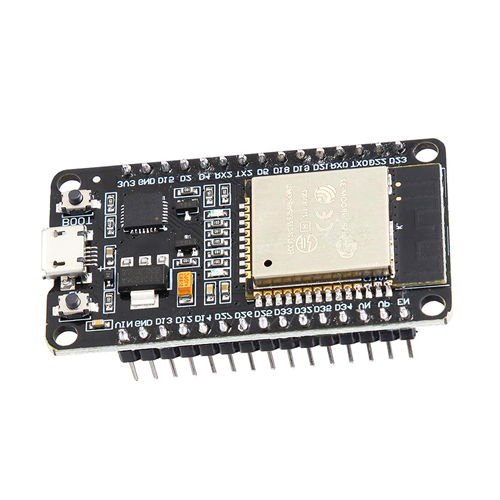

F4: Für welche Anwendungen eignet sich diese HDI-Leiterplatte am besten?

A: Diese Leiterplatte eignet sich ideal für den Einsatz in Mobilgeräten, HF-Modulen, Hochgeschwindigkeitscomputern, medizinischen Instrumenten und Elektronik in der Luft- und Raumfahrt, wo kompakte Bauweise und Signalintegrität entscheidend sind.

F5: Wie hoch ist die Mindestbestellmenge (MOQ)?

A: Die Mindestbestellmenge hängt von den spezifischen Produktionsanforderungen ab. Wir bieten Prototypen in kleinen Stückzahlen und Großserienproduktion an. Bitte kontaktieren Sie uns für ein individuelles Angebot.