Einleitung: Warum ein systematischer Prozess entscheidend ist

Wer nach dem Begriff „tecnograph process PCB“ sucht, möchte eine strukturierte, lückenlose Übersicht darüber, wie aus einer blanken Leiterplatte ein zuverlässiges Fundament für die Baugruppenmontage wird. Ein sauber abgestimmter Fertigungsprozess reduziert Prototypen-Fehlversuche, stabilisiert Lieferzeiten und verhindert unangenehme Überraschungen bei der Wareneingangskontrolle. Dieser Leitfaden beschreibt den modernen, produktionsreifen Herstellungsablauf einer Leiterplatte – Schritt für Schritt, mit Fokus auf Relevanz, toleranzkritische Parameter und Daten, die für ein fehlerfreies Ergebnis beim ersten Durchlauf notwendig sind. Die Inhalte richten sich an Entwicklungsingenieure, Beschaffungsteams und Start-ups, die praktische Klarheit ohne unnötiges Fachkauderwelsch benötigen.

Prozessübersicht: Von den Daten zur Auslieferung

Ein robuster Tecnograph-Prozess folgt einem klaren Ablauf:

CAM & DFM → Innenlagen-Belichtung und Ätzung → Laminierung → Bohren (mechanisch/laser) → PTH und Kupfergalvanisierung → Außenlagen-Belichtung und Ätzung → Lötstopplack → Siebdruck/Kennzeichnung → Oberflächenfinish → Elektrischer Test und Inspektion → Nutzen-Trennung, Reinigung, Verpackung

Zwei Faktoren halten diesen Prozess zusammen:

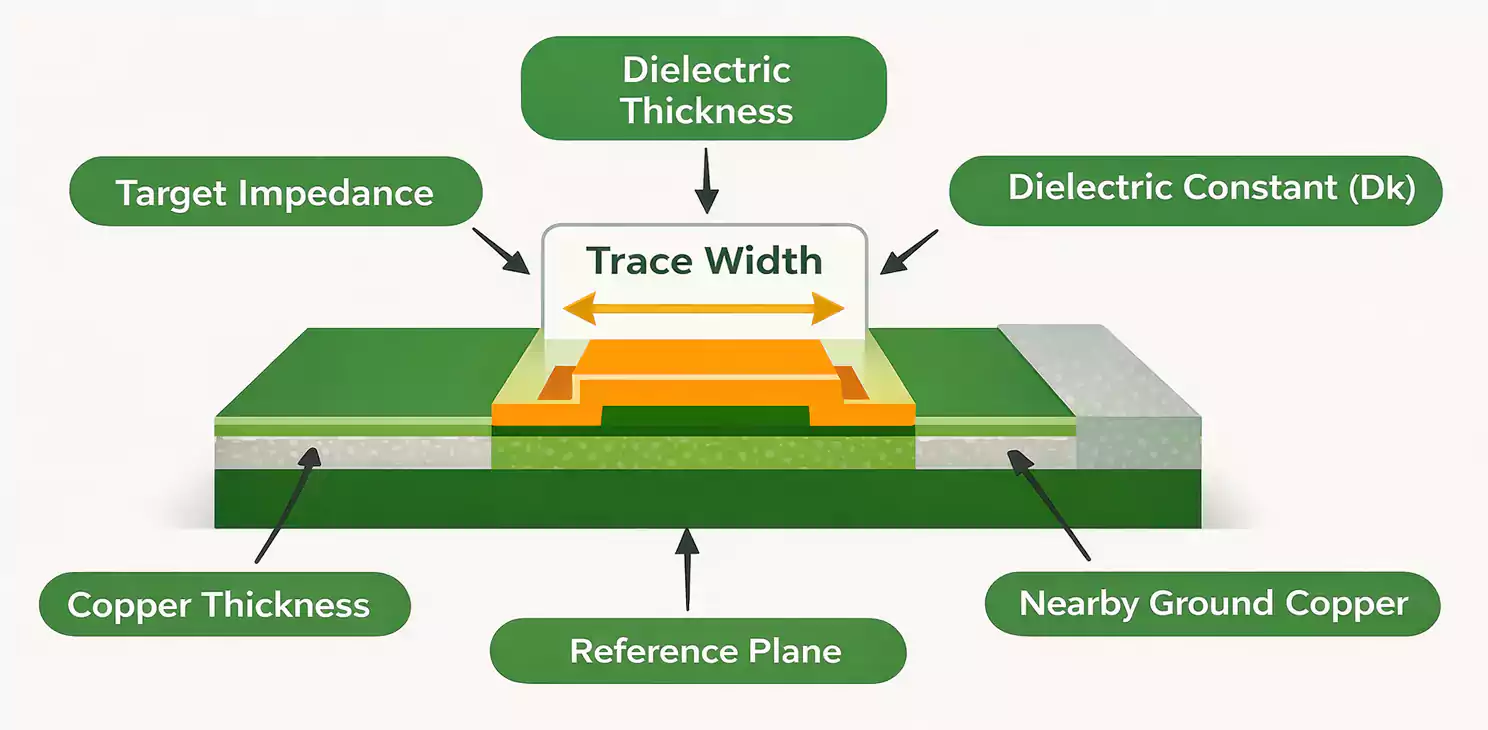

- Klare, eindeutige Fertigungsdaten

- Abgestimmte Herstellungsziele hinsichtlich Leiterbahnbreite/-abstand, Via-Strategie, Impedanz und Oberflächenbehandlung

Sind diese definiert, wird der gesamte Prozess planbar und reproduzierbar.

Front-End-Engineering: CAM und DFM auf Anhieb korrekt

Das Front-End-Engineering wandelt Ihre Design-Dateien in ein fertigungsgerechtes Produkt um.

Daten & Formate:

Übliche Formate sind Gerber X2, ODB++ oder IPC-2581. Ergänzen Sie: ein sauberes Lagenaufbau-Diagramm, Materialangaben, Bohrpläne, Impedanzziele mit Toleranzen sowie ein Testnetz. Bei Montageprojekten fügen Sie bitte Pick-&-Place-Daten und ein Stücklistenfile (BOM) bei.

Nutzenbildung (Panelization):

Eine gut geplante Nutzenbildung steigert Ausbeute und Durchsatz. Fügen Sie Aufspannränder, globale Fiducials, Couponbereiche, und eine Strategie zur Nutzen-Trennung (V-Cut oder Fräsen) hinzu. Für Impedanz-kritische Designs: Testcoupons nicht vergessen.

Kritische Toleranzen:

Passen Sie minimale Leiterbahnbreiten und -abstände an die Kupferdicke an. Berücksichtigen Sie Bohr-Toleranzen und Registriergenauigkeit. Definieren Sie Impedanzfenster, die mit dem Lagenaufbau und dem galvanischen Aufbau realistisch umsetzbar sind. HDI, feine BGAs oder strenge Impedanzziele müssen unbedingt mit dem Hersteller vorab abgestimmt werden.

Materialien und Lagenaufbau

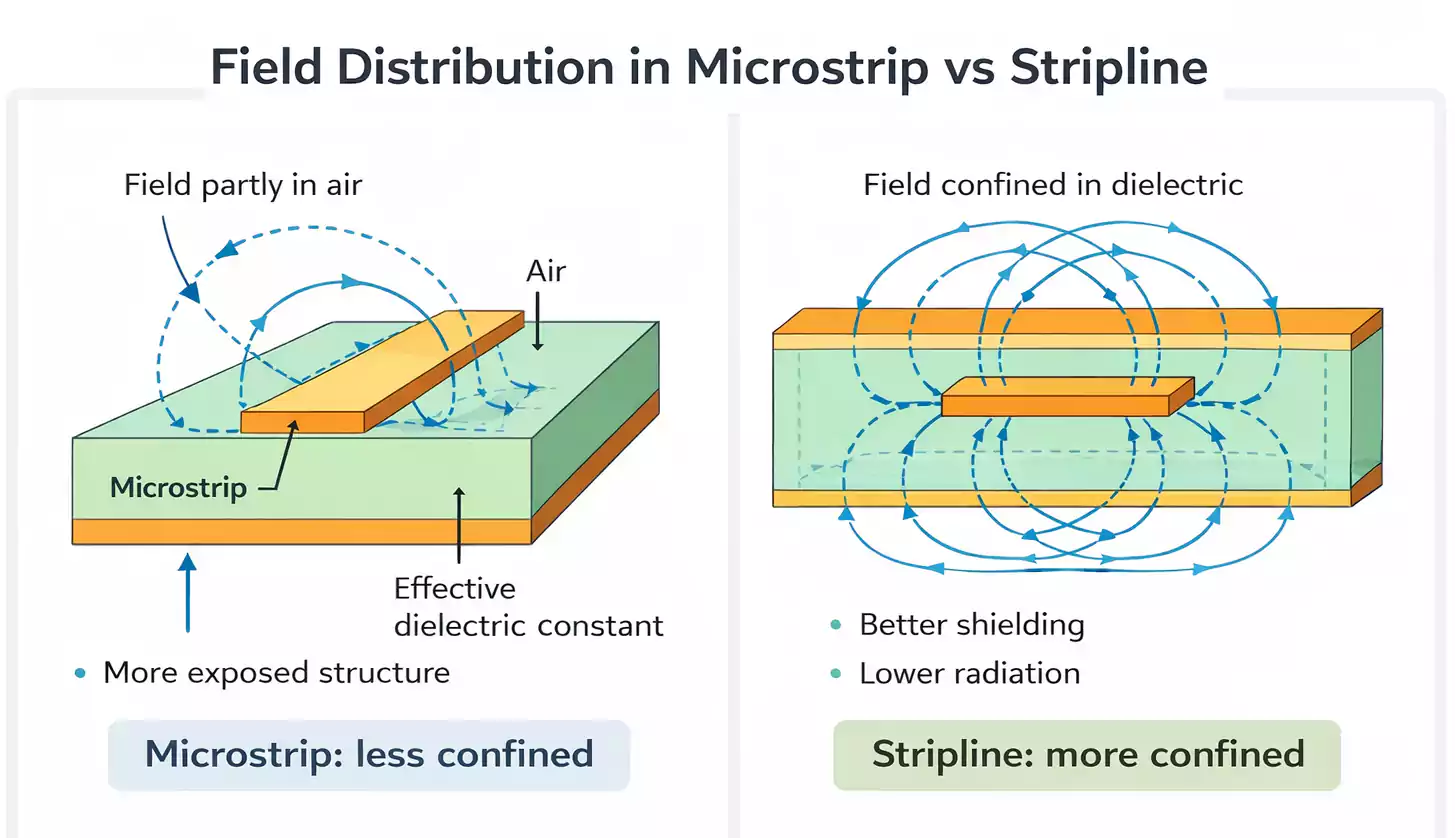

Der Lagenaufbau ist die „DNA“ Ihrer Leiterplatte. Er beeinflusst Impedanz, Signalverlust, Ebenheit und thermisches Verhalten.

Basismaterialien:

Für Standard-Digitaldesigns sind FR4-Typen mit angepasstem Tg und CTE geeignet. Highspeed- und HF-Designs benötigen Materialien mit geringem Dk/Df-Wert. Dokumentieren Sie immer Dk/Df bei der tatsächlichen Frequenz – nicht nur bei 1 MHz.

Kupferdicken:

Außenlagen starten oft dünn und werden galvanisch aufgebaut. Innenlagen verwenden gewalzte oder elektrolytisch abgeschiedene Kupferfolien. Dickere Kupferlagen erhöhen Stromtragfähigkeit, beeinflussen aber die Ätzgeometrie und Registrierung. Entsprechende Anpassungen im Design sind nötig.

Symmetrie & Verzug:

Ein symmetrischer Aufbau und ausgewogene Kupferverteilung verhindern Biegung, Verzug oder Delamination.

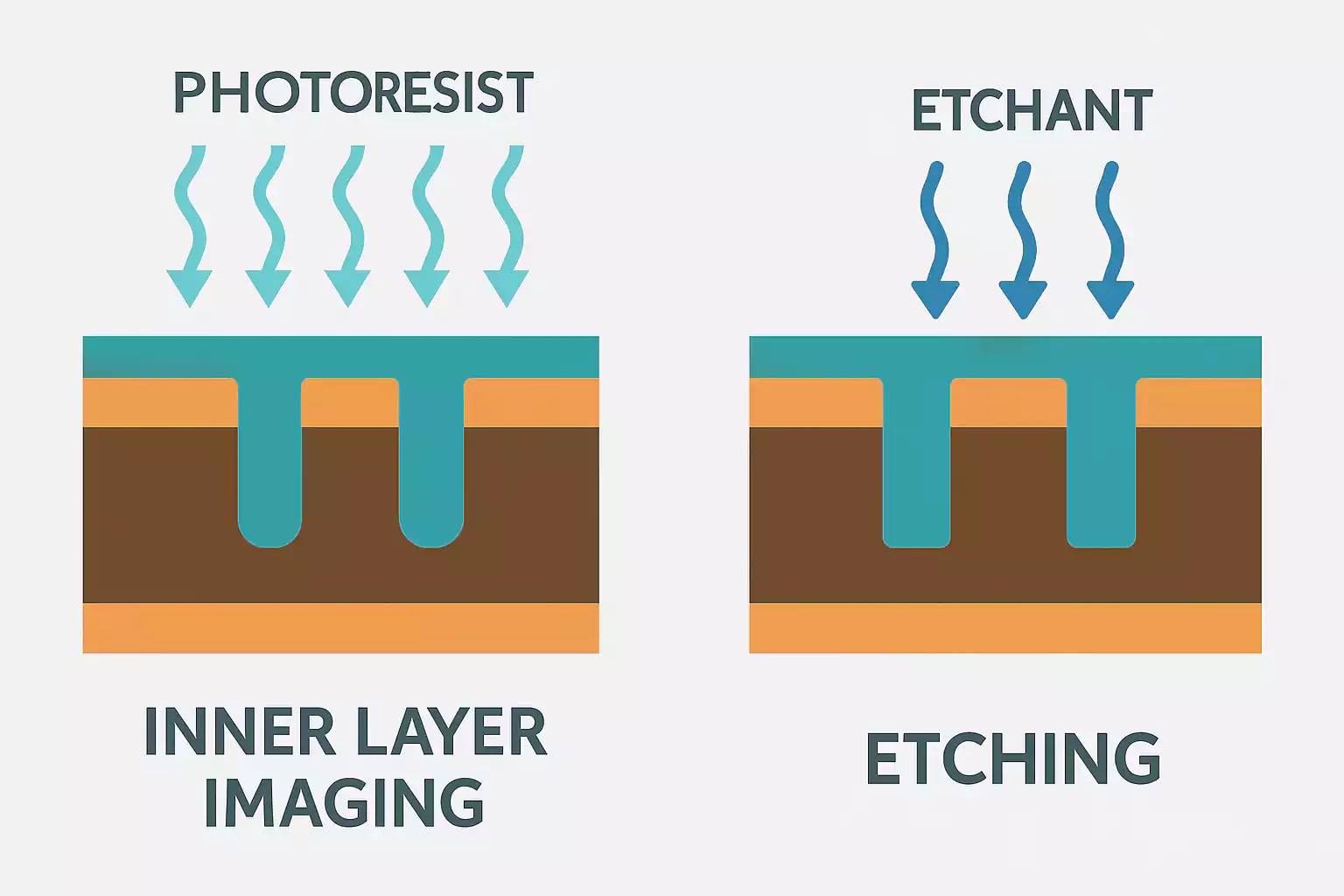

Innenlagen-Belichtung und Ätzen

Innenlagen definieren versteckte Leiterzüge und Masseflächen vor der Laminierung.

Belichtung:

Fotoresist wird auflaminiert und per LDI (Laser Direct Imaging) belichtet. Danach wird das gewünschte Leiterbild entwickelt. Eine gute Artwork-Kompensation berücksichtigt Schrumpfung oder Wachstum.

Ätzen:

Die freigelegten Kupferbereiche werden chemisch entfernt. Ätzrate hängt von Temperatur, Chemikalienkonzentration und Fördergeschwindigkeit ab. Unterätzungen müssen in den Designtoleranzen einkalkuliert werden. Danach erfolgt eine AOI (Automatic Optical Inspection).

Worauf achten:

Übermäßiges Ätzen schwächt die Leiterbahnen, Unterätzung lässt Kupferreste stehen. Sauberkeit ist kritisch – Rückstände im Laminat sind langfristig fehlerträchtig.

Laminierung

Die Innenlagen werden unter Hitze und Druck mit Prepregs verpresst.

Harzfluss und Füllung:

Das Harz muss Kavitäten, Webstrukturen und eventuell vergrabene Vias füllen. Zu viel Fluss verschiebt Features, zu wenig erzeugt Lufteinschlüsse.

Ausrichtung & Ebenheit:

Presszyklen, Fixiermethoden und Werkzeuge sorgen für exakte Lagenregistrierung. Symmetrischer Aufbau minimiert Z-Ausdehnung und Verzug. Bei HDI-Mehrfachpressungen muss die Reihenfolge der Microvia-Erzeugung klar geplant werden.

Thermomechanik:

Wählen Sie Materialien mit passendem Tg und CTE für Ihre Reflow-Profile und Einsatzumgebungen. Hoher Tg verhindert Verformungen bei Lötprozessen.

Bohren und Via-Strategien

Via-Typen:

- Durchkontaktierungen: robust, kosteneffizient

- Blind/Buried Vias: sparen Platz und Layerübergänge

- Laser-Microvias: ideal bei BGAs ≤ 0,1 mm, in gestaffelter oder gestapelter Form

Prozesskontrolle:

Beim mechanischen Bohren: richtige Vorschubgeschwindigkeit und Drehzahl. Beim Lasern: schonende Energiezufuhr, keine Kupferbeschädigung. Achten Sie auf genügend Ringbreite zur Toleranzaufnahme beim Galvanisieren.

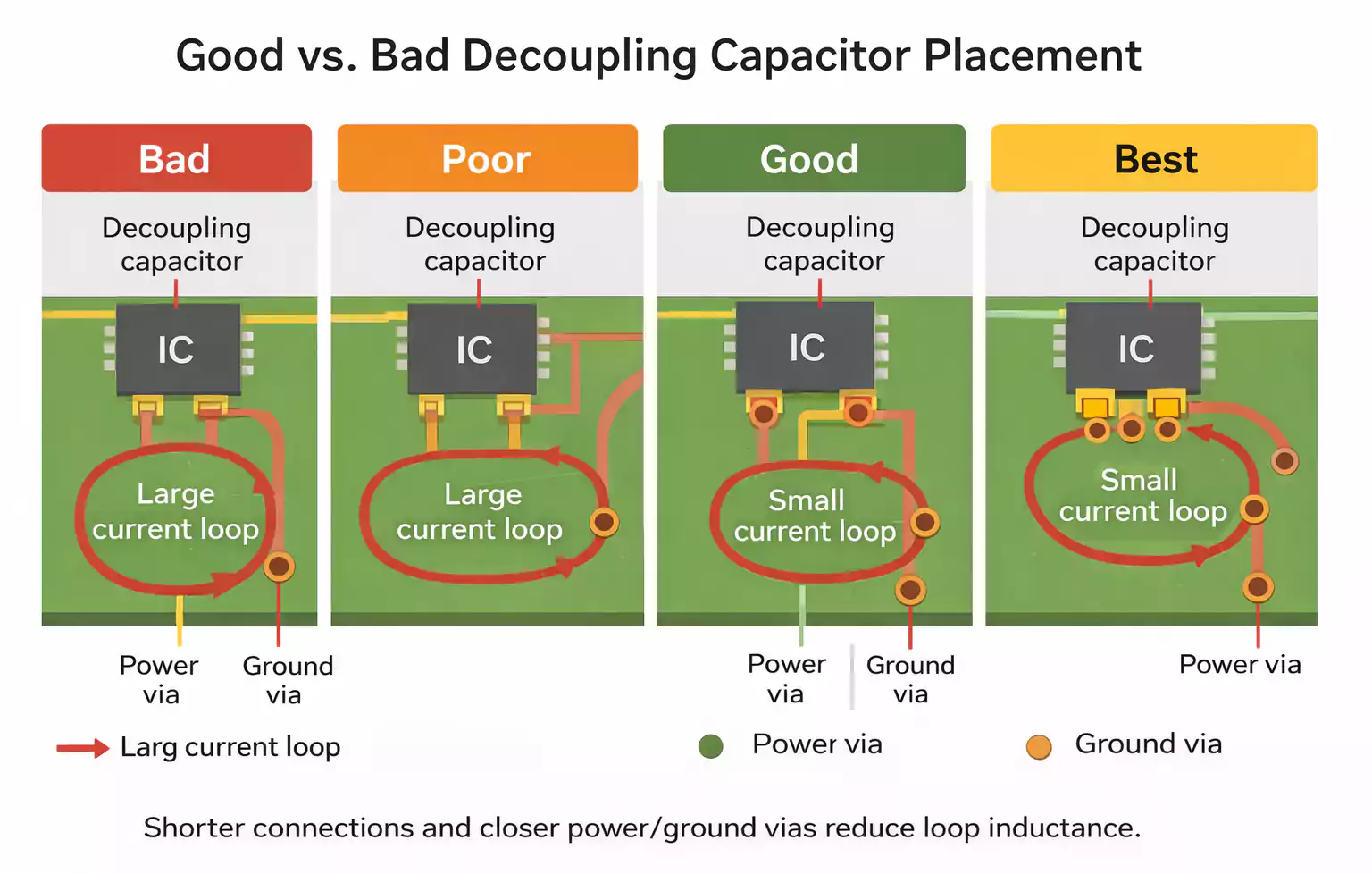

Design-Kompromisse:

Via-in-Pad spart Fläche, erhöht SI/PI, benötigt aber Kupferfüllung und Planarisierung. Tenting oder Capping beeinflussen Lötbarkeit, Reinigung und Testbarkeit – also frühzeitig im DFM festlegen.

PTH und Kupfer-Galvanisierung

Nach dem Bohren sind die Lochwände unleitend. PTH macht sie elektrisch leitfähig.

Ablauf:

Entschmieren → Aktivierung mit Palladium → chemische Kupferabscheidung → galvanischer Kupferaufbau (innen + außen). Optional: additive Plattierung für Pads.

Qualitätsmetriken:

Gleichmäßige Kupferdicke = zuverlässige thermische Zyklenfestigkeit. Überwacht wird: Stromdichte, Rührtechnik, Badqualität. Mikroschliffe liefern Messwerte zu Verteilung, Rissen oder Hohlräumen.

Risiken:

„Dog-boning“ an Padkanten, Knotenbildung durch Stromspitzen – beides beeinflusst Impedanz und Lötverhalten negativ.

Außenlagen-Belichtung und Ätzen

Der Prozess entspricht dem der Innenlagen, jedoch mit Fokus auf Endimpedanz und Plattierungstoleranzen.

Belichtung & Musterplattierung:

Dry-Film-Resist erzeugt das Layout. Wichtige Pads/Leiterbahnen werden ggf. zusätzlich plattiert.

Finales Ätzen:

Entfernung freiliegenden Kupfers zur Endstruktur. CAM-Kompensation ist hier besonders wichtig.

Fehlervermeidung:

AOI prüft auf Rückstände, Überplattierungen, Unterätzung – unbedingt vor Lötstopplack beheben.

Lötstoppmaske & Siebdruck

Maskenstrategie:

Aussparungen um Pads mit ausreichender Toleranz. Bei feinen Abständen: Mindestabstand Maskensteg einhalten. Bei BGA: Maskendefiniert oder kupferdefiniert abstimmen. Via-Strategie: geschlossen, offen oder gekapselt.

Aushärtung & Ausrichtung:

Exakte Positionierung verhindert Abdeckung aktiver Flächen oder Kupferfreilegung.

Druck:

Siebdruck liefert Bauteilkennzeichnungen, Polmarkierungen und Rückverfolgbarkeit. Keine Tinte auf Lötpads.

Auswahlhilfe für Oberflächenfinish

| Finish | Vorteile | Anwendung |

|---|---|---|

| HASL / LF-HASL | robust, günstig | weniger geeignet für Feinstrukturen |

| OSP | plan, günstig | begrenzte Lagerfähigkeit |

| ENIG | plan, korrosionsfest | ideal für BGA & Feinstrukturen |

| ENEPIG | bondbar, langlebig | höhere Kosten, höchste Qualität |

| Imm. Zinn/Silber | gut lötbar | empfindlich bei Lagerung/Handhabung |

Wählen Sie entsprechend Taktzeit, Empfindlichkeit der Bauteile, Lötverfahren und Budget.

Tests & Prüfverfahren

Elektrischer Test:

- Flying-Probe: flexibel für Prototypen

- Nadelbett (Fixture): schnell & ideal für Serie

AOI & Röntgen:

Prüfen Leiterbild, Maskenregistrierung und ggf. Via-Integrität (vor Bestückung).

Design for Test (DFT):

Testpunkte, Abstände für Prüfspitzen, Netlist-Abgleich mit CAM. Impedanz-Coupons für TDR-Prüfungen beilegen.

Nutzen-Trennung, Reinigung & Verpackung

Nutzen-Trennung:

V-Cut = effizient, aber geradlinig. Fräsen = flexibler, aber mehr Aufwand.

Reinigung:

Ionische Verunreinigungen entfernen. Auch für sofort zu bestückende Boards sinnvoll.

Verpackung:

Feuchtigkeitsbarriere, Trockenmittel, Indikatoren, klar beschriftet mit Lot, Datum, Revisionsstand. Hinweise für OSP/Silber beilegen.

Drei typische Szenarien und Empfehlungen

Prototypen & Kleinserien:

ENIG oder OSP, Flying-Probe-Test, einfache Nutzenstruktur. Designregeln konservativ halten.

Serienfertigung & Kostenoptimierung:

Hohe Nutzenauslastung, fixture-basierte Tests, OSP oder LF-HASL bei kurzer Lagerung. Stabiler Stack-up = konstante Impedanz.

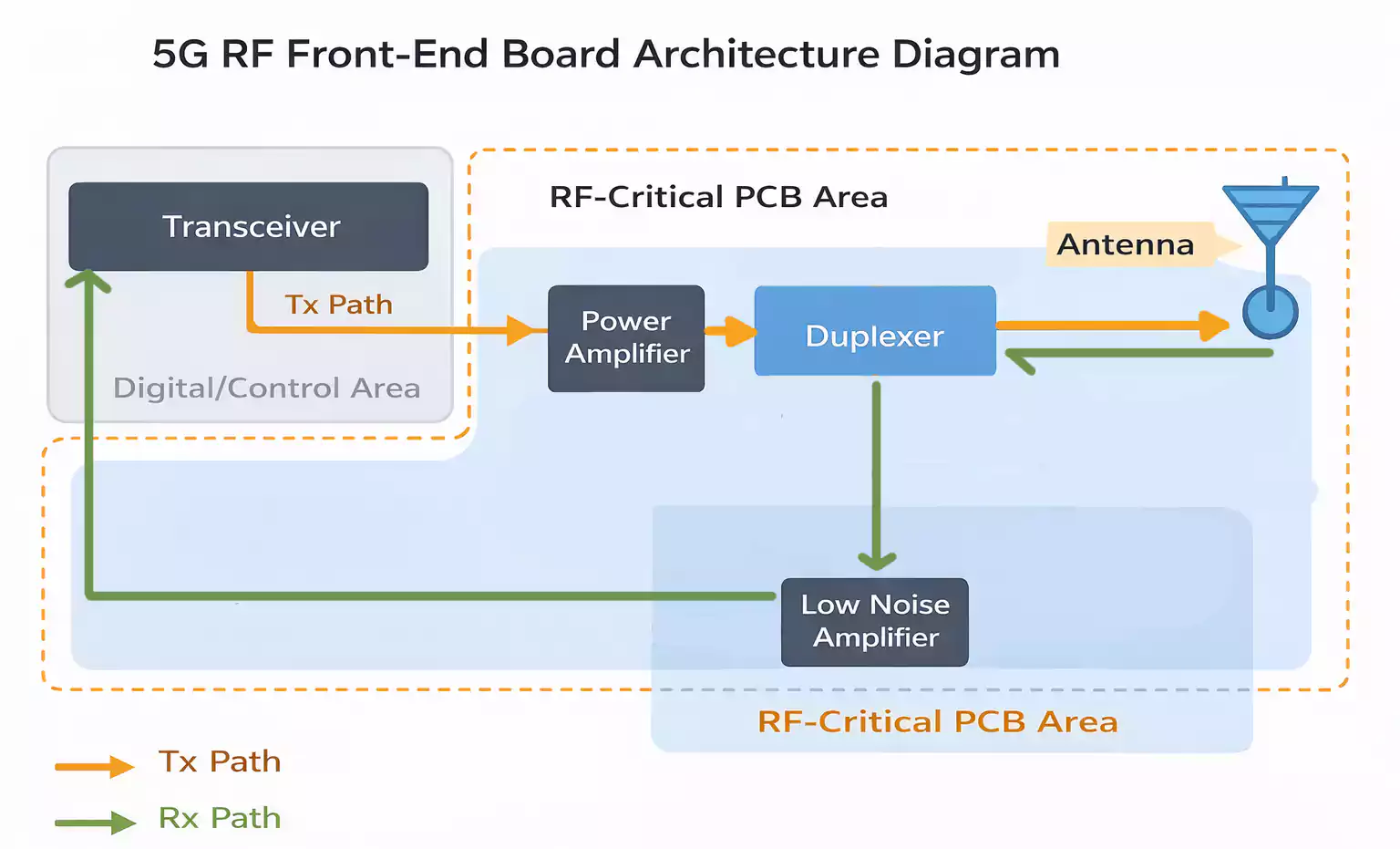

High-Speed/RF/HDI:

Low-Loss-Material, kontrollierte Kupferrauheit, realistische Microvia-Geometrie. Impedanz-Coupons & Materialfreigaben notwendig.

Fazit & nächste Schritte

Ein strukturierter Tecnograph PCB-Prozess verwandelt Designvorgaben in zuverlässige Hardware: passendes Material, kontrollierte Ätzung, sichere Vias, geeignete Oberflächen, durchdachte Teststrategie. Klare Daten und realistische Toleranzen verbessern Ausbeute, verkürzen Durchlaufzeiten und vermeiden späte Nacharbeiten.

Bereit für die Umsetzung? Senden Sie uns Ihre Daten für eine Fertigungsbewertung und ein schnelles, präzises Angebot.