Einleitung

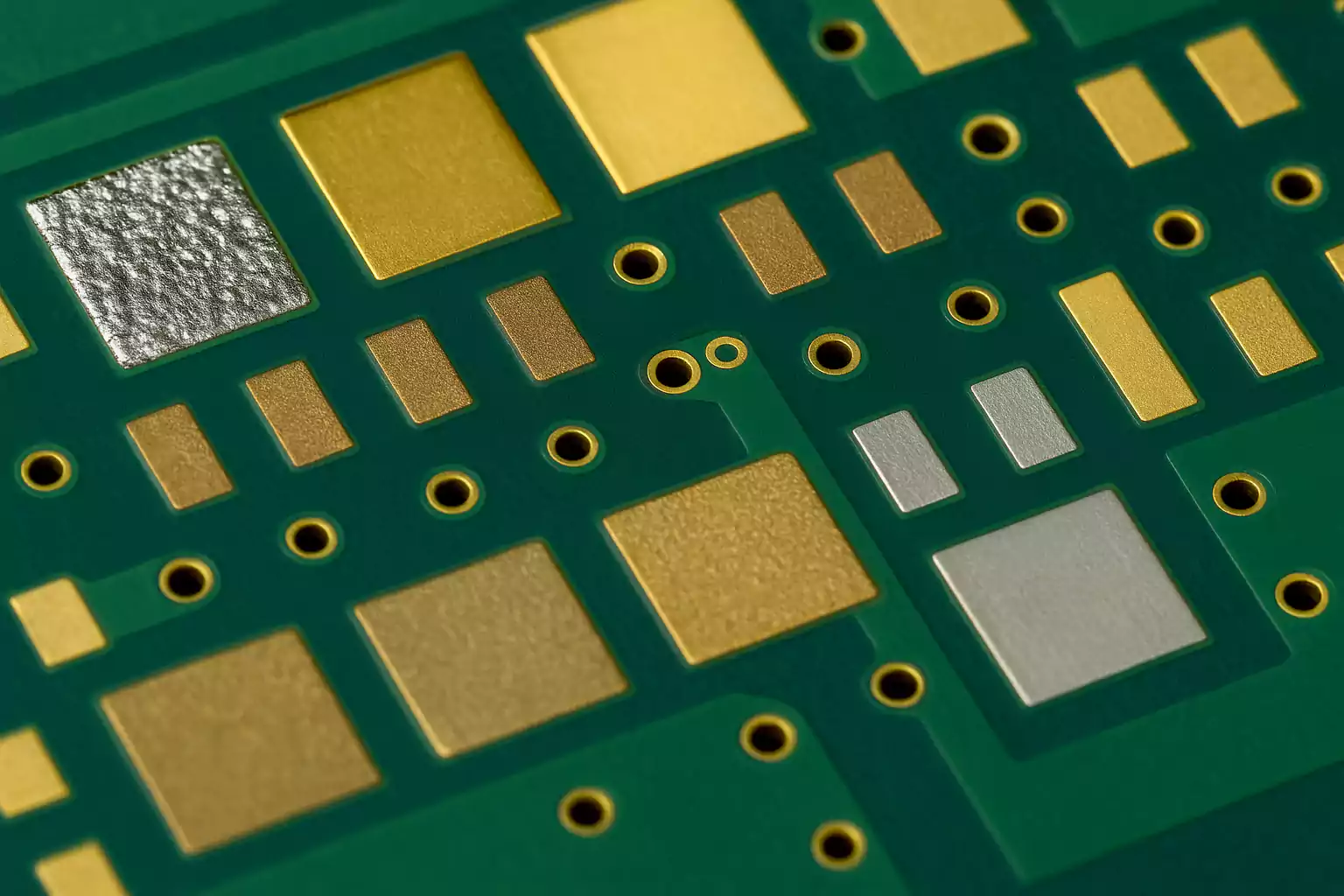

PCB-Plating ist entscheidend, um zuverlässige elektrische Verbindungen und robuste Oberflächen in der Leiterplattenfertigung sicherzustellen. Es erfüllt zwei Kernfunktionen: das Bilden leitfähiger Wege in Durchkontaktierungen sowie das Aufbringen von Oberflächenfinishes, die freiliegendes Kupfer schützen und die Lötbarkeit sichern.

In diesem Leitfaden erfahren Sie, wie die Kupferbeschichtung durch Bohrungen funktioniert, worin sich chemisches (electroless) und galvanisches (electrolytic) Plating unterscheiden und wie Sie das passende Oberflächenfinish—z. B. HASL, ENIG, OSP oder Immersion Silver—für Ihre Anwendung auswählen.

Ganz gleich, ob Sie Leiterplatten entwickeln, beschaffen oder bestücken: Ein solides Verständnis dieser Plating-Prozesse hilft, Leistung, Lebensdauer und Kosten zu optimieren.

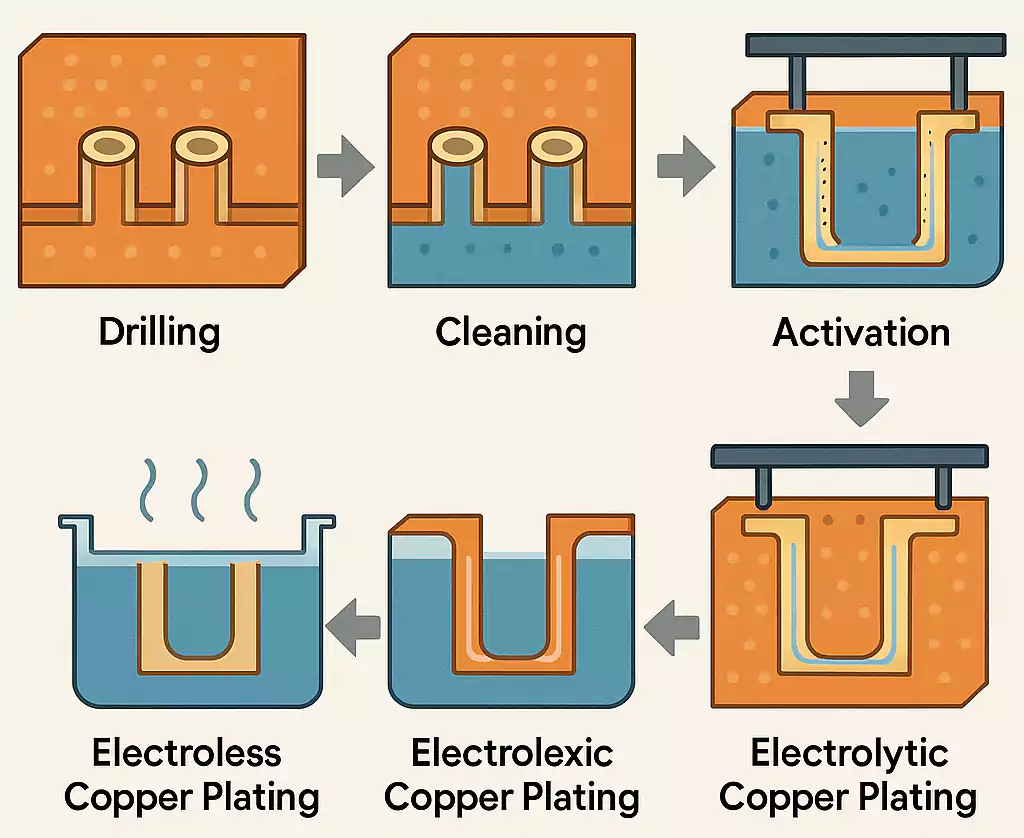

Überblick: Durchkontaktierte Kupferbeschichtung (Through-Hole Copper Plating)

Die Kupferbeschichtung durch Bohrungen ist ein kritischer Schritt in der Fertigung mehrlagiger Leiterplatten. Sie stellt zuverlässige elektrische Verbindungen zwischen den Lagen sicher. Dabei wird eine leitfähige Kupferschicht in den gebohrten Löchern (Vias) der Leiterplatte abgeschieden, sodass Strom von einer Lage zur anderen fließen kann. Der folgende Abschnitt beschreibt den gesamten Ablauf—von der Vorbehandlung bis zur endgültigen Kupferabscheidung—samt zentraler technischer Aspekte für optimale Ergebnisse.

1. Reinigen und Desmearing

Bevor Kupfer abgeschieden werden kann, müssen die frisch gebohrten Löcher sorgfältig gereinigt werden. Beim mechanischen Bohren entstehen häufig Rückstände, Harzschmiere und Oxide, die die Haftung des Platings beeinträchtigen.

- Desmearing: Per Plasma oder chemischer Behandlung (z. B. Permanganat) werden Harzreste von den Lochwänden entfernt.

- Oberflächenvorbereitung: Innenlagen und Lochwände werden mikrogeätzt, um die Haftung und Benetzbarkeit für den nachfolgenden Plating-Prozess zu verbessern.

Diese Phase ist entscheidend, damit die chemische Kupferschicht gleichmäßig haftet und Hohlstellen oder Delaminationen vermieden werden.

2. Chemisches Kupfer (Electroless Copper Plating)

Auch als PTH-Aktivierung (Plated Through Hole) bekannt: Eine dünne, leitfähige Kupferschicht wird ohne elektrischen Strom in nichtleitenden Bohrungen abgeschieden.

- Katalysatoraktivierung: Die Leiterplatte wird in eine palladiumhaltige Lösung eingebracht, um die isolierenden Oberflächen zu aktivieren.

- Chemische Abscheidung: Kupferionen werden aus der Lösung reduziert und gleichmäßig auf den Lochwänden und freiliegenden Kupferflächen abgeschieden.

Typische Schichtdicken liegen bei 0,5–1,0 µm. Diese Grundschicht ist für das anschließende galvanische Plating unerlässlich, um zuverlässige Vias sicherzustellen und Unterbrechungen in Multilayer-PCBs zu vermeiden.

3. Galvanisches Kupfer (Electrolytic Copper Plating)

Nach der leitfähigen Grundschicht wird mit galvanischer Abscheidung die Kupferdicke in den Lochwänden und auf der Leiterplattenoberfläche aufgebaut.

- Galvanikaufbau: Die Leiterplatte wird an eine Kathodenschiene angeschlossen und in eine saure Kupfersulfat-Lösung getaucht.

- Zusätze im Bad: Glanzbildner, Egalisierer und Suppressoren sorgen für eine gleichmäßige Abscheidung und hohe Oberflächenqualität.

- Stromeintrag: Geregelt eingespeister Gleichstrom bewirkt die Abscheidung von Kupferionen vom Anodenmaterial auf die Leiterplatte.

Die galvanisch abgeschiedene Kupferschicht beträgt üblicherweise 18–25 µm (0,7–1,0 mil) und erfüllt damit IPC-6012, Class 2/3. Für hochzuverlässige Designs kann zusätzliche Dicke erforderlich sein.

4. Wrap-Plating (Kantenüberdeckung)

Zur Erhöhung der elektrischen Zuverlässigkeit—vor allem bei Via-in-Pad oder HDI-Strukturen—wird die Beschichtung so geführt, dass das Kupfer vom Lochzylinder auf die Pad-Oberfläche „herumzieht“.

- IPC-6012B fordert eine Kupferüberdeckung von mindestens 0,025 mm (1 mil) von der Lochkante auf die umliegende Lötfläche.

- Richtig ausgeführtes Wrap-Plating verbessert die Lötstellenfestigkeit und reduziert das Risiko des Pad-Ablösens bei Bestückung oder Rework.

5. Qualitätssicherung und Dickenprüfung

Konstante Kupferdicken und vollständige Abdeckung sind für Leistung und Lebensdauer essenziell. Gängige Prüfmethoden:

- Mikroschliffe: Querschliff-Analyse zur Verifizierung von Gleichmäßigkeit und Dicke.

- Röntgenfluoreszenz (XRF): Zerstörungsfreie Messung der Kupferdicke über die gesamte Leiterplatte.

- Haftprüfung: Sicherstellung, dass die Schichten fest mit dem Substrat verbunden sind und thermische sowie mechanische Belastungen aushalten.

Umfassender Leitfaden zu PCB-Oberflächenfinishes (Surface Finishes)

Oberflächenfinishes schützen freiliegende Kupferpads und -leiterbahnen, erhalten die Lötbarkeit und verhindern Oxidation. Die richtige Wahl beeinflusst Ausbeute, Langzeitzuverlässigkeit und Kosten unmittelbar. Im Folgenden werden die gängigsten Finishes hinsichtlich Eigenschaften, Einsatzfällen, Vor-/Nachteilen und Auswahlkriterien verglichen.

1) HASL (Hot Air Solder Leveling)

Kurzprofil: Die Leiterplatte wird in flüssiges Lötzinn getaucht und mit Heißluftmessern abgezogen/ebenisiert.

Merkmale:

- In bleifreier und bleihaltiger Variante verfügbar

- Gute Lagerfähigkeit und Lötbarkeit

- Geeignet für THT und große Bauteile

Einschränkungen:

- Unregelmäßige Ebenheit; ungeeignet für Feinraster-SMD

- Thermischer Schock während der Verarbeitung

- Nicht empfohlen für Hochfrequenz oder strenge Impedanzkontrolle

Ideal für: Standard-Anwendungen, THT-Boards, kostenkritische Projekte

2) OSP (Organic Solderability Preservative)

Kurzprofil: Eine dünne organische Schutzschicht (meist Azole) verhindert Kupferoxidation bei gleichzeitig sehr guter Lötbarkeit.

Merkmale:

- Sehr flache, glatte Oberfläche—ideal für Feinraster und BGA

- Bleifrei, RoHS-konform

- Exzellent für eine einmalige Reflow-Lötung

Einschränkungen:

- Kürzere Lagerfähigkeit (6–12 Monate)

- Weniger robust für mehrere Reflow-Zyklen/hohe Temperaturen

- Empfindlich gegen Kratzer—sorgfältige Handhabung nötig

Ideal für: Großserien-SMT mit einfachem Reflow; Unterhaltungselektronik

3) Immersion Tin (ISn)

Kurzprofil: Chemisch abgeschiedene Zinnschicht auf Kupfer—bleifrei, flach und lötbar.

Merkmale:

- Sehr flache Oberfläche mit guter Lötbarkeit

- Geeignet für Press-Fit

- RoHS-konform

Einschränkungen:

- Risiko von Zinn-Whiskern (Kurzschlussgefahr)

- Nicht ideal für mehrere Bestückungszyklen

- Empfindlich in Handhabung und Lagerung

Ideal für: Telekom, Backplanes, designs mit vielen Steckverbindern

4) Immersion Silver (IAg)

Kurzprofil: Dünne Silberschicht auf Kupfer mit hervorragender Leitfähigkeit und Planarität.

Merkmale:

- Sehr gut für HF-Signale und High-Speed-Digital

- Exzellente Benetzung und Ebenheit

- Kostengünstiger als Gold-basierte Finishes

Einschränkungen:

- Anlaufempfindlich bei unsachgemäßer Lagerung

- Mitunter Stickstoff-Atmosphäre beim Reflow empfohlen

- Silbermigration bei hoher Luftfeuchte möglich

Ideal für: RF-Boards, High-Speed-Digitalschaltungen, feinrasterige SMT

5) ENIG (Electroless Nickel Immersion Gold)

Kurzprofil: Zweilagiges Finish mit Nickel-Sperrschicht (gegen Kupferdiffusion) und dünner Goldoberlage für Lötbarkeit.

Merkmale:

- Sehr flach—ideal für BGA, QFN, HDI

- Lange Lagerfähigkeit (12+ Monate)

- Geeignet für mehrere Reflow-Zyklen

Einschränkungen:

- Teurer als OSP/HASL

- Risiko des „Black Pad“-Defekts bei ungenauer Prozessführung

- Lötstellen tendenziell spröder als bei Zinn-Finishes

Ideal für: Hochzuverlässige, hochdichte Anwendungen in Luft-/Raumfahrt, Medizintechnik, Telekom

6) ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold)

Kurzprofil: Zusätzliche Palladiumschicht zwischen Nickel und Gold—bessere Oxidationsfestigkeit, geringeres „Black-Pad“-Risiko.

Merkmale:

- Hervorragend für Drahtbonden (Gold/Aluminium)

- Exzellente Korrosionsbeständigkeit

- Lange Lagerfähigkeit und Lötbarkeit

Einschränkungen:

- Höhere Kosten (Edelmetall-Mehrlagen)

- Präzise Prozesskontrolle erforderlich

Ideal für: Sicherheitskritische Elektronik, Drahtbonden, Militär & Aerospace

7) Auswahlhilfe Oberflächenfinish (Kurzvergleich)

| Finish | Ebenheit | Kosten | Lagerfähigkeit | Lötbarkeit | Am besten geeignet für |

|---|---|---|---|---|---|

| HASL | Niedrig | Niedrig | Hoch | Gut | Standard, THT |

| OSP | Hoch | Niedrig | Mittel | Exzellent (1× Reflow) | SMT-Großserie |

| Imm. Tin (ISn) | Hoch | Mittel | Mittel | Gut | Steckverbinder, Press-Fit |

| Imm. Silver | Hoch | Mittel | Niedrig–Mittel | Exzellent | RF/High-Speed |

| ENIG | Sehr hoch | Hoch | Hoch | Exzellent | HDI, Feinraster, BGA |

| ENEPIG | Sehr hoch | Sehr hoch | Hoch | Exzellent | Luft-/Raumfahrt, Drahtbonden |

Schneller Referenzteil: Prozessparameter & Normen

Präzise Prozessführung und konsequente Normerfüllung sind Voraussetzung für konstante Qualität, elektrische Performance und Langzeitzuverlässigkeit.

1) Typische Richtwerte für Kupfer- und Finish-Dicken

| Anwendungsbereich | Prozess | Typische Dicke | Relevante Standards |

|---|---|---|---|

| Durchkontaktierungen (PTH) | Galvanisches Kupfer | 18–25 µm (0,7–1,0 mil) | IPC-6012, IPC-2221 |

| Innenlagen-Leiterbahnen | Kupferfolie/Lamination | 18–35 µm (0,7–1,4 mil) | IPC-2221, IPC-6011 |

| Außenlagen-Leiterbahnen | Galv. Kupfer + Aufbau/Plating | 35–70 µm (1,4–2,8 mil) | IPC-6012 Class 2/3 |

| Wrap-Plating um Vias | Kantenüberdeckung | ≥ 25 µm (1,0 mil) | IPC-6012B |

| ENIG—Nickelschicht | Chem./autokatalytisch | 3–6 µm (120–240 µin) | IPC-4552, JEDEC J-STD-003C |

| ENIG—Goldschicht (Immersion) | Tauchgold | 0,05–0,1 µm (2–4 µin) | IPC-4552 |

| ENEPIG—Palladiumschicht | Autokatalytisch | 0,05–0,1 µm (2–4 µin) | IPC-4556 |

2) Zentrale IPC-Standards für Plating & Finishes

| Standard | Titel | Geltungsbereich |

|---|---|---|

| IPC-6012 | Qualification and Performance for Rigid PCBs | Plating-Dicken, Via-Integrität, Wrap-Anforderungen |

| IPC-2221 | Generic PCB Design Standard | Kupfergewichte, Leiterbahnbreiten |

| IPC-6011 | Generic Performance Specification for PCBs | Grundlegende Qualitätsmetriken |

| IPC-4552 | Specification for ENIG Surface Finish | Ni/Au-Dicken und Qualitätsanforderungen |

| IPC-4556 | Specification for ENEPIG Finish | Ni/Pd/Au-Anforderungen |

| IPC-A-600 | Acceptability of Printed Boards | Visuelle Kriterien: Hohlstellen, Gleichmäßigkeit |

| IPC-TM-650 | Test Methods Manual | Mikroschliffe, Dickenmessung |

3) Wesentliche Prozess-Kontrollparameter

- Stromdichte: typ. 1,5–3,0 A/dm² (galv. Kupfer)

- Badtemperatur: 20–25 °C (68–77 °F) (saures Kupferbad)

- Bewegung/Umwälzung: mechanisch oder Luftsprudeln zur Homogenität

- pH-Wert: ca. 0,2–1,0 für optimale Kupferionen-Verfügbarkeit

- Additiv-Management: Egalisierer/Glanzbildner exakt dosieren, um Rauheit/Unregelmäßigkeiten zu vermeiden

- Plating-Zeit: abhängig von Zielschichtdicke und Leiterplattendicke

4) Toleranzen & Gleichmäßigkeit

- Kupferdicke: typ. ±20 % (Innen-/Außenlagen)

- Gleichmäßigkeit an Lochwänden: mind. gemäß IPC-6012 (≥ 20 µm in kritischen Vias)

- Finish-Konsistenz: gleichmäßige Gold-/Silberschichten sind entscheidend für Lötbarkeit und Kontaktwiderstand

Häufige Fragen (FAQ)

Worin besteht der Unterschied zwischen chemischem und galvanischem Kupfer-Plating?

Chemisches Plating kommt ohne Strom aus—ideal, um nichtleitende Lochwände zu aktivieren. Galvanisches Plating baut anschließend per Stromzufuhr die Kupferdicke auf.

Wie dick sollte das Kupfer in einer durchkontaktierten Bohrung (PTH) sein?

Nach IPC-6012 beträgt die Mindestdicke in der Regel 20–25 µm (0,8–1,0 mil) für Class 2; höherwertige Klassen verlangen mehr.

Welches Finish eignet sich am besten für Hochfrequenz-PCBs?

ENIG oder Immersion Silver wegen Planarität und geringerer Signaldämpfung. HASL ist hierfür nicht zu empfehlen.

Was ist „Black Pad“ bei ENIG und wie vermeidet man es?

Ein Korrosionsdefekt der Nickelschicht während ENIG, der die Lötbarkeit verschlechtert. Vorbeugung durch strenge Kontrolle von pH, Eintauchzeit und hochreine Chemie.

Wie verhält sich OSP im Vergleich zu ENIG?

OSP ist kostengünstig und gut für kurzfristige Serien. ENIG bietet längere Lagerfähigkeit, Oxidationsschutz und bessere Eignung für feinrasterige Bauteile—ideal für komplexe oder langlebige Produkte.

Was ist Wrap-Plating und warum ist es wichtig?

Dabei zieht die Kupferschicht vom Lochzylinder auf die Pad-Oberfläche—das erhöht die Lötstellenfestigkeit und die elektrische Kontaktqualität. IPC-6012B empfiehlt mind. 0,025 mm (1 mil) Überdeckung.

Ist „mehr Kupfer“ beim Plating immer besser?

Nicht unbedingt. Mehr Kupfer erhöht Stromtragfähigkeit und Robustheit, kann aber die Ätzpräzision verschlechtern und Kosten steigern. Wählen Sie die Dicke gemäß elektrischen und thermischen Anforderungen.

Fazit

Die durchkontaktierte Kupferbeschichtung und die Wahl des passenden Oberflächenfinishs zählen zu den wichtigsten Prozessen der Leiterplattenfertigung. Korrekt ausgeführt, sichern sie langfristige Leitfähigkeit, strukturelle Integrität und Lötbarkeit—Grundpfeiler leistungsfähiger Elektronik.

Wer den gesamten Ablauf versteht—vom Reinigen und der electroless-Aktivierung über das galvanische Plating bis zur Endoberfläche—trifft als Entwicklung oder Einkauf fundiertere Entscheidungen. Ebenso entscheidend ist die passende Finish-Wahl: ENIG für feinrasterige Komponenten, HASL für kostensensitive Anwendungen oder OSP für bleifreie Anforderungen. So steigern Sie Produktqualität und Lebensdauer—bei kontrollierten Kosten.