Sobald Systemdefinition, funktionale Partitionierung, Simulation und Placement abgeschlossen sind, tritt das High-Speed-PCB-Design in seine kritischste Phase ein.

Ab diesem Punkt geht es nicht mehr darum, nur zu zeigen, dass der Schaltplan funktioniert. Ziel ist es, sicherzustellen, dass das physische Design realen Flankensteilheiten (Edge Rates), Routing-Dichte, Fertigungsgrenzen und reproduzierbarer Serienproduktion standhält. Anders gesagt: Hier wird aus Designabsicht ein fertigungstaugliches Layout – und der PCB-Design-Flow wechselt von Theorie zu industrieller Realität.

Dieser Guide behandelt die zweite Hälfte des PCB-Design-Flows für High-Speed-PCB-Design – mit Fokus auf High-Speed-PCB-Routing, PCB-Signalintegrität, PCB-Timing-Analyse, PCB-Routing-Constraints, PCB-Routability-Analyse sowie die Übergabe vollständiger PCB-Manufacturing-Files.

PCB-Routing-Constraints: Signalintegrität beginnt vor dem High-Speed-Routing

Bei Low-Speed-Designs reicht logische Konnektivität oft aus. Im High-Speed-PCB-Design ist das nicht der Fall.

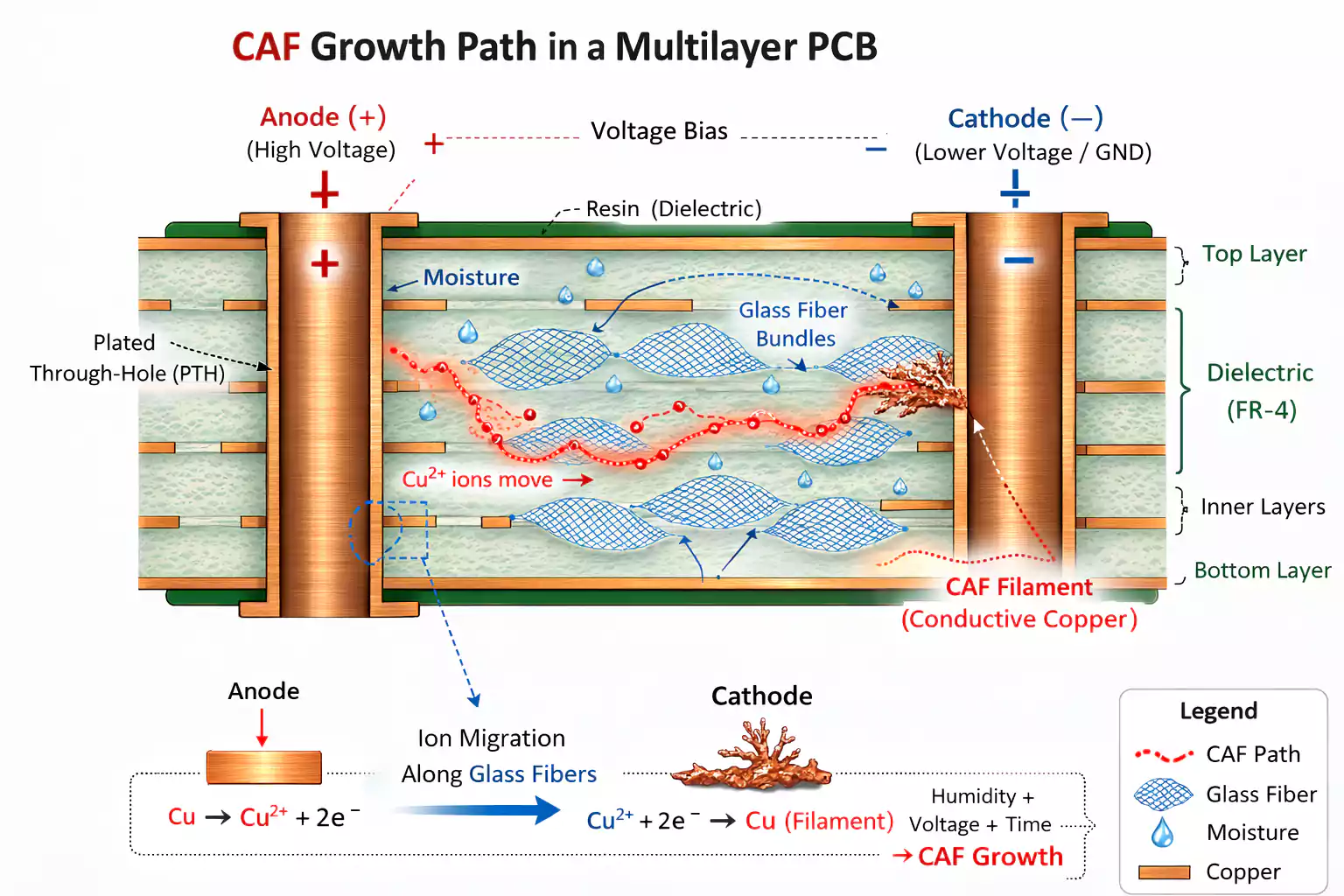

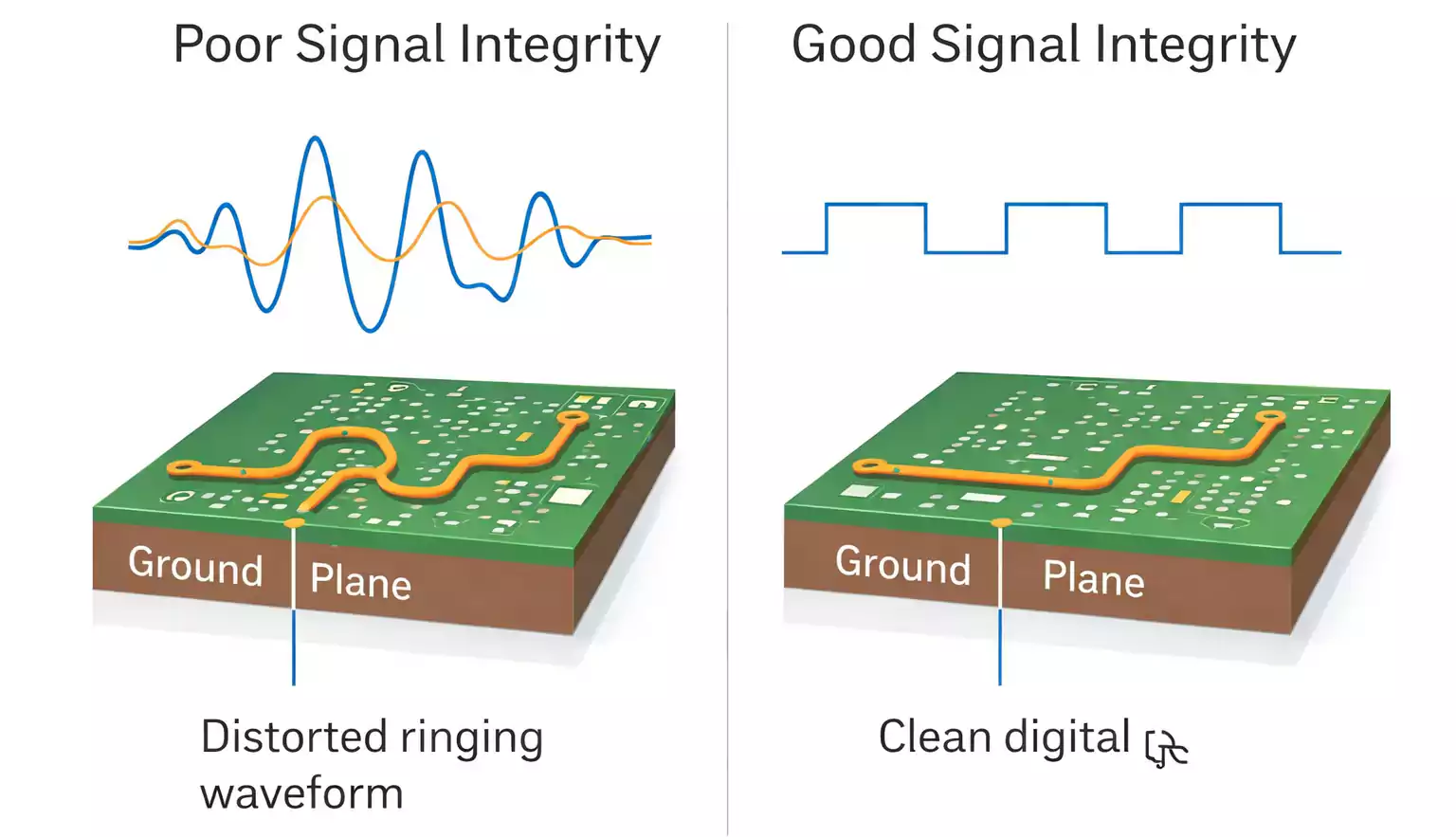

Mit steigenden Flankensteilheiten und relevanten Interconnect-Verzögerungen verhalten sich Leiterbahnen wie Übertragungsleitungen. Dann beeinflusst die Layout-Geometrie direkt die PCB-Signalintegrität. Typische Fehlerbilder sind:

- Reflexionen

- Übersprechen (Crosstalk)

- Klingeln/Ringing

- Overshoot und Undershoot

- Fehlumschaltungen / Threshold-Fehler

Daher sollten Routing-Constraints direkt nach dem Placement definiert und überprüft werden – bevor das detaillierte High-Speed-Routing startet.

Wichtige Constraints sind typischerweise:

- Driver-to-Load-Topologie

- Terminierungsstrategie und -platzierung

- Reihenfolge der Knoten entlang des Netzes

- Längenkontrolle und Skew-Grenzen

- Impedanzkonsistenz (Single-Ended und Differential)

Ziel ist ein vorhersehbares Übertragungsverhalten, bevor Kupfer final „festgelegt“ wird. In High-Speed-Backplanes und Compute-Plattformen sind diese Constraints essenziell – kleine physische Entscheidungen können große Instabilitäten verursachen.

PCB-Timing-Analyse und Übertragungsleitungsmodellierung: Vor dem Routing prognostizieren

Wenn das Placement stabil ist, sind physische Positionen und grobe Routing-Korridore bekannt. Noch bevor das detaillierte Routing beginnt, ermöglicht das eine frühe PCB-Timing-Analyse und Übertragungsleitungsmodellierung basierend auf:

- Geschätzten Leiterbahnlängen und Laufzeiten (Flight Times)

- Topologieannahmen (Point-to-Point vs. Multi-Drop)

- Frühen Risikosignalen für Reflexionen und Flankenverzerrung

Da Knotenkoordinaten und Verbindungsreihenfolge definiert sind, kann das erwartete Verhalten simuliert und Timing-Margin-Probleme erkannt werden, solange Änderungen noch einfach sind.

Der Nutzen ist klar: PCB-Signalintegritätsprobleme nach dem Routing zu beheben ist teuer; sie vor dem High-Speed-PCB-Routing zu finden ist effizienter und kontrollierbar. Für reife High-Speed-Teams ist frühes Timing- und Interconnect-Modelling ein Standardbaustein der Risikoreduktion im PCB-Design-Flow.

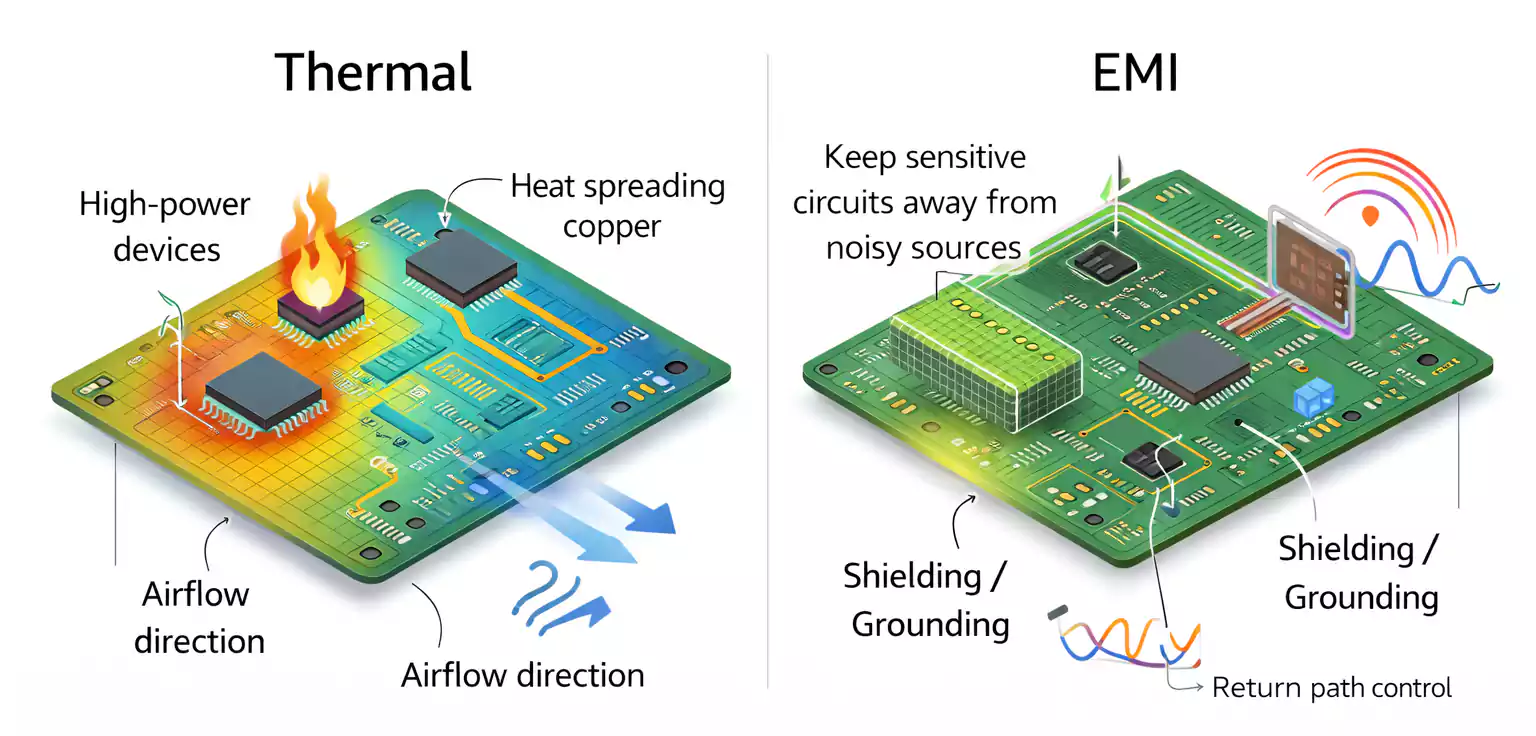

PCB-Signalintegrität: Internes Rauschen vs. externe Störungen

Nicht jedes Rauschen hat die gleiche Ursache. Alle Noise-Probleme gleich zu behandeln führt häufig zu ineffektiven Maßnahmen. Eine sauberere PCB-SI-Vorgehensweise ist die Trennung in zwei Kategorien.

1) Internes Systemrauschen (intrinsisch)

Dazu gehören:

- Thermisches Rauschen

- Schalt-/Switching-Rauschen

- Intrinsisches Signalrauschen

Internes Rauschen ist Teil des normalen Schaltungsverhaltens. Es lässt sich nicht vollständig eliminieren, aber über ein besseres Signal-Rausch-Verhältnis und kontrollierte physische Implementierung beherrschen – z. B. über Return-Paths, Decoupling und Edge-Rate-Management.

2) Externe Störungen (gekoppelt / umgebungsbedingt)

Externe Störungen entstehen außerhalb der unmittelbaren Schaltung und können besonders in empfindlichen Analog-, RF-nahen und Mixed-Signal-Bereichen problematisch sein.

Typische Gegenmaßnahmen:

- Abschirmung (Shielding)

- Verbesserte Masse-/Grounding-Strategie

- Physische Isolation sensibler Blöcke

- Filter-Netzwerke

- Kontrolliertes Interface-Design

Zu verstehen, ob ein Problem intrinsisch oder extern ist, hilft, die richtige Lösung zu wählen und Debugging zu beschleunigen.

Wenn Timing oder SI nicht passt: Placement und Topologie vor dem Routing anpassen

Wenn frühe Modellierung Folgendes zeigt:

- Zu große Verzögerung

- Zu geringe Timing-Margin

- Signifikante Reflexionen

- Flankenverzerrung oder Ringing

Dann ist die richtige Reaktion nicht „wir routen erst mal und schauen“. Im High-Speed-PCB-Design ist das der Punkt, an dem Placement und Topologie überarbeitet werden.

Typische Korrekturen:

- Kritische Komponenten näher zusammenrücken

- Priorisierte Signalpfade verkürzen

- Topologie anpassen (Point-to-Point vs. Multi-Drop)

- Terminierung hinzufügen, entfernen oder verlagern

- Stackup anpassen, um Constraints zu unterstützen

In GHz-Digitalsystemen – besonders auf physisch großen Boards – beeinflussen Layout-Länge und Topologie das globale Timing-Verhalten direkt. Iteration in dieser Phase erhöht die First-Pass-Erfolgsquote und verhindert teure Spät-Reroutes.

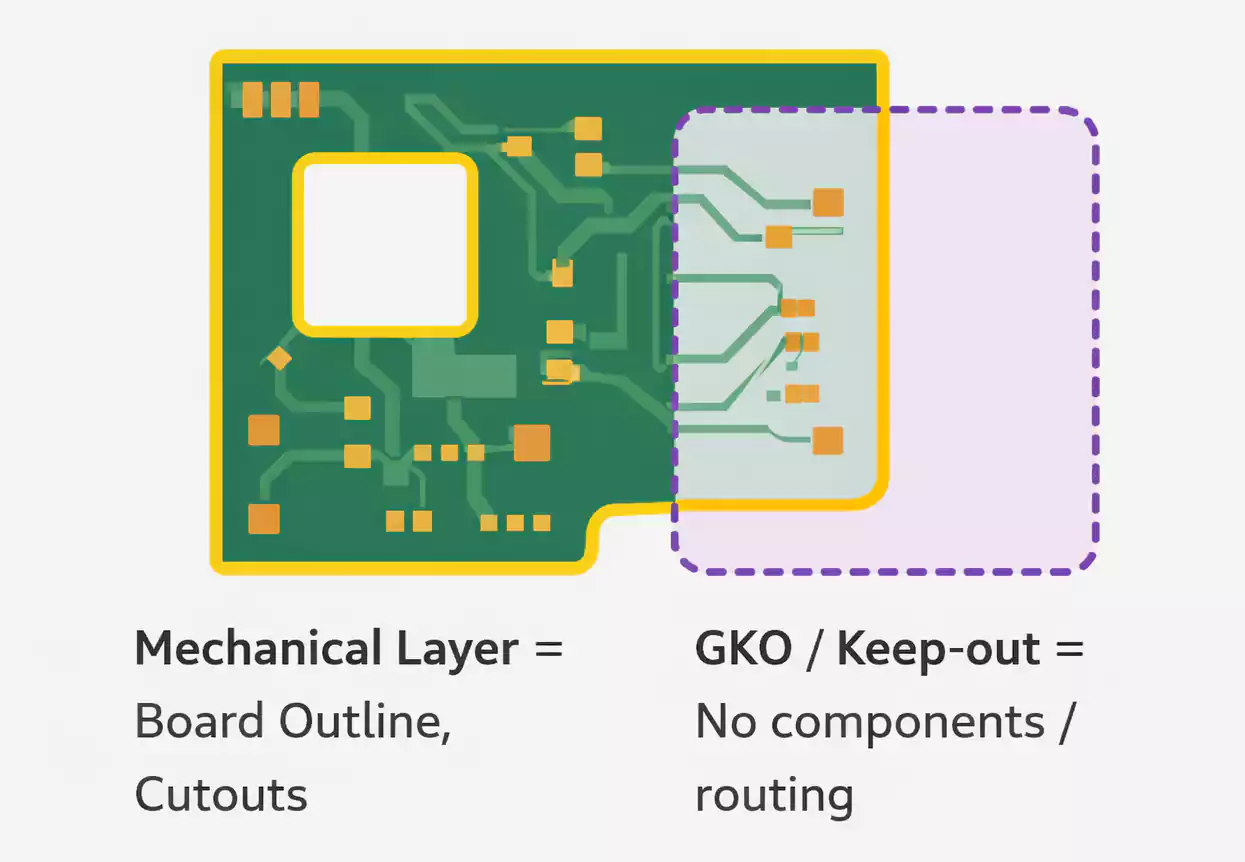

PCB-Routability-Analyse: Sicherstellen, dass das Board tatsächlich routbar ist

Viele Designs scheitern nicht an elektrischen Fehlern, sondern an unterschätzten Routing-Ressourcen. Deshalb sollte Routability-Analyse vor dem detaillierten Routing stattfinden.

Routability-Checks sollten beantworten:

- Gibt es genug Signal-Layer?

- Ist das Placement-Spacings realistisch für das erwartete Fanout?

- Wo sind die Congestion-Hotspots?

- Sind kritische Kanäle durch mechanische Constraints oder Keepouts blockiert?

- Unterstützt das Floorplan den Stackup und die Via-Strategie?

Moderne EDA-Tools liefern Congestion-Metriken und Routing-Feasibility-Checks. Wenn die Routability schwach ist, ist die richtige Maßnahme meist eine Anpassung von Placement/Layer-Strategie – nicht das Erzwingen kompromittierter Leitungsführung.

Diese Phase ist besonders wichtig bei hochdichten Multilayer-Boards und Mixed-Signal-Layouts, in denen Routing-Constraints die nutzbare Routing-Fläche reduzieren.

High-Speed-PCB-Routing: Innerhalb der Constraints arbeiten – nicht dagegen

Sobald Placement, PCB-Timing-Analyse und PCB-Routability-Analyse solide sind, beginnt das detaillierte High-Speed-PCB-Routing.

Das Routing muss die zuvor definierten Constraints einhalten, u. a.:

- Trace-Width- und Spacing-Regeln

- Length Matching und Skew-Kontrolle

- Impedanzanforderungen

- Kopplung und Symmetrie von Differential-Pairs

- Return-Path-Kontinuität

- Crosstalk-Limits und Spacing-Klassen

In der Praxis nutzen leistungsstarke Teams typischerweise:

- Manuelles Routing für kritische High-Speed-Netze

- Kontrolliertes Routing für Power-Distribution-Pfade

- Automatisches Routing für unkritische Signale

- Post-Route-Cleanup und Optimierung

Ein Routing-„Playbook“ – Layer-Policy, Via-Regeln, Net-Class-Prioritäten und Review-Kriterien – verbessert Konsistenz und reduziert Review-Schleifen in Multi-Engineer-Designs.

Post-Route-Verifikation: SI, Timing und Connectivity schließen

Routing fertig heißt nicht Design fertig. Jetzt müssen reale Längen und Geometrien revalidiert werden.

Post-Route-Checks umfassen typischerweise:

1) Re-Check von PCB-Signalintegrität und PCB-Timing-Analyse

- Timing-Margins anhand realer Trace-Längen bestätigen

- Reflexionen und Flankenqualität erneut prüfen

- Kopplungsrisiken zwischen Aggressor/Victim-Netzen bewerten

2) Netlist- / Connectivity-Verifikation

- Sicherstellen, dass keine unbeabsichtigten Connectivity-Änderungen passiert sind

- Prüfen, dass keine Opens/Shorts durch Edits eingeführt wurden

3) Fertigungstauglichkeit und Regelkonformität

- Trace-Width/Spacing-Compliance sicherstellen

- Solder-Mask-Clearances validieren

- Vermeiden, dass Pads versehentlich freigelegt oder abgedeckt werden

- Bestätigen, dass Impedanzstrukturen fertigungstauglich sind

Hier werden viele „funktioniert im CAD“-Probleme abgefangen, bevor sie zu „fällt im Build durch“ werden.

PCB-Manufacturing-Files: Vom Design-Database zur produktionsreifen Übergabe

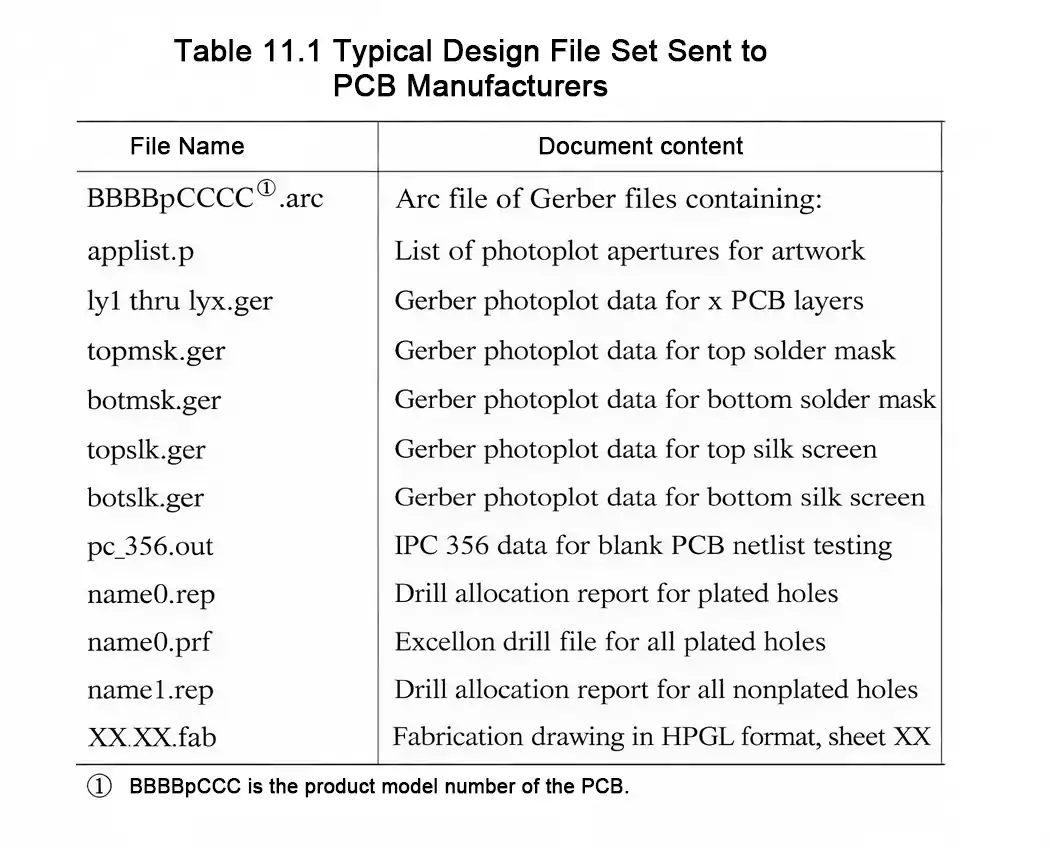

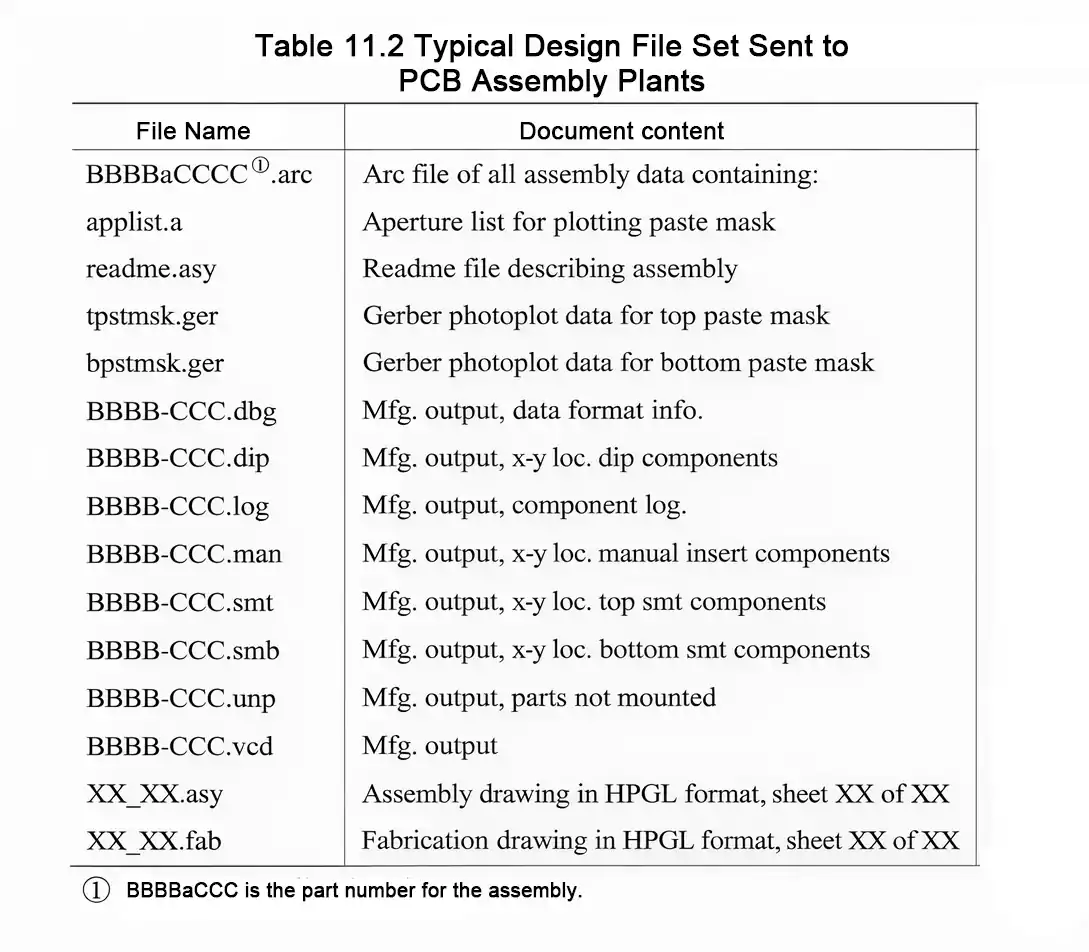

Nach Abschluss der Verifikation wechselt der PCB-Design-Flow in die Manufacturing-Release-Phase. Ein vollständiges Release-Package umfasst typischerweise:

- Fertigungsoutputs (Gerber oder ODB++)

- Drill-Files

- Pick-and-Place-Daten

- Assembly-Zeichnungen

- Bare-Board-Testdaten (falls zutreffend)

- Functional-Test-Dokumentation (falls zutreffend)

- Vollständige, validierte BOM

Diese PCB-Manufacturing-Files sind die Grundlage für Fertiger und Bestücker. Unklarheiten führen zu Verzögerungen, Scrap-Risiko und Yield-Verlusten. Für B2B-Hardware sind Klarheit und Vollständigkeit dieser Daten direkt mit Durchlaufzeit, Reproduzierbarkeit und Skalierbarkeit verknüpft.

Design-Archivierung: Das High-Speed-PCB-Design als Asset schützen

Letzter Schritt: strukturierte Archivierung.

Archivierung ist mehr als Backup. Sie unterstützt:

- Zukünftige Revisionen und ECOs

- Field-Failure-Investigation

- Version-Traceability

- Lifecycle-Management

Ein vollständiges Archiv umfasst Native-Database, Manufacturing-Outputs, Testdokumente, Revisionshistorie und Engineering-Notizen. Wenn ein Design später nicht reproduzierbar ist, wird das zum Business-Risiko – nicht nur zur Unannehmlichkeit.

Fazit: High-Speed-PCB-Design braucht einen disziplinierten PCB-Design-Flow

Die zweite Hälfte des PCB-Design-Flows entscheidet, ob ein High-Speed-PCB-Design reibungslos in die Produktion übergeht – oder in eine teure Debug-Schleife gerät.

Wenn Routing-Constraints, Timing-Analyse, Routability-Analyse und diszipliniertes High-Speed-Routing als zusammenhängender Prozess umgesetzt und mit realen physikalischen Daten verifiziert werden, entsteht ein Board, das:

- Konsistent gefertigt werden kann

- Zuverlässig bestückt wird

- Tests effizient besteht

- Skalierbar in Serie geht

- Langfristig wartbar bleibt

Das ist der Unterschied zwischen einem Board, das im Labor läuft, und einem Produkt, das zuverlässig ausgeliefert wird.