In der Elektronikfertigung kann der Begriff „flip board PCB“ zwei völlig unterschiedliche Dinge bedeuten. Manche Ingenieurinnen und Ingenieure verwenden ihn im Zusammenhang mit Flip-Chip-Packaging und dessen Integration in Leiterplattendesigns. Andere meinen damit das Umdrehen bzw. Spiegeln eines PCB-Layouts in ihrer EDA-Software. Dieser umfassende Leitfaden behandelt beide Bedeutungen und liefert umsetzbare Tipps, Best Practices und Checklisten auf Expertenniveau. Ganz gleich, ob Sie ein hochdichtes BGA mit Flip-Chip-Dies entwickeln oder in KiCad lediglich ein Board spiegeln möchten – hier finden Sie die passenden Antworten.

Was bedeutet „Flip Board PCB“ wirklich?

Wenn Nutzerinnen und Nutzer nach „flip board PCB“ suchen, verfolgen sie in der Regel eine von zwei Absichten:

Flip-Chip-Packaging auf der Leiterplatte:

Dabei werden Flip-Chip-ICs (integrierte Schaltkreise, mit der aktiven Seite nach unten montiert) direkt auf der Leiterplatte oder auf einem Interposer platziert. Dieser Ansatz ist in Hochleistungs- und Hochdichte-Designs verbreitet – etwa in Smartphones, Netzwerkausrüstung oder fortgeschrittenen Rechensystemen.

EDA-basiertes Umdrehen des Boards:

Hierbei geht es um Funktionen in Tools wie KiCad oder EasyEDA, mit denen das Layout während der Entwicklung oder zur Fertigungsvorbereitung gespiegelt/umgedreht wird.

Dieser Artikel behandelt beide Themen – mit Schwerpunkt auf dem Flip-Chip-Packaging und einem praxisnahen EDA-Spiegel-Abschnitt am Ende.

Flip-Chip auf der Leiterplatte: Konzepte, Vorteile und Einsatzzeitpunkte

Was ist Flip-Chip?

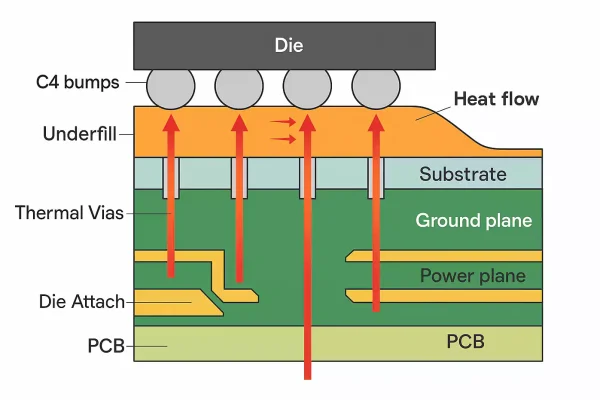

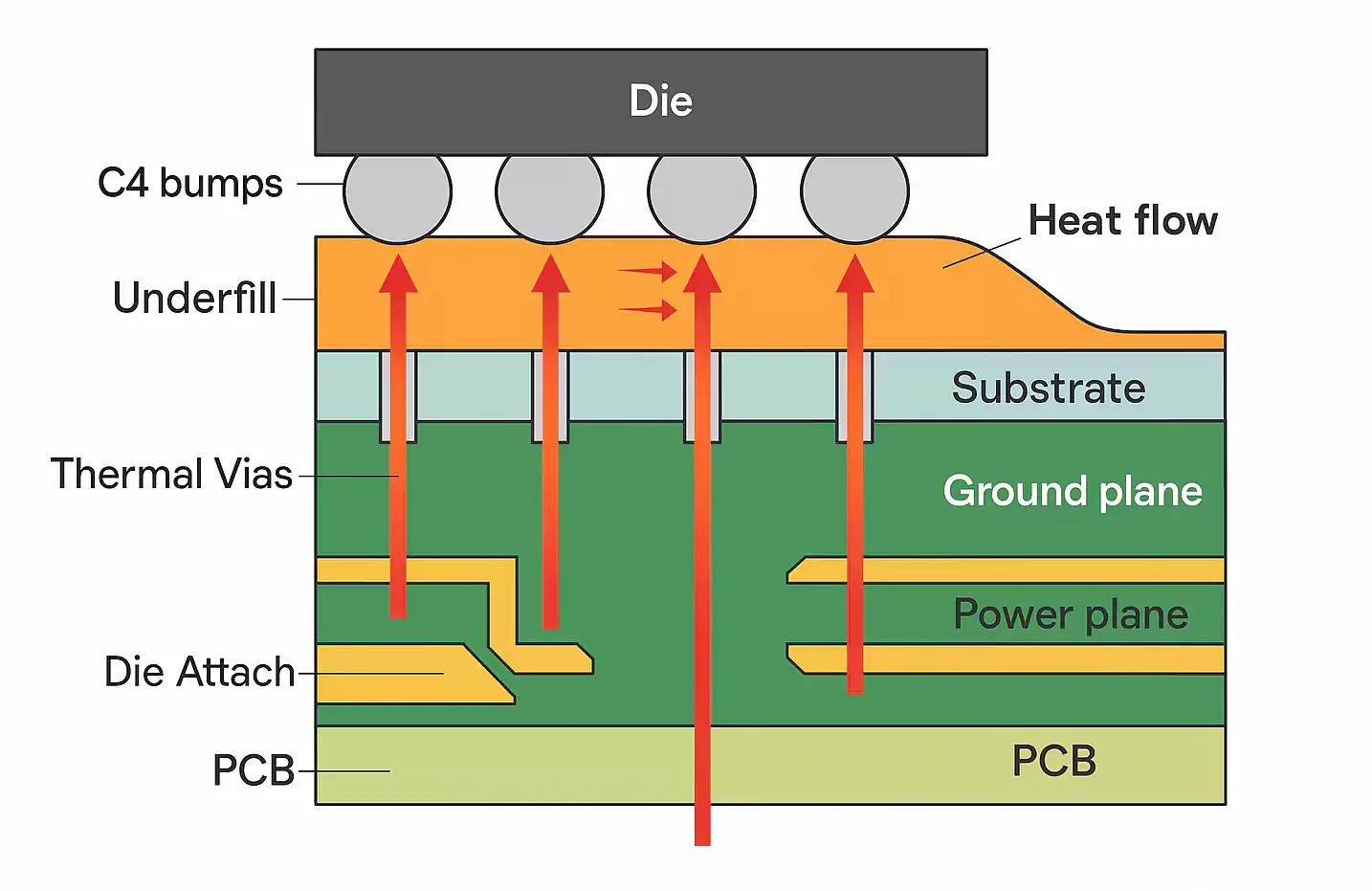

Flip-Chip ist eine Gehäusetechnologie, bei der der Silizium-Die umgedreht (face-down) montiert wird. Die elektrische Verbindung zwischen Die und Substrat erfolgt direkt über Lotkugeln (auch C4-Bumps genannt). Im Gegensatz zum Drahtbonden entstehen kurze, hochdichte Verbindungen.

Vorteile des Flip-Chip-Packagings

- Elektrische Performance: Geringere Induktivität und parasitäre Effekte dank kurzer Verbindungswege.

- Thermisches Management: Bessere Wärmeabfuhr über Substrat und Die-Oberfläche.

- Flächeneffizienz: Kompaktere Layouts mit mehr I/O pro Flächeneinheit.

Typische Anwendungsfälle

- Hochgeschwindigkeits-Prozessoren (CPU, GPU)

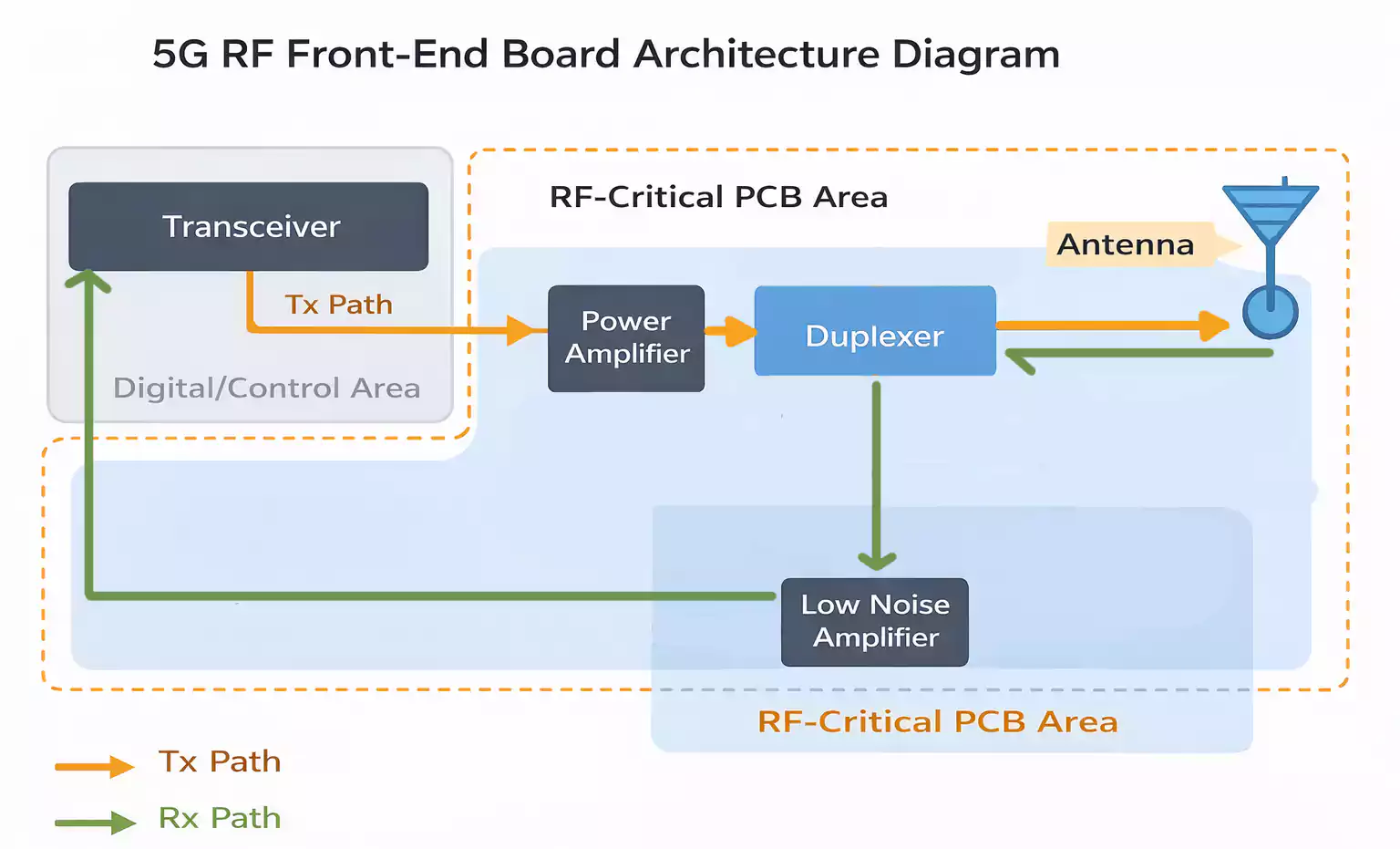

- RF-Komponenten

- Fortgeschrittene BGA- und SiP-Designs (System-in-Package)

- Geräte mit feiner Pitch-Anforderung und starkem Miniaturisierungsdruck

Prozessablauf: Flip-Chip-Montage auf der Leiterplatte

Der typische Integrationsprozess umfasst:

- Bump-Aufbringung: Der Silizium-Die wird mit Lotkugeln versehen.

- Die-Platzierung: Der Die wird umgedreht und präzise auf dem Substrat ausgerichtet.

- Reflow-Löten: Wärme erzeugt dauerhafte Lötverbindungen.

- Underfill-Applikation: Epoxidharz füllt den Spalt zwischen Die und Substrat, erhöht die mechanische Stabilität und die Zuverlässigkeit.

- Reinigung und Inspektion: Entfernen von Rückständen; Prüfung mittels Röntgen oder AOI.

Wichtig: Underfill kompensiert thermische Ausdehnungsunterschiede (CTE-Mismatch) und reduziert die mechanische Belastung der Lotkugeln während thermischer Zyklen.

PCB-Layout-Best-Practices für Flip-Chip/FC-BGA

Das Design einer Leiterplatte mit Flip-Chip- oder FC-BGA-Bauteilen erfordert Präzision und Detailtreue. Die wichtigsten Empfehlungen:

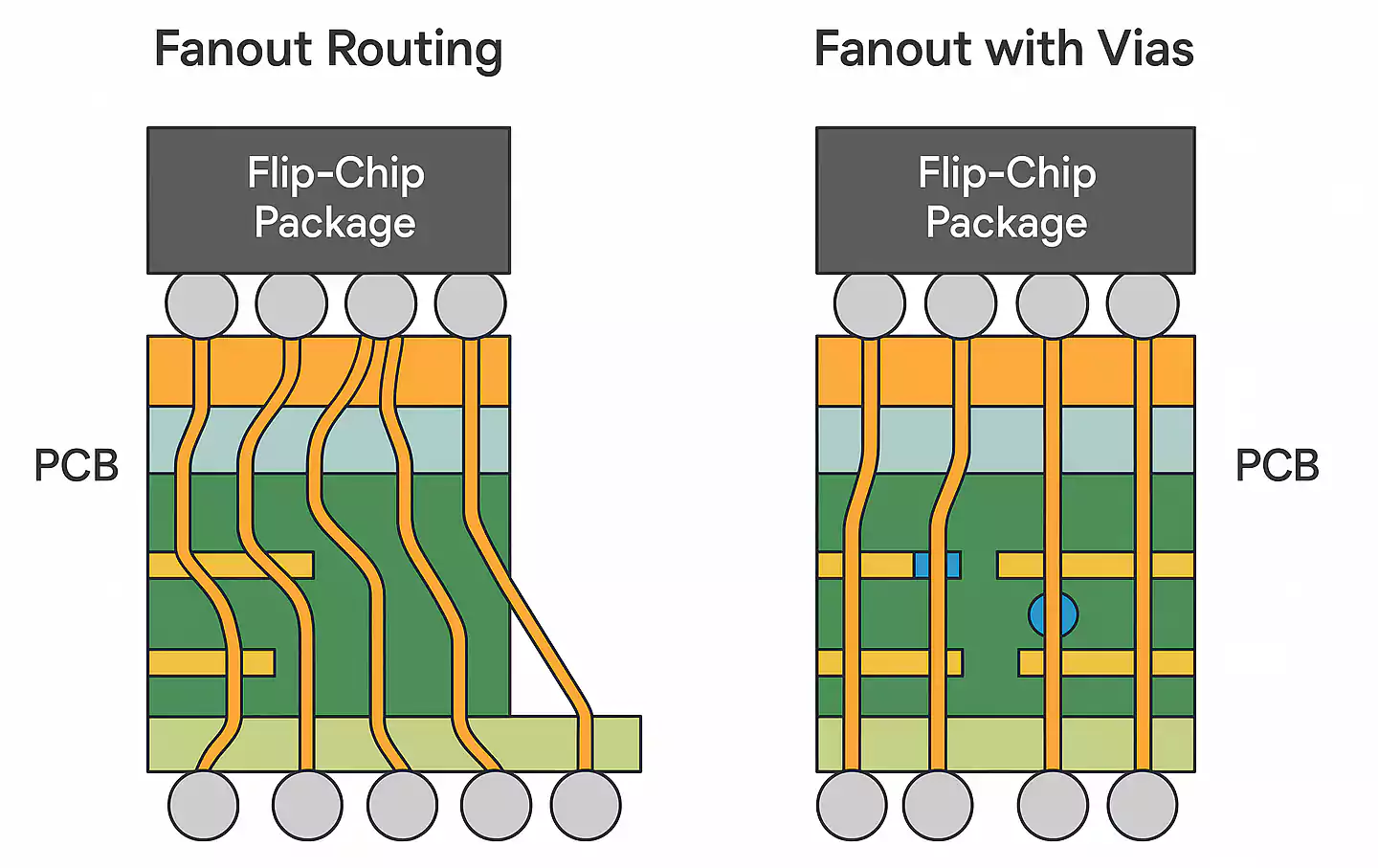

1) Fanout-Strategie

- Via-in-Pad oder Mikro-Vias einsetzen, um Routing-Engpässe zu reduzieren.

- HDI-Stackups (High-Density Interconnect) für Fine-Pitch-Breakout nutzen.

- Lange Leiterbahnen vom Die-Zentrum zu äußeren Ball-Pads vermeiden.

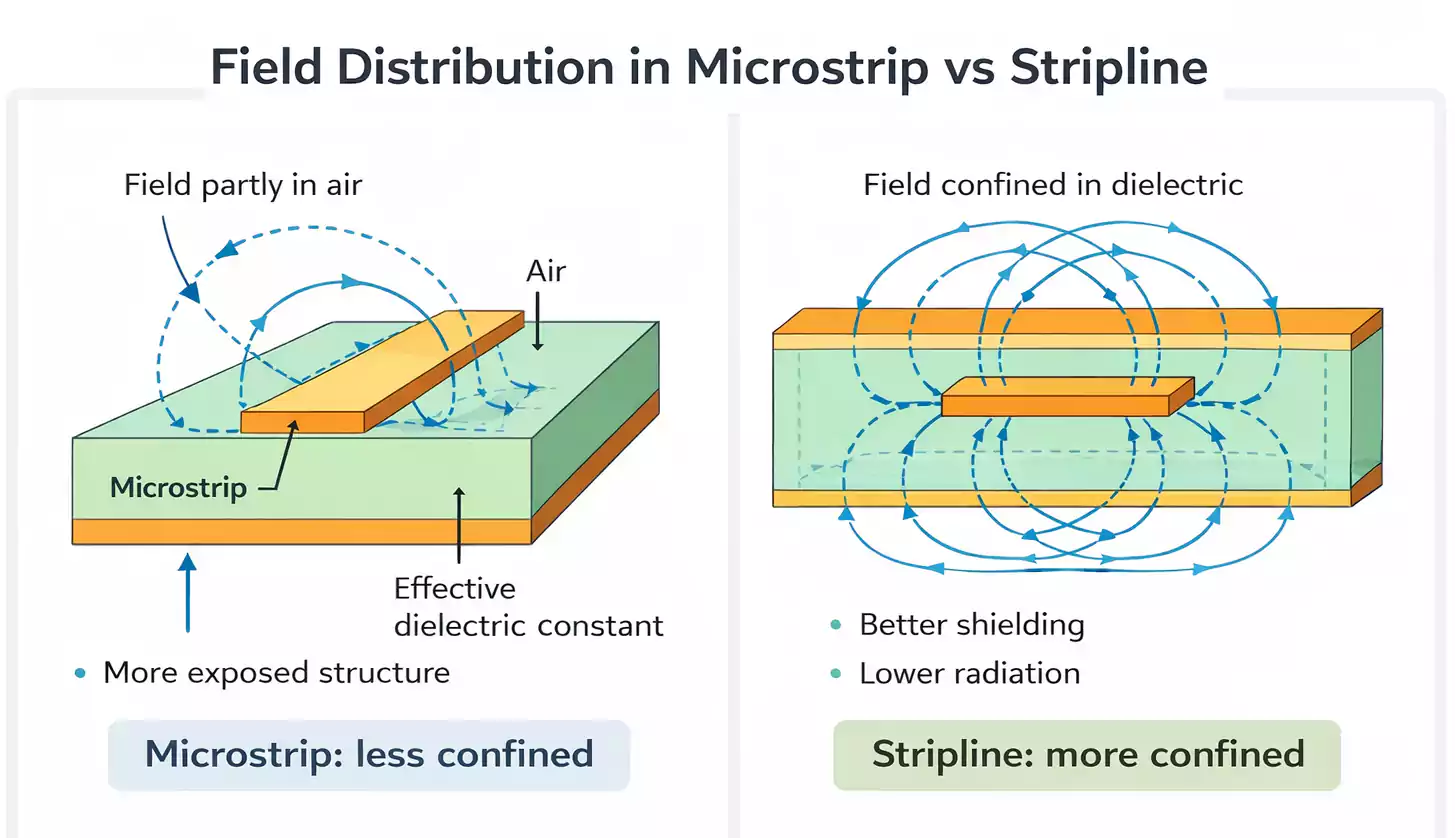

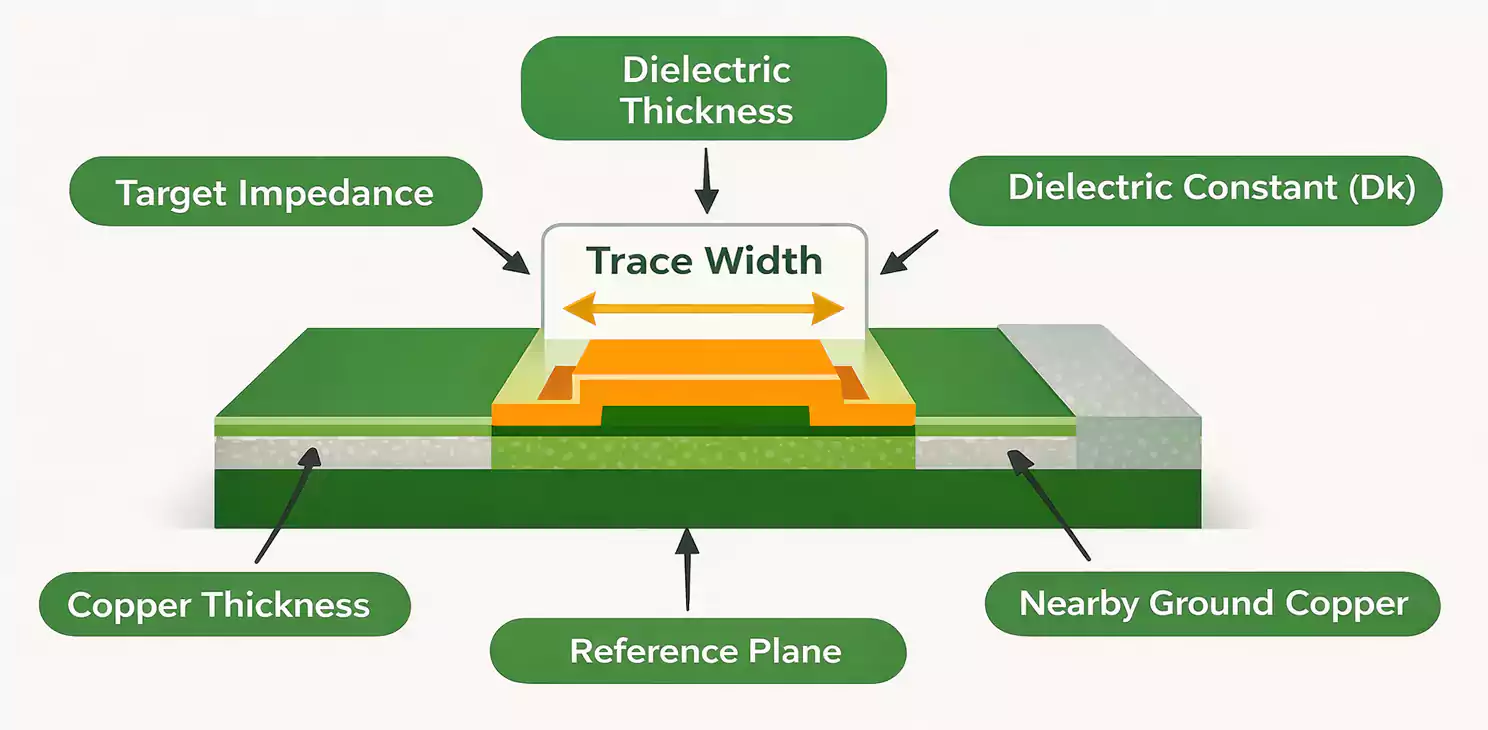

2) Impedanz und Signalintegrität

- Referenzebenen konsistent halten.

- Differenzialpaare mit Längenanpassung für High-Speed-Signale verwenden.

- Rückstrompfade berücksichtigen und Stubs minimieren.

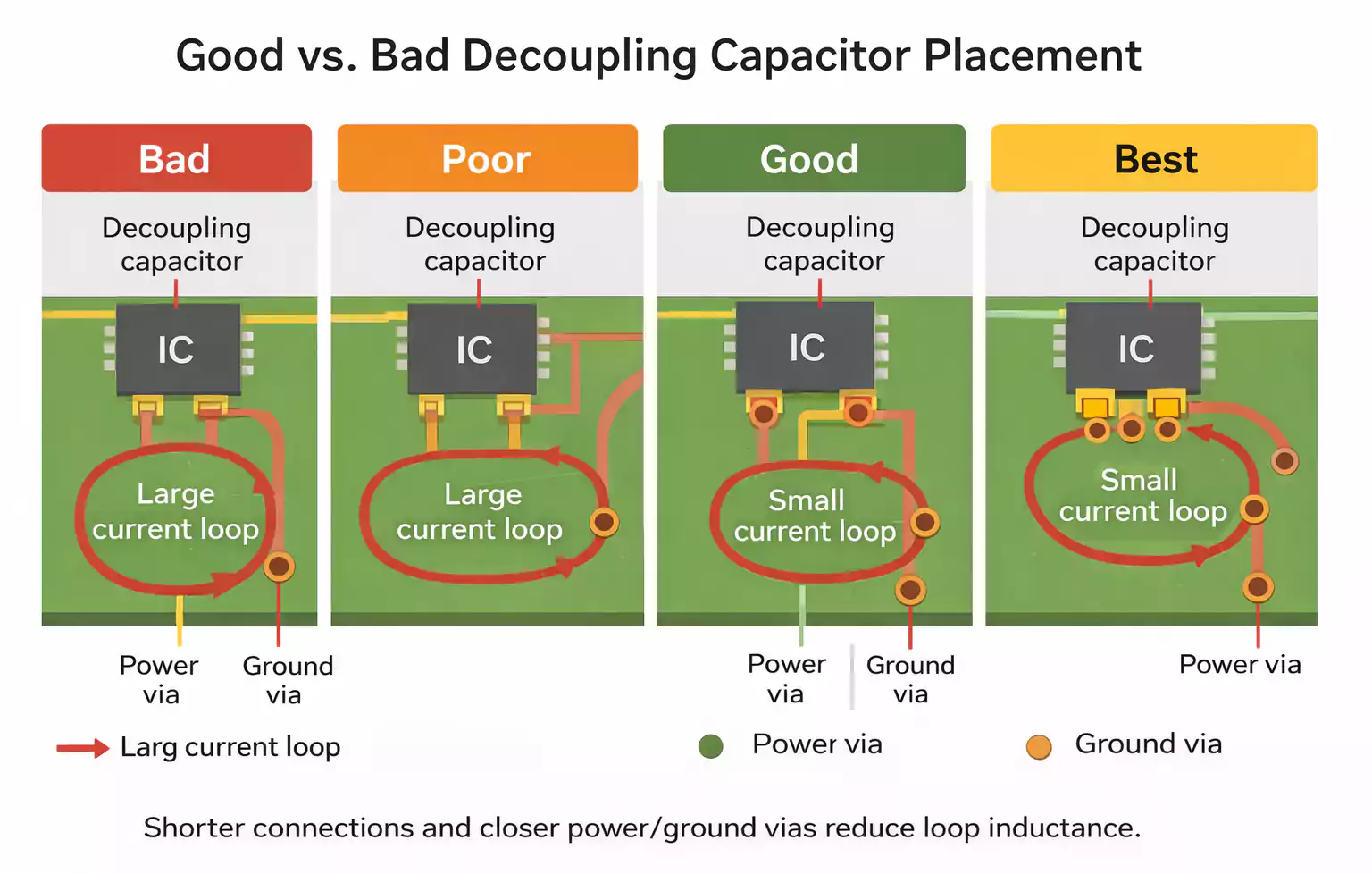

3) Power- und Ground-Planung

- Niedrige Impedanz der Stromverteilung über durchgehende Ebenen sicherstellen.

- Entkopplungskondensatoren nahe den Power-Balls platzieren.

- Mehrere Vias einsetzen, um ESL/ESR in kritischen Netzen zu reduzieren.

4) Thermisches Design

- Kupferdicke oder Kupferfläche zur Wärmeableitung erhöhen.

- Thermal-Vias nutzen, um Wärme in Innen-/Unterlagen zu leiten.

- Thermiksimulation durchführen, wenn die Leistungsdichte > 1–2 W/cm² liegt.

5) Materialien und Stackup

- Substrate mit geringem CTE-Mismatch wählen (z. B. BT, ABF).

- Ebenenzahl vs. Routbarkeit sinnvoll ausbalancieren.

- Dk/Df-Konstanz für kontrollierte Impedanzen sicherstellen.

6) Footprint und Land-Pattern

- Land-Pattern anhand des Hersteller-Datasheets verifizieren.

- Bibliotheken nach IPC-7351 verwenden.

- Exakte Ausrichtung in Abhängigkeit vom Reflow-Profil sicherstellen.

Flip-Chip vs. Drahtbonden vs. BGA: Entscheidungsmatrix

| Merkmal | Flip-Chip | Drahtbonden | BGA |

|---|---|---|---|

| Elektrische Performance | Exzellent | Moderat | Gut |

| Wärmeabfuhr | Hoch | Niedrig | Mittel |

| Gehäusegröße | Sehr kompakt | Größer | Kompakt |

| Montagekomplexität | Hoch | Niedrig | Mittel |

| Kosten | Höher | Niedriger | Mittel |

| Anwendung | High-End, RF, Miniaturisierung | Günstige ICs | Allgemeiner Einsatz |

Wann Flip-Chip einsetzen?

- Hochleistungsrechnen

- Anwendungen mit feinem Pitch oder hoher I/O-Dichte

- Thermisch kritische Designs

DFM/DFX-Checkliste für den Fertigungserfolg

Damit die Fertigung und Bestückung gelingt:

1) Design for Manufacturability (DFM)

- Mindest-Leiterbahnbreiten/-abstände je Fertiger bestätigen.

- Pad-Größen auf Schablone (Stencil) und Bump-Abmessungen abstimmen.

- Nicht-standardisierte Pad-Formen nur bei Bedarf einsetzen.

2) Design for Assembly (DFA)

- Fiducials sowie globale/lokale Ausrichtmarken vorsehen.

- Underfill-Typ und Prozessparameter dokumentieren.

- Bestückungszeichnung und Reflow-Profil bereitstellen.

3) Design for Testability (DFT)

- Testpunkte für JTAG/Funktionstest einplanen.

- Boundary-Scan-Zugriff nach Möglichkeit ermöglichen.

4) Lieferunterlagen

- Gerber oder ODB++

- BOM mit eindeutigen Artikelnummern und Alternativen

- Pick-and-Place-Datei mit exakten Koordinaten

- Stackup-Zeichnung mit Impedanzangaben

Troubleshooting & Zuverlässigkeit

Häufige Probleme:

- Offene/kurzgeschlossene Bumps

- Voids im Underfill

- Verzug/Warping von Die oder Leiterplatte

- Unzureichende Reinigung unter dem Die

Prüfwerkzeuge:

- 2D/3D-Röntgen

- SAM (Scanning Acoustic Microscopy)

- AOI (Automated Optical Inspection)

Zuverlässigkeitstests wie Temperaturzyklen, Vibrationen und Feuchtebelastung sind in anspruchsvollen Einsatzumgebungen unverzichtbar.

So „flippen“/spiegeln Sie ein PCB in EDA-Tools (sekundäre Absicht)

Auch wenn „flip board PCB“ meist Flip-Chip meint, möchten manche lediglich das Layout im CAD spiegeln. So geht’s:

KiCad:

- F drücken, um ein Bauteil bzw. die Seite zu wechseln.

- View > Flip Board View zur Spiegelansicht nutzen.

- Sicherstellen, dass Texte/Symbole korrekt gespiegelt werden.

EasyEDA:

- Rechtsklick → Flip Horizontally/Vertically.

- Pad-Orientierung und Netz-Kontinuität nach dem Spiegeln prüfen.

- Mit Gerber-Vorschau die Spiegelung final verifizieren.

Wichtig: Für einseitige Bestückung oder Schablonenfertigung müssen Layer und Silkscreen gespiegelt werden – die Netzliste bleibt dabei unverändert und korrekt.

FAQs

F1: Ist Flip-Chip dasselbe wie BGA?

Nein. Flip-Chip beschreibt eine Die-Anbindungsmethode, BGA ist eine Gehäusebauform. Ein Flip-Chip kann innerhalb eines BGA eingesetzt sein.

F2: Benötigen alle Flip-Chip-PCBs Underfill?

In den meisten Anwendungen mit hoher thermischer/mechanischer Belastung wird Underfill empfohlen; in weniger kritischen Umgebungen ist er optional.

F3: Ist Flip-Chip immer teurer?

Nicht zwingend. Bei hochdichten, leistungsstarken Designs kann Flip-Chip die Lagenzahl oder die Leiterplattenfläche reduzieren und so Packaging-Kosten teilweise kompensieren.

F4: Kann ich Standard-PCB-Materialien mit Flip-Chip verwenden?

Nur wenn CTE und thermische Eigenschaften kompatibel sind. Häufig sind spezialisierte Substrate wie ABF erforderlich.

Zusammenfassung & Fazit

Flip-Chip bietet der modernen Elektronik herausragende Performance, bringt jedoch höhere Design- und Fertigungskomplexität mit sich. Mit sorgfältiger Planung, enger Zusammenarbeit mit dem Fertiger und strikter Einhaltung von DFM/DFX lassen sich thermische, elektrische und platzsparende Vorteile realisieren.

Wer „flip board PCB“ im Sinne von EDA-Spiegeltricks verwendet, sollte die korrekte Spiegelpraxis kennen – das sichert präzise Fertigungsdaten und zuverlässige Ergebnisse.

Wenn Sie möchten, passe ich den Text gerne stilistisch an (Sie/du, Tonalität Technik/Marketing) oder liefere eine druckfertige PDF/Word-Version.