Einleitung

Mit dem Fortschritt von Gehäusetechnologien wie BGA (Ball Grid Array) und CSP (Chip Scale Package) steigt die Nachfrage nach höherer Verbindungsdichte in Leiterplatten (PCBs) stetig an.

Die zunehmende Leiterbahndichte beeinflusst jedes Element des Basismaterials und dessen Herstellungsprozess.

Um eine zuverlässige High-Density-Interconnect-Struktur (HDI) zu erreichen, muss der Bauteilabstand (Pitch) verringert werden. Dadurch werden engere Leiterbahnabstände und kleinere Durchkontaktierungen (PTHs) erforderlich.

Drei Hauptmethoden zur Erhöhung der Leiterbahndichte

Im Allgemeinen gibt es drei Möglichkeiten, die Leiterbahndichte einer Leiterplatte zu erhöhen:

- Verkleinerung von Leiterbahnbreite und -abstand

- Erhöhung der Anzahl der Lagen

- Verkleinerung von Durchkontaktierungen und Pads

Jede dieser Methoden bringt eigene Kompromisse zwischen Fertigungstoleranz, Kosten und elektrischer Leistung mit sich.

Schauen wir uns diese Ansätze genauer an.

1. Verkleinerung von Leiterbahnbreite und -abstand

Der direkteste Weg, mehr Leiterbahnen auf derselben Fläche unterzubringen, ist die Reduzierung von Breite und Abstand der Leiterbahnen.

Feinlinien-Ätzverfahren ermöglichen kleinere Strukturen und engere Führung, verkleinern aber zugleich das Prozessfenster der Fertigung.

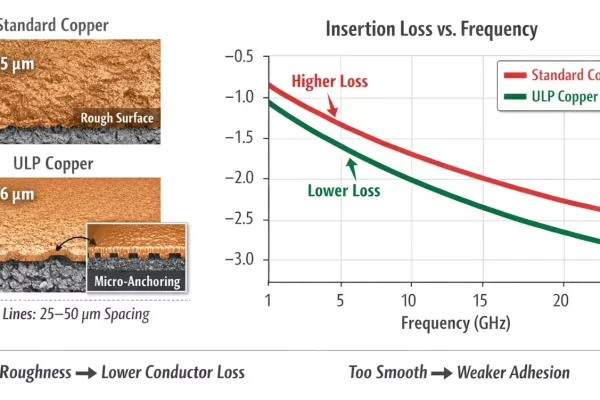

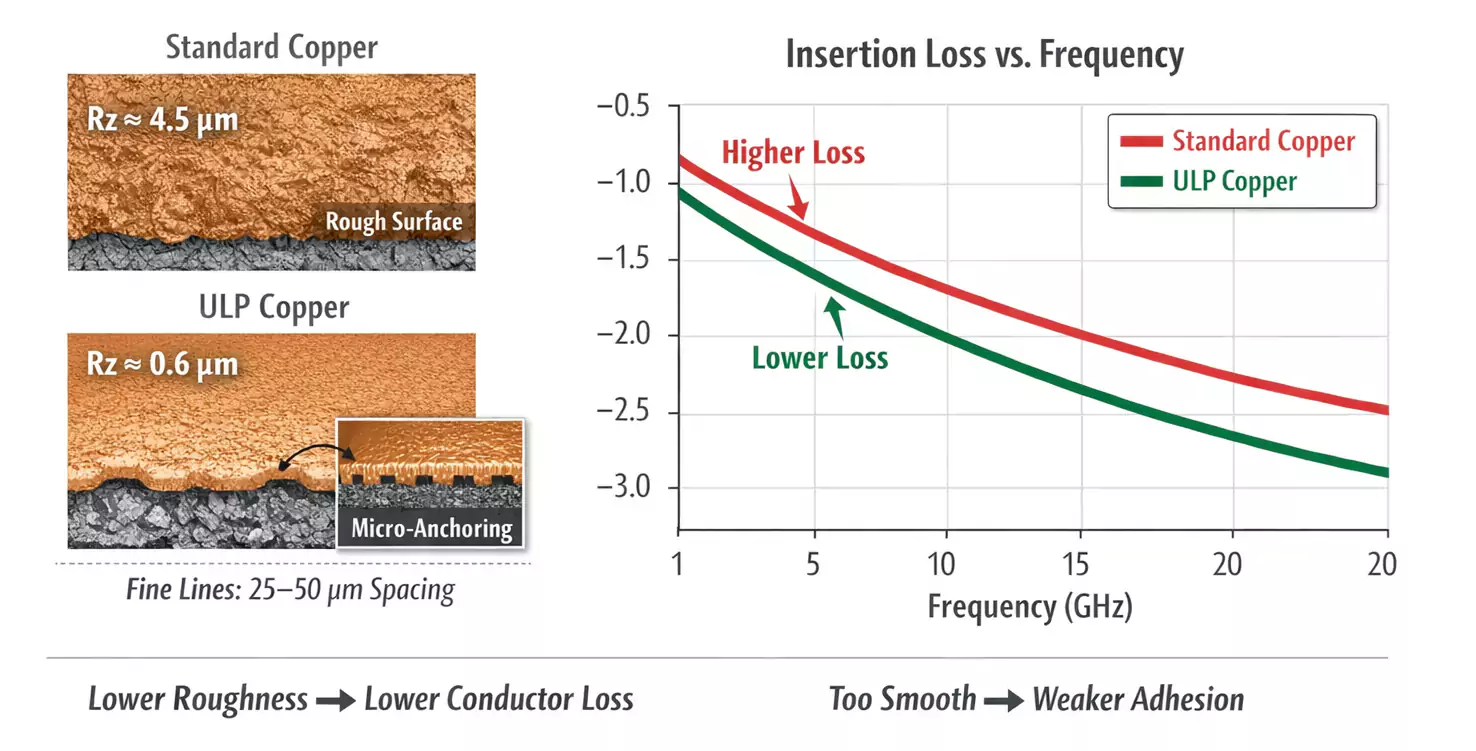

Um eine hohe Ausbeute beim Ätzen zu erreichen, müssen Hersteller Kupferfolien mit kontrollierter, niedriger Oberflächenrauheit verwenden.

Eine glattere Kupferoberfläche ermöglicht eine präzisere Linienbildung – unerlässlich für 25 µm oder noch feinere Line-Space-Designs, wie sie in modernen HDI-Platinen üblich sind.

Allerdings hat dies eine Kehrseite: Glatteres Kupfer bietet eine geringere Haftfestigkeit zur dielektrischen Schicht.

Die mikroskopischen Spitzen der herkömmlichen Kupferfolie dienen als Ankerpunkte für das Harz während der Laminierung.

Wird die Rauheit reduziert, sinkt die Haftkraft – was zu Delamination oder geringer Schälfestigkeit führen kann.

Typischer technischer Zielkonflikt:

| Ziel | Empfohlene Oberfläche | Risiko |

|---|---|---|

| Feine Ätzstruktur | Niedrige Rauheit (glatt) | Geringere Haftung |

| Hohe Haftfestigkeit | Höhere Rauheit | Schwieriger zu ätzen |

Darüber hinaus beeinflusst die Oberflächenrauheit direkt das Hochfrequenzverhalten.

Bei GHz-Frequenzen nimmt der Leiterverlust mit zunehmender Rauheit zu, da der Strom aufgrund des Skineffekts überwiegend an der Oberfläche fließt.

Eine raue Oberfläche verlängert den effektiven Strompfad und erhöht den Einfügeverlust (Insertion Loss).

Zur Lösung dieses Problems entwickeln Kupferfolienhersteller ultraglatte Folien (ULP) und umgekehrt behandelte Folien (Reverse-Treated Copper).

Diese Materialien kombinieren geringe Rauheit zur Minimierung der Verluste mit Nano-Ankerstrukturen zur Verbesserung der Haftung – ein optimales Gleichgewicht zwischen Signalintegrität, Ätzpräzision und Laminierzuverlässigkeit.

2. Erhöhung der Lagenzahl

Wenn die horizontale Fläche ausgeschöpft ist, ist der nächste logische Schritt, weitere Lagen hinzuzufügen.

Mehrlagige Leiterplatten ermöglichen eine vertikale Signalführung durch das Stapeln von Kupfer- und Dielektrikschichten.

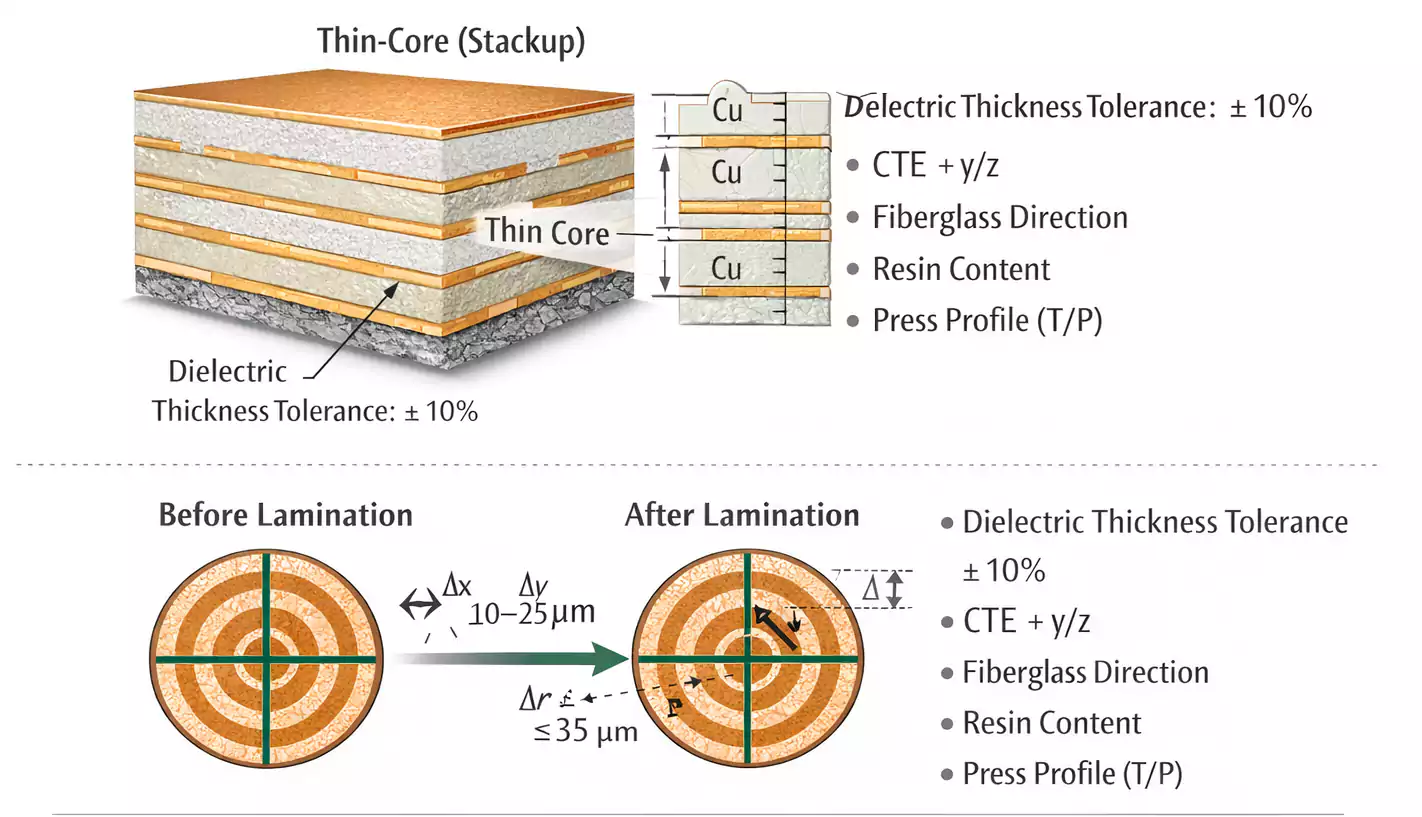

Das Hinzufügen von Lagen führt jedoch dazu, dass die gesamte Platine dicker, die einzelnen Isolierschichten aber dünner werden – was neue Herausforderungen schafft:

- Dickenkontrolle: Dünnere Dielektrika erfordern engere Fertigungstoleranzen, um gleichmäßige Impedanz und Isolation zu gewährleisten.

- Thermische Stabilität: Ein dickerer Aufbau speichert mehr Wärme während Laminierung und Reflow. Die Materialien müssen wiederholte thermische Zyklen ohne Verzug überstehen.

- Registrierungsgenauigkeit: Mehr Lagen erhöhen das Risiko von Fehlausrichtungen. Schon ein Versatz von 25 µm kann Kurzschlüsse oder Unterbrechungen verursachen.

Die Lagenregistrierung hängt stark von der maßlichen Stabilität der Laminate ab.

Kernmaterial und Prepreg dehnen sich unter Hitze und Druck aus bzw. schrumpfen.

Bei Verwendung von dünnen Kernen in Platinen mit vielen Lagen wird die Maßstabilität schwieriger zu beherrschen, was präzise Ausrichtung erschwert.

Um die Registrierungsgenauigkeit zu sichern, müssen Hersteller folgende Parameter kontrollieren:

- Druck- und Temperaturprofile der Laminierung

- Orientierung des Glasgewebes und Harzanteil

- Wärmeausdehnungskoeffizient (CTE) des Materials

Bei FastTurn PCBs setzen unsere Ingenieure auf präzise Laminiersteuerung und Röntgen-Ausrichtungssysteme, um konstante Genauigkeit in HDI-Mehrlagenaufbauten sicherzustellen.

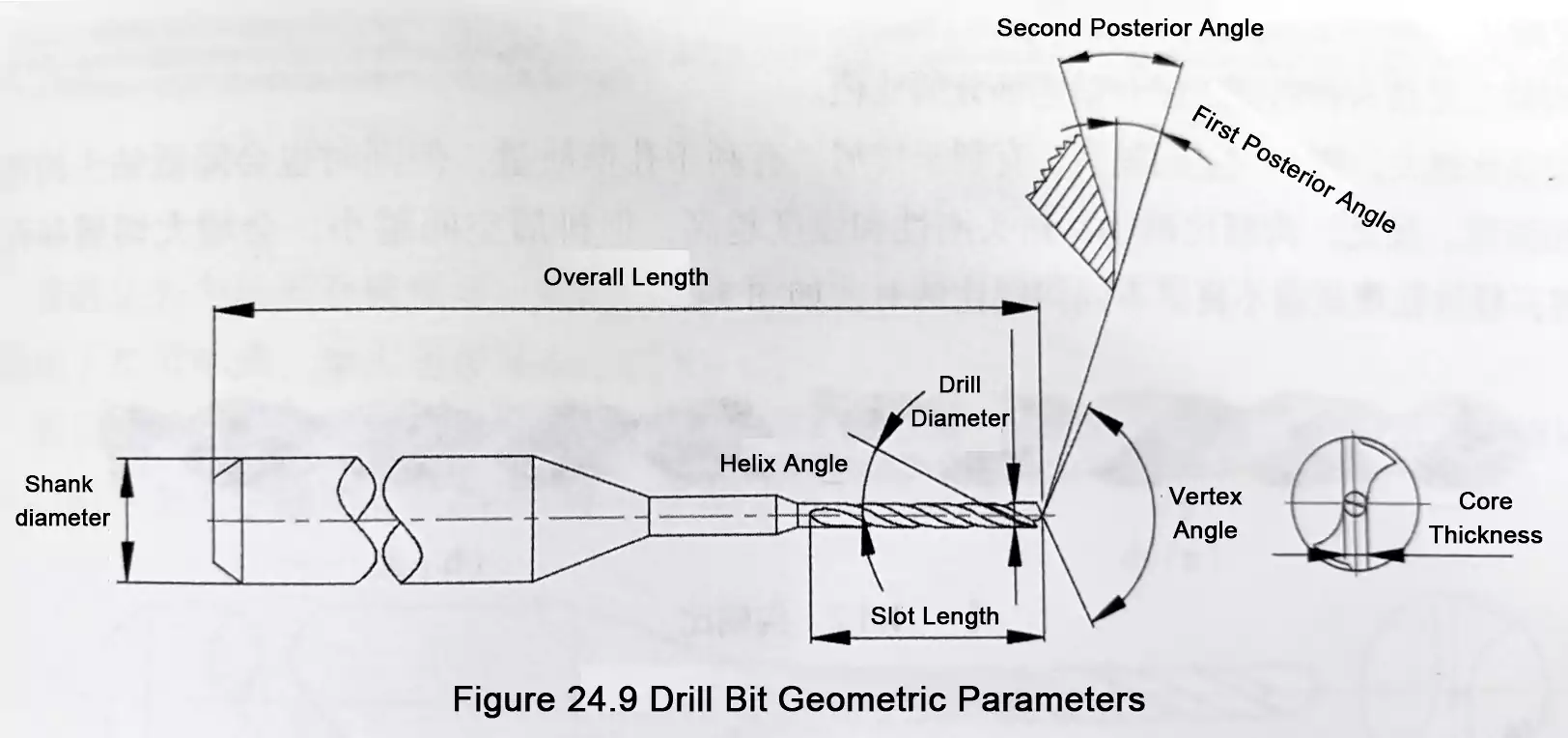

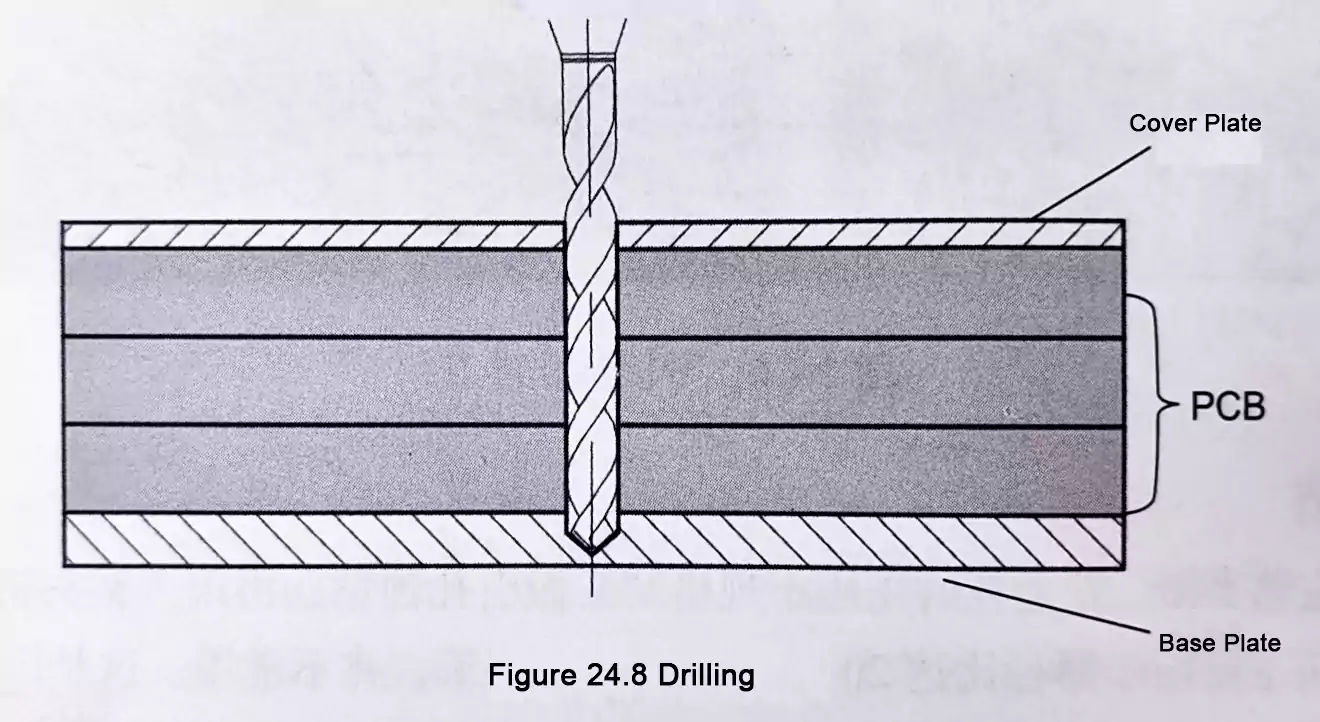

3. Verkleinerung von Vias und Pads

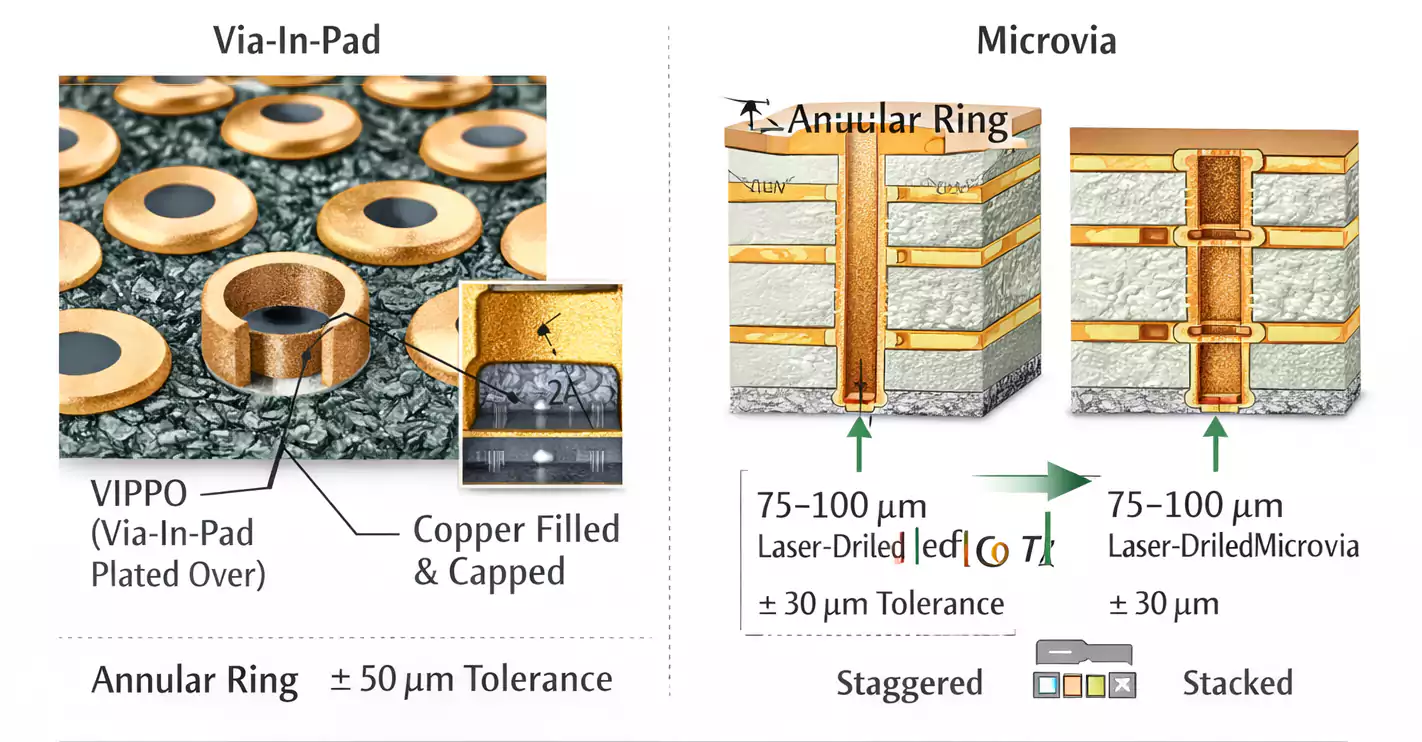

Eine weitere effektive Methode zur Erhöhung der Leiterbahndichte ist die Verkleinerung der Vias und Pads.

Kleinere Durchkontaktierungen schaffen zusätzliche Routing-Kanäle zwischen den Lagen – ein Grundprinzip der HDI-Technologie.

Wichtige Technologien:

- Lasergebohrte Microvias – typischerweise 75–100 µm im Durchmesser, verbinden ein oder zwei benachbarte Lagen.

- Via-in-Pad (VIPPO) – Vias direkt in den Bauteilpads, um Platz zu sparen und Signalwege zu verkürzen.

- Sequentielle Laminierung – Aufbau gestapelter oder versetzter Microvias Schicht für Schicht.

Die Verkleinerung von Vias und Pads erhöht jedoch die Fertigungsanforderungen.

Kleinere Pads verringern die Toleranz des Anularrings, was eine präzisere Registrierung und stabile Basismaterialien erfordert.

Unzureichende Maßstabilität kann schnell zu Via-Ausbrüchen oder Fehlausrichtung führen und die Ausbeute mindern.

Materialhersteller wie Isola und Panasonic betonen daher die maßliche Stabilität als entscheidende Materialeigenschaft für moderne HDI-Anwendungen.

Materialien mit niedrigem CTE und minimalem Harzschrumpf tragen zu einer hohen Registrierungsgenauigkeit bei.

Das richtige Gleichgewicht finden

Um bessere Ergebnisse beim Feinlinien-Ätzen zu erzielen, setzen Hersteller auf Kupferfolien mit geringer Rauheit.

Doch glatteres Kupfer bedeutet gleichzeitig schwächere Haftung zur dielektrischen Schicht.

Die Herausforderung besteht darin, das optimale Oberflächenprofil zu finden – mit geringer Rauheit für Hochfrequenz- und Feinlinienleistung, aber ausreichender Haftfestigkeit.

Kupferfolienhersteller entwickeln daher neue Folientypen, die bessere Haftung bieten, ohne die Rauheit zu erhöhen.

Fazit

Der Trend zu höherer Leiterbahndichte verändert die Leiterplattenindustrie grundlegend.

Mit steigenden Betriebsfrequenzen und immer kompakteren Bauformen wächst der Bedarf an Feinlinien-Fähigkeit, Maßkontrolle und verlustarmen Materialien weiter.

Bei FastTurn PCBs unterstützen wir unsere Kunden mit:

- Fortschrittlichen HDI-Stack-up-Designs

- Kupferoptionen mit kontrollierter Oberflächenrauheit

- Präziser Laminier- und Registrierungssteuerung

- Fachwissen in Microvia- und Via-in-Pad-Technologien

Egal ob Sie kompakte Konsumelektronik oder Hochgeschwindigkeits-Serverplatinen entwickeln – das Verständnis der Balance zwischen Kupferrauheit, Lagenzahl und Via-Design ist entscheidend, um sowohl Leistung als auch Zuverlässigkeit zu gewährleisten.