Viele Leiterplatten (PCBs) „funktionieren elektrisch“, scheitern aber trotzdem in der Serienfertigung, weil das Layout PCB DFM (Design for Manufacturability) und DFT (Design for Test) nicht ausreichend berücksichtigt. Das Ergebnis ist meist vorhersehbar: Alarme auf der SMT-Linie, instabile Handhabung, schlechte Lötstellen, mehr Nacharbeit (Rework) und eine schwache Testabdeckung.

Im Folgenden finden Sie einen praxisorientierten Leitfaden mit Fokus auf die Fertigung: die häufigsten PCB-Designfehler, die dadurch ausgelösten SMT-Defekte und die DFM-Regeln, mit denen Sie diese vermeiden—inklusive PCB-Panelisierung, Fiducial-Marken, Tooling-Holes, Tombstoning, Via-in-Pad, ICT-Testpunkte und Lötstopplack (Solder Mask).

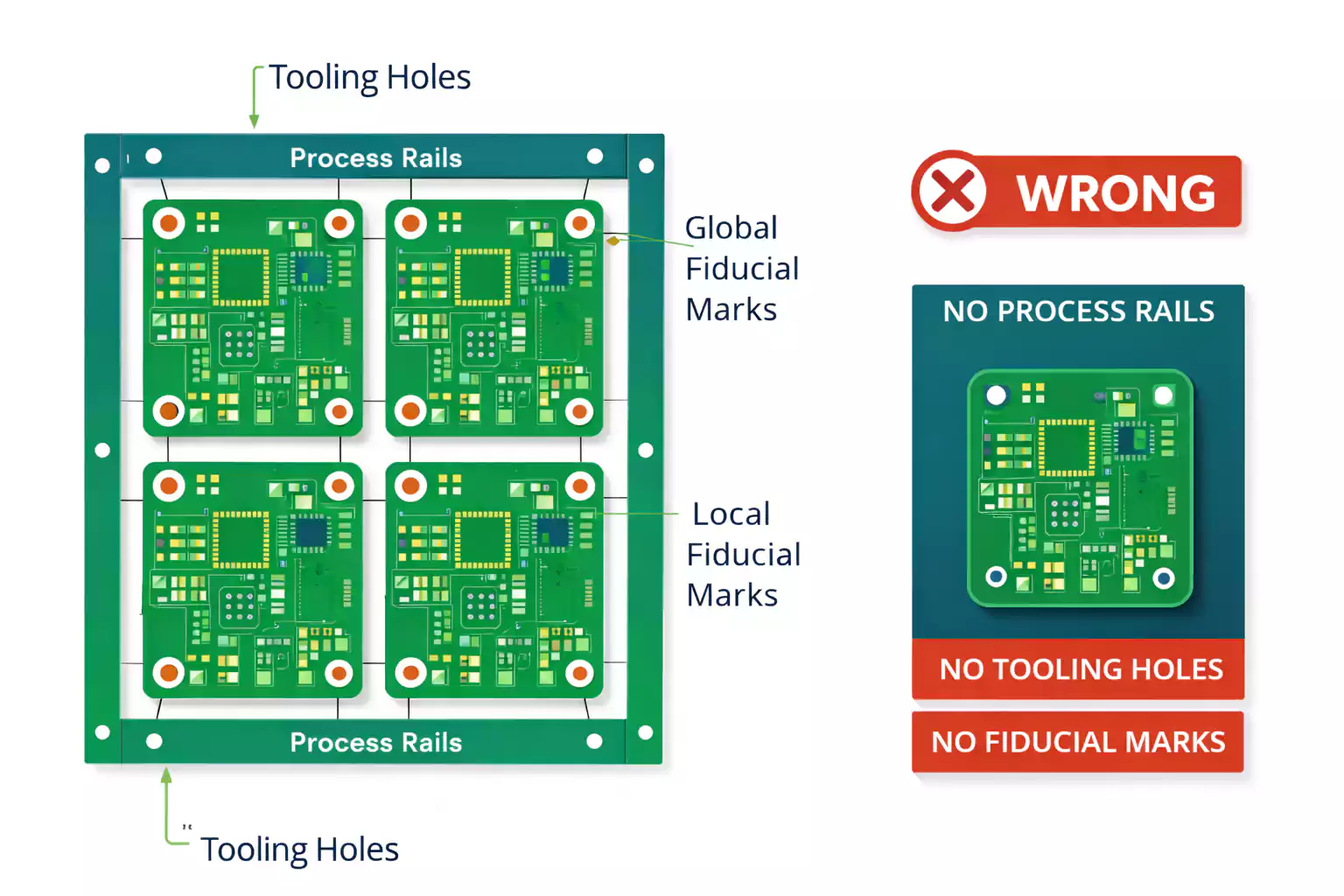

1) Fehlende Tooling-Holes und Prozess-Rails: Eine Leiterplatte, die „nicht lauffähig“ ist

PCB-Designfehler: Keine Tooling-Holes und keine Prozess-Rails (Panel-Rails / Break-Away-Kanten).

DFM-Auswirkung: SMT-Anlagen können die Leiterplatte nicht reproduzierbar spannen oder ausrichten.

Was man in der Linie sieht:

- Versatz bei der Lotpasten-Schablonierung (Solder Paste Printing)

- Vision-/Platzierfehler am Bestückautomaten (Pick-and-Place)

- Instabiler Transport, Board-Skew, häufige Alarme

DFM-Lösung:

- Panel-Rails und standardisierte Tooling-Holes für Registrierung und Handling vorsehen

- Mindest-Railbreite und Lochspezifikation des EMS/Bestückers einhalten

2) Extremes Board-Format oder ungewöhnliche Kontur: Instabiles Handling und Platzierung

PCB-Designfehler: Leiterplatte zu klein/zu groß oder stark unregelmäßig.

DFM-Auswirkung: Passt nicht ins mechanische Fenster der SMT-Linie oder benötigt teure Vorrichtungen (Fixtures).

Typische Folgen:

- Schlechter Transport (Kippen, Vibration)

- Platzierdrift und Druckfehler

- Höheres Warpage-Risiko (Verzug) im Reflow

DFM-Lösung:

- PCB-Panelisierung mit Rails nutzen, um ein stabiles Handling-Format zu erreichen

- Konturen vermeiden, die Standard-Fördersysteme nicht sicher unterstützen

3) Fiducial-Marken falsch umgesetzt: Vision-Fehler und Platzieralarme

PCB-Designfehler: Fehlende oder nicht standardkonforme Fiducial-Marks (Mark-Punkte), besonders nahe Fine-Pitch-ICs (z. B. FQFP).

Häufige Fiducial-Probleme:

- Lötstopplack zu nah oder bedeckt die Kupferfläche

- Falsche Größe (zu groß/zu klein)

- Zu geringer Kontrast im Umfeld

Was passiert:

- Kameras des Bestückautomaten „locken“ nicht zuverlässig auf den Fiducial

- Häufige Alarme und schlechtere Platziergenauigkeit

DFM-Lösung:

- Standardisierte Global- und Local-Fiducials verwenden

- Fiducials sauber halten (keine Masken-/Legend-Überlagerung) und genügend Freistellung für guten Kontrast einplanen

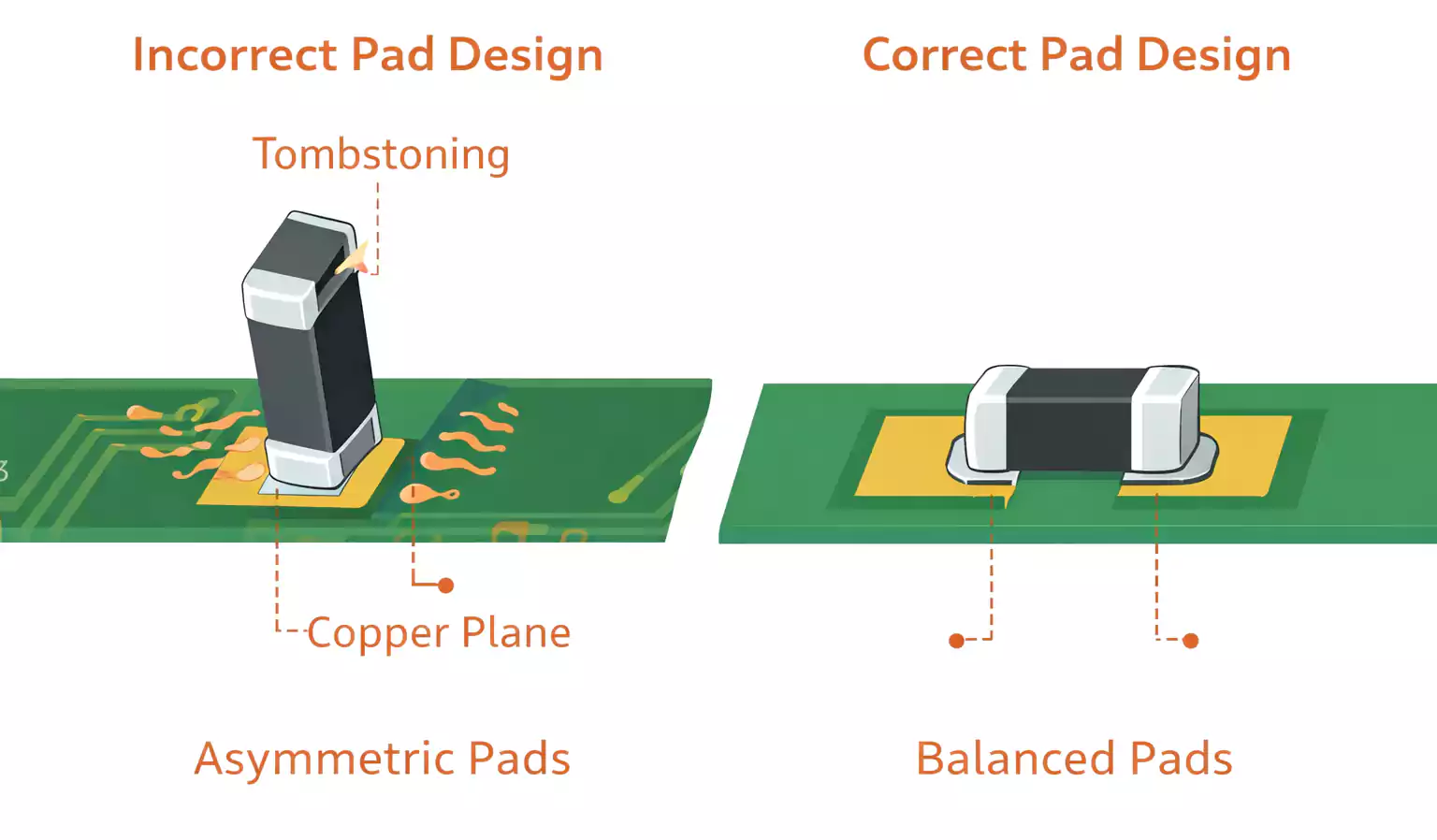

4) Falsche SMT-Padgeometrie: Versatz, Rotation und Tombstoning

PCB-Designfehler: Falsche Pad-Größe/Abstände für Chip-Bauteile oder asymmetrische Pads.

SMT-Defekte: Fehlpositionierung, Schiefstand, Tombstoning.

Warum das passiert (Reflow-Dynamik):

Im Reflow schmilzt die Lotpaste, Oberflächenspannungskräfte wirken auf das Bauteil. Sind Pads ungleich, sind auch die Kräfte ungleich—das Bauteil wandert oder richtet sich auf.

DFM-Lösung:

- Bewährte IPC-Footprints oder Hersteller-Landpattern einsetzen

- Padgeometrie symmetrisch halten (Größe, Form, Pastenvolumen)

5) Via-in-Pad ohne korrekte Prozessierung: Lotmangel (Solder Starvation)

PCB-Designfehler: Via-in-Pad mit offenen Vias (nicht gefüllt/verschlossen).

SMT-Defekte: Zu wenig Lot, schwache Lötstellen, intermittierende Unterbrechungen.

Was passiert:

Geschmolzenes Lot „zieht“ in das Via (Wicking) und fehlt anschließend an der Padoberfläche.

DFM-Lösung:

- Via-in-Pad nur einsetzen, wenn es wirklich nötig ist

- Wenn erforderlich: geeignete Via-Behandlung spezifizieren (gefüllt/plugged und planarisiert) passend zu den Fähigkeiten von Leiterplattenfertiger/EMS

6) Massekupfer als Pad genutzt: Thermisches Ungleichgewicht → Tombstoning

PCB-Designfehler: Ein Pad ist an eine große Massefläche angebunden oder ein Leiterbahn-Segment wird als Pad genutzt, während das andere Pad kleiner ist.

SMT-Defekte: Tombstoning (besonders bei kleinen Passiven).

Warum passiert das:

Mehr Kupfer = höhere thermische Masse = langsameres Aufheizen. Eine Seite schmilzt später, die Oberflächenspannung zieht das Bauteil hoch.

DFM-Lösung:

- Kupfer um Pads herum ausbalancieren

- Wo sinnvoll: Thermal-Reliefs einsetzen

- Beide Anschlüsse thermisch möglichst ähnlich gestalten

7) Fine-Pitch-IC-Pads zu breit oder zu kurz: Bridging und schwache Lötstellen

PCB-Designfehler (FQFP-Beispiel):

- Pads zu breit → mehr Lot → Bridging

- Heel/Toe zu kurz → geringere mechanische Festigkeit der Lötstelle

SMT-Defekte:

- Lötbrücken (Kurzschlüsse)

- Fragile Lötstellen, schlechtere Zuverlässigkeit

DFM-Lösung:

- Validierte Landpattern für Fine-Pitch-Packages nutzen

- Pad-Breite/-Länge und Lötstopplack-Strategie auf das Prozessfenster abstimmen

8) Routing zentral zwischen Pads: AOI/Visuelle Prüfung wird schwieriger

PCB-Designfehler: Leiterbahnen verlaufen mittig zwischen Fine-Pitch-Pads.

Auswirkung: Schlechtere Sichtbarkeit der Lötstellen nach Reflow.

Was passiert:

AOI und manuelle Inspektion erkennen Lotfillet-Kanten schlechter—Bridges und Lotmangel werden leichter übersehen.

DFM-Lösung:

- So routen, dass Lötstellen möglichst gut sichtbar bleiben

- Inspektionsreserve nicht für minimale Routing-Bequemlichkeit opfern

9) Wave-Solder-Design ohne Hilfsfeatures: Höheres Bridging-Risiko

PCB-Designfehler: Für Wellenlöten vorgesehene ICs ohne Hilfspads/Solder-Thieving-Features.

SMT-Defekt (Wave): Bridging nach Wellenlöten.

DFM-Lösung:

- Layout auf Wellenrichtung und Lotfluss auslegen

- Geeignete Hilfsfeatures ergänzen (gemäß Fähigkeiten des Bestückers)

10) Ungünstige Bauteilverteilung: Reflow-Verzug und Deformation nach dem Löten

PCB-Designfehler: ICs in einem Bereich konzentriert; Kupfer- und Massenverteilung unausgewogen.

Auswirkung: PCB-Warpage nach Reflow und Instabilität bei Second-Side-Assembly.

Defekte und Konsequenzen:

- Platzierabweichungen

- Stress auf Fine-Pitch-/BGA-Lötstellen

- Probleme in Vorrichtungen und Test-Setups

DFM-Lösung:

- Kupferverteilung ausbalancieren

- Schwere Bauteile nicht ohne mechanische Betrachtung clustern

- Stack-up und Panel-Support frühzeitig mitdenken

11) ICT-Testpunkte nicht DFM-/DFT-tauglich: Geringe Abdeckung oder kein Test

PCB-Designfehler: ICT-Testpunkte fehlen, sind zu klein, schlecht erreichbar oder zu dicht beieinander.

Auswirkung: ICT-Nadeln können nicht zuverlässig kontaktieren—oder ICT ist gar nicht möglich.

DFM/DFT-Lösung:

- Zugängliche, ausreichend getrennte Testpunkte für kritische Netze vorsehen

- Testpunkte nicht unter Bauteilen oder in Keep-Out-Bereichen platzieren

12) Zu geringe Abstände zwischen SMDs: Rework wird riskant

PCB-Designfehler: SMD-zu-SMD-Abstände sind zu klein.

Auswirkung: Nacharbeit ist langsam, riskant und teils unmöglich.

DFM-Lösung:

- Praktische Rework-Abstände für Heißluftdüse und Lötkolben einplanen

- Reparierbarkeit als Teil der Herstellbarkeit behandeln

13) Lötstopplack und Silkscreen auf Pads: Non-Wet-Opens und Intermittents

PCB-Designfehler: Schlechte Lötstopplack-Öffnungen oder Silkscreen auf Pads.

SMT-Defekte: Schlechte Benetzung, kalte Lötstellen, Opens, intermittierende Fehler.

DFM-Lösung:

- Lötstopplack-Clearance-Regeln konsequent anwenden

- Silkscreen von lötbaren Flächen fernhalten

- Masken-Expansion und Registriertoleranzen prüfen

14) Schlechte Panelisierung oder V-Score-Auslegung: Warpage nach Reflow

PCB-Designfehler: PCB-Panelisierung oder V-Score ist schlecht ausgelegt oder schlecht gefertigt.

Auswirkung: Verzug nach Reflow, mechanischer Stress beim Depaneling.

Typische Probleme:

- Schwache Tabs oder ungleichmäßige Unterstützung

- V-Score-Tiefe/Position passt nicht zu Boarddicke und Layout

DFM-Lösung:

- Panel-Rails + stabile Tab/V-Score-Strategie nutzen

- Trennstellen fern von empfindlichen Bauteilen und Fine-Pitch-Joints platzieren

Ursachen: Warum treten diese PCB-Designfehler immer wieder auf?

Die meisten Ausfälle lassen sich auf drei Punkte zurückführen:

- Reflow wird als dynamischer Prozess unterschätzt

Tombstoning und Schiefstand sind nicht „Zufall“, sondern Physik + Footprint + thermische Balance. - Prozessingenieure werden zu spät eingebunden

DFM- und Assembly-Constraints werden oft erst im Pilot-Build sichtbar. - Keine konsistenten internen PCB-DFM/DFT-Richtlinien

Ohne Standards für Footprints, Fiducials, Tooling-Holes, Panelisierung, ICT-Testpunkte und Lötstopplack werden die gleichen Fehler in jedem Projekt wiederholt.

Praktisches Fazit: Mit DFM-Denken vermeiden Sie die meisten SMT-Defekte

Wenn Sie weniger SMT-Defekte und eine stabilere Produktion wollen, behandeln Sie das PCB-Layout als Teil des Fertigungssystems:

- PCB DFM: Tooling-Holes, Panel-Rails, Fiducials, Panelisierungsstrategie, Kupferbalance

- SMT-Zuverlässigkeit: Pad-Symmetrie, Via-in-Pad-Kontrolle, thermische Balance gegen Tombstoning

- DFT: ICT-Testpunkte mit gutem Zugang und ausreichendem Abstand

- Prozesshygiene: saubere Lötstopplack-Öffnungen und Silkscreen-Keep-Outs