Was ist eine HDI-Leiterplatte?

HDI steht für High-Density Interconnect (hochdichte Verbindungstechnik).

Eine HDI-Leiterplatte nutzt feine Leiterbahnen, Mikrovias und mehrere Build-up-Schichten, um eine höhere Verdrahtungsdichte als herkömmliche Multilayer-Boards zu erreichen.

Nach IPC-2226 gilt typischerweise:

- Leiterbahn-/Abstandsbreite < 100 µm (≈ 4 mil)

- Mikrovias < 150 µm (≈ 6 mil)

- > 20 Pads pro cm² Leiterplattenfläche

Kurz gesagt: HDI ermöglicht mehr Bauteile auf kleinerer Fläche, kürzere Verbindungswege und bessere elektrische Performance – ideal für Smartphones, Wearables, Kfz-Radar und Medizintechnik.

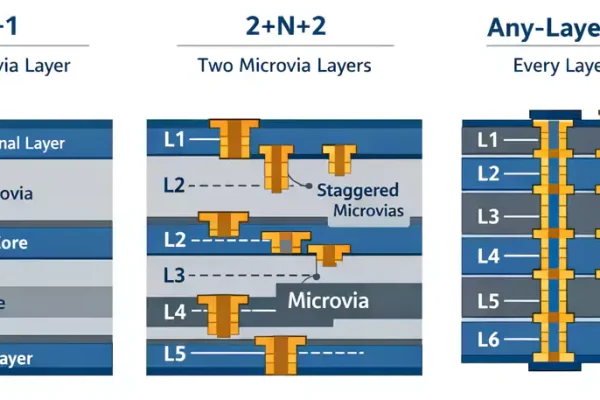

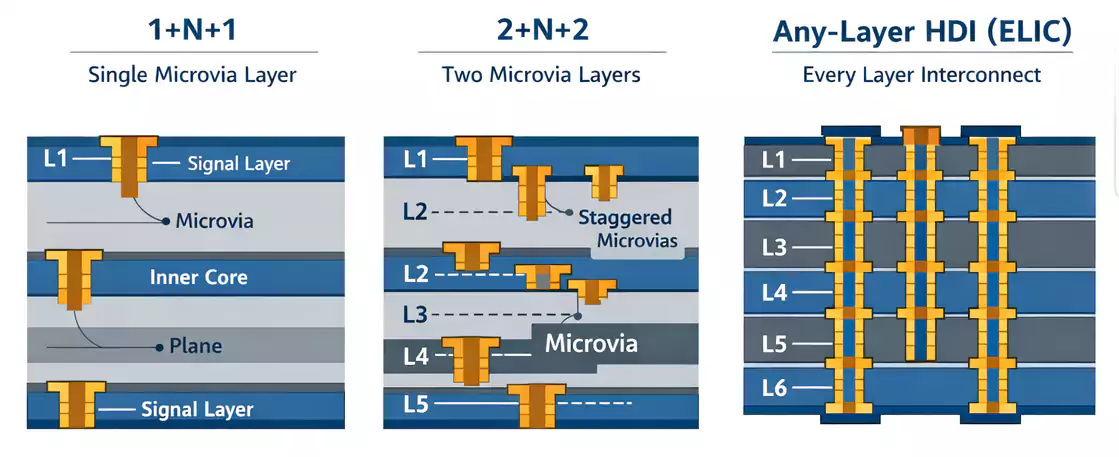

HDI-Strukturtypen

HDI-Aufbauten werden durch die Anzahl der Mikrovia-Schichten über dem Kern definiert.

- Typ I (1+N+1): Eine Mikrovia-Schicht pro Seite des Kerns. Einsatz: Smartphones, IoT-Boards.

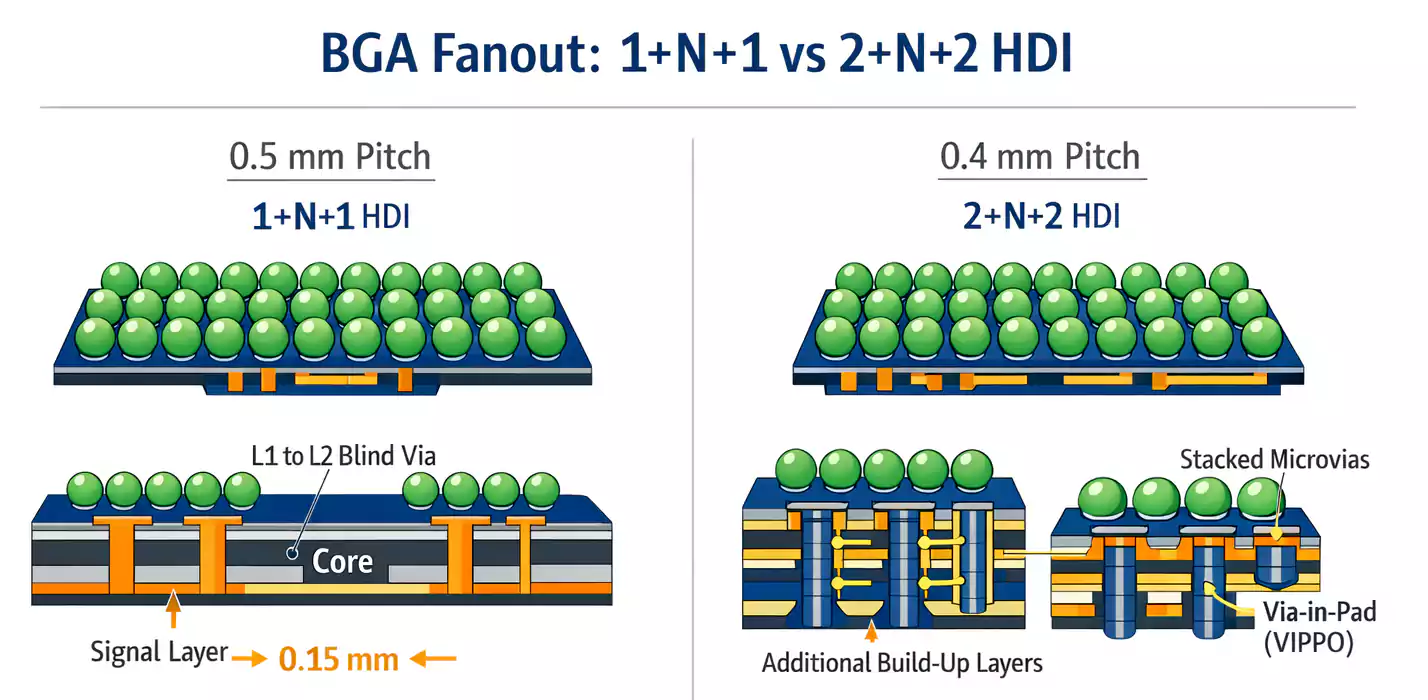

- Typ II (2+N+2): Zwei gestapelte Mikrovia-Schichten pro Seite. Einsatz: dichte BGA-Fan-outs.

- Typ III / ELIC (Any-Layer): Mikrovias zwischen allen Lagen. Einsatz: ICs mit sehr hoher Pin-Zahl.

Gestapelte Mikrovias liegen Lage-für-Lage übereinander; versetzte (staggered) verschieben ihre Position zwischen den Lagen. Versetzte Vias sind einfacher und günstiger zu fertigen; gestapelte sparen mehr Platz, benötigen aber robustere Verkupferung und strengere Prüfung.

Typische HDI-Stack-ups & Impedanzkontrolle

- 1+N+1: je eine Mikrovia-Schicht oben und unten, verbunden mit einem Standard-Kern.

- 2+N+2: zusätzliche Build-up-Schicht auf jeder Seite.

- Any-Layer (ELIC): alle Lagen sind mit gestapelten Mikrovias frei verschaltbar.

Da HDI dünne Dielektrika nutzt, ist Impedanzkontrolle kritisch: Signallagen werden oft engen Referenzebenen (Masse-/Versorgungsflächen) zugeordnet, um definierte Impedanzen für Hochgeschwindigkeitssignale (z. B. PCIe, SerDes) sicherzustellen.

Mikrovia- & Via-in-Pad-Design

Mikrovias sind sehr kleine Blindlöcher (typisch < 0,1 mm), meist lasergebohrt, die nur benachbarte Lagen verbinden (z. B. L1→L2).

Wichtige Via-Arten in HDI:

- Blind Vias: von Außen- zu Innenlage

- Buried Vias: nur zwischen Innenlagen

- Via-in-Pad (VIP/VIPPO): Via direkt im Pad eines Bauteils zur Platzersparnis

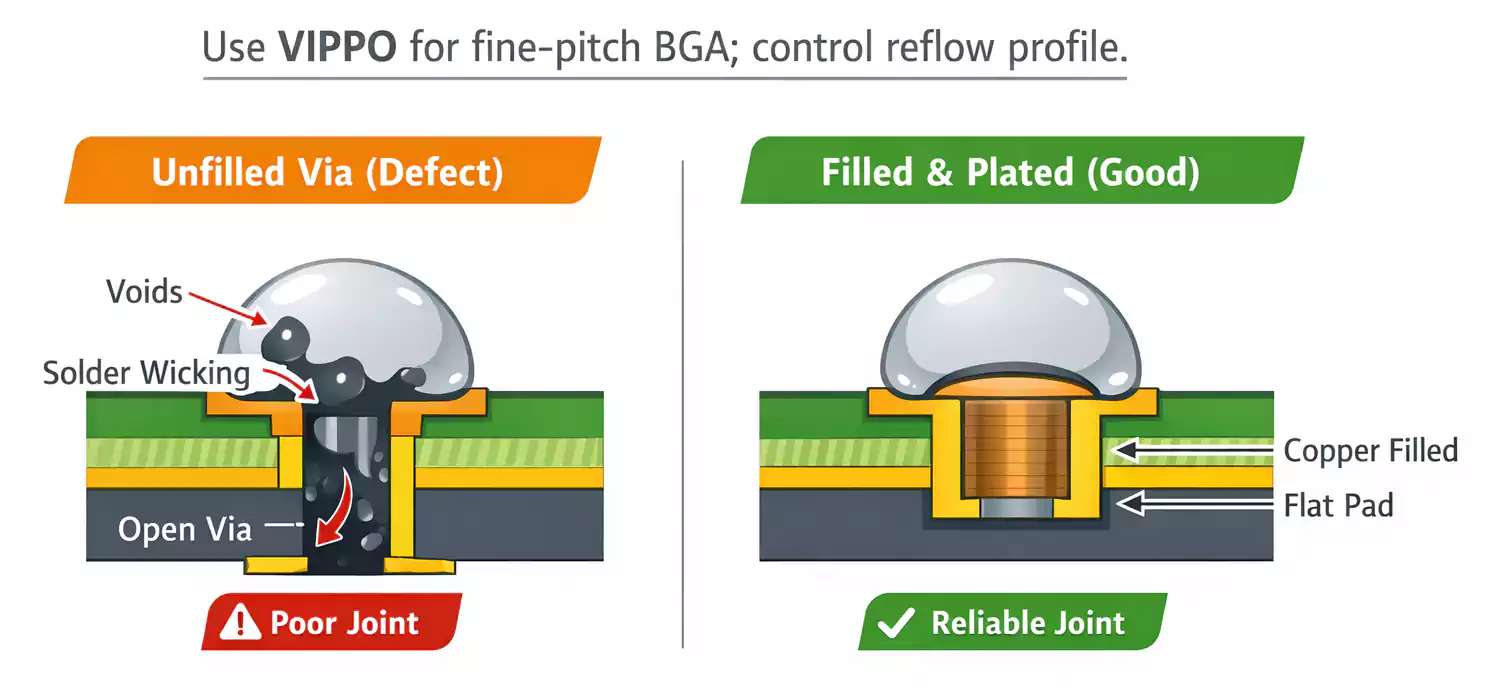

VIP ist bei feinpitchigen BGAs (≤ 0,4 mm) verbreitet. Die Vias werden mit Kupfer oder Epoxid gefüllt und plan übergalvanisiert, sodass eine glatte Lötfläche entsteht.

Worauf Designer achten sollten:

- Ungefüllte Vias können beim Reflow Lotabzug verursachen.

- Zu viele gestapelte Mikrovias erhöhen das Risiko Rissbildung der Kupferschichten bei thermischer Belastung.

Überblick: HDI-Fertigungsprozess

HDI-Boards entstehen stufenweise im Sequential Build-Up (SBU):

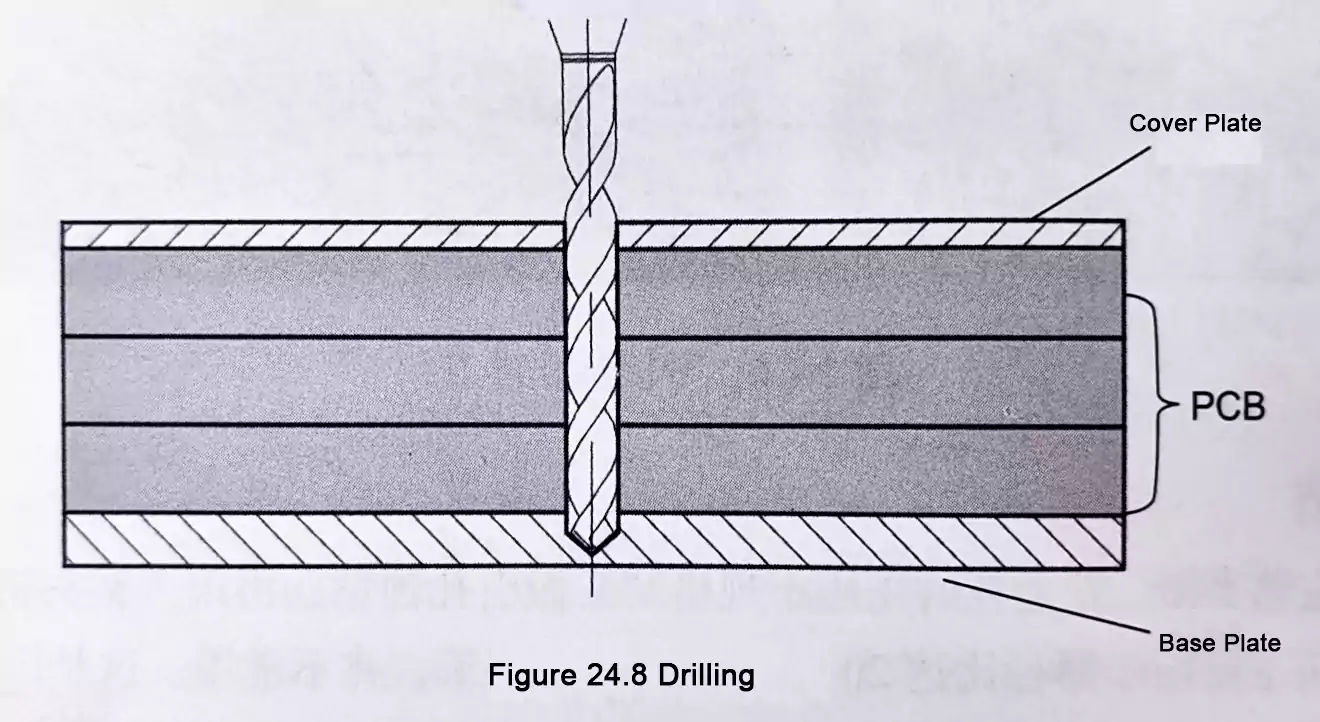

- Kern vorbereiten: Bohren & Metallisieren der Durchkontaktierungen des Kerns

- Build-up-Lagen: Dünne Dielektrika (z. B. RCC, laserbohrbare Prepregs) aufbringen

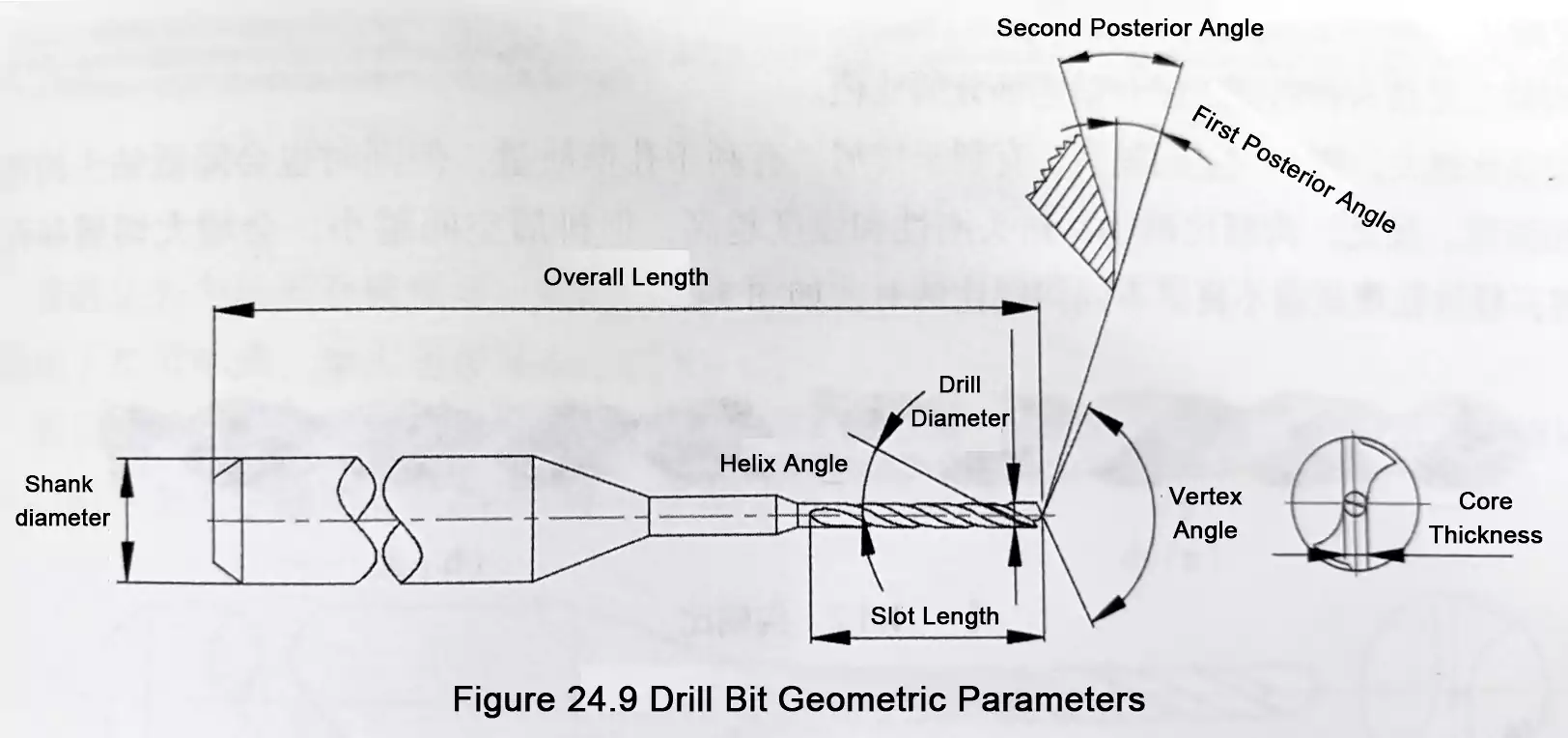

- Laserbohren: Bildung der Mikrovias (< 0,1 mm)

- Entschmieren & Metallisieren: Via-Wände reinigen und verkupfern

- Bildgebung: LDI (Laser Direct Imaging) für ultrafeine Leiterbilder

- Kupferabscheidung & Ätzen: Leiterbilder erzeugen

- Wiederholen für weitere Build-up-Zyklen

- Lötstopp, Endoberfläche und Test

Jeder zusätzliche Build-up-Schritt erhöht Kosten und Komplexität; kosteneffiziente HDI-Boards nutzen häufig eine bis zwei Build-ups pro Seite.

Neue Verfahren wie mSAP (Modified Semi-Additive Process) ermöglichen Leiterbahnen < 30 µm für Ultra-HDI (z. B. 5G-Module, kompakte RF-Systeme).

Zentrale DFM-Regeln für HDI-Designer

(Richtwerte – je nach Hersteller unterschiedlich)

- Mikrovia-Durchmesser: 0,075–0,10 mm

- Aspektverhältnis Mikrovia: ≤ 0,8:1

- Fang-/Ringbreite (Annular Ring): ≥ 0,10 mm

- Leiterbahn/Abstand: 75–100 µm

- Versatz bei gestapelten Vias: ≥ 50 µm zwischen den Vias

- Endkupferdicke: 18–35 µm typisch

Vermeiden Sie > 3 gestapelte Mikrovias in Serie – die Zuverlässigkeit der Galvanik sinkt stark. Nutzen Sie wenn möglich versetzte oder Skip-Vias (L1→L3) zur Risikominimierung und Kostensenkung.

Signal- & Power-Integrität (SI/PI)

Kurze Verbindungswege bei HDI reduzieren parasitäre Effekte und verbessern die Signalintegrität.

Vorteile:

- Weniger Stubs → geringere Reflexion

- Kürzere Rückstrompfade → kleinere Schleifenfläche

- Dichtere Power-/Ground-Paare → weniger Rauschen

Design-Tipps:

- Referenzebenen geschlossen halten.

- Stitching-Vias an Ebenentrennungen/-rändern setzen.

- Bei Differenzialpaaren gleichmäßigen Abstand auch über Vias beibehalten.

- Impedanz früh simulieren – Toleranzen der dünnen Dielektrika sind kleiner.

Zuverlässigkeit & Prüfung

Aufgrund dünner Dielektrika und feiner Vias ist Qualifizierung essenziell.

Typische Probleme:

- Halsrisse in gestapelten Mikrovias durch thermische Zyklen

- Kupferermüdung nach mehreren Reflow-Vorgängen

- CAF-Bildung (Conductive Anodic Filament) bei ungeeigneter Harz/Glas-Kombination

Verifikationsmethoden:

- IST (Interconnect Stress Test)

- Thermoschock/-zyklus

- Röntgen und Schliffbildanalyse

Hochzuverlässige Bereiche (Automotive, Luft-/Raumfahrt, Verteidigung) fordern zusätzliche Nachweise zu Viafüllung und Galvanikqualität.

Materialauswahl für HDI

Die Wahl des Materials beeinflusst Fertigbarkeit und Signalleistung:

- RCC (Resin-Coated Copper): ermöglicht dünne, laserbohrbare Dielektrika

- Laserbohrbare Prepregs: bessere Haftung zwischen Build-up-Schichten

- Spread-Glass-Lamine: höhere Maßstabilität

- Niederverlust-Materialien (Df < 0,005): nötig für SerDes > 10 GHz

- Achten Sie auf ausgewogene CTE und hohe Tg (> 170 °C) für mehrfaches Laminieren und Reflow.

HDI & SMT-Bestückung – wichtige Punkte

- Via-in-Pad muss gefüllt, plan übergalvanisiert sein → keine Hohlräume, kein Lotabzug.

- Solder-Mask-Plugging unter BGAs verhindert Lufteinschlüsse.

- Schablonendesign: Step-Stencils bzw. kleinere Öffnungen für 0201/01005.

- Reflow-Profil: Aufheizrate kontrollieren, um Verzug dünner HDI-Kerne zu vermeiden.

- Thermisches Management ist wegen dichterer Bauteile/Kupferverteilung wichtiger.

Häufige Designfehler & Gegenmaßnahmen

- Zu viele gestapelte Mikrovias → Galvanikrisse → versetzen oder Build-ups reduzieren

- Ungefülltes VIP → Lotabzug, schwache Lötstellen → VIPPO (Kupfer/Epoxid gefüllt, plan)

- Zu kleiner Annular Ring → Ausbrüche beim Bohren → Fangpad vergrößern

- Dünner Kern ohne Ausgleich → Verzug beim Laminieren → Ausgleichslagen/dickeres Prepreg

- Zu geringe Isolationsabstände um Mikrovias → Ätz-Kurzschlüsse → Clearance/Designregeln anpassen

Schlüsselbegriffe

- HDI: High-Density Interconnect

- Microvia: lasergebohrte Via zwischen zwei benachbarten Lagen

- Blind Via / Buried Via: Blind-/vergrabene Via

- VIP / VIPPO: Via-in-Pad (gefüllt, plan übergalvanisiert)

- SBU: Sequential Build-Up

- ELIC: Every Layer Interconnect (Any-Layer HDI)

- mSAP: Modified Semi-Additive Process (ultrafeine Leiterbilder)

Fazit

HDI-Leiterplatten ermöglichen kompakte und zuverlässige Designs.

Durch feine Leiterbilder, optimierte Stack-ups und kontrollierte Via-Strukturen liefern sie Hochgeschwindigkeits-Performance auf kleinem Raum.

Fastturn PCB fertigt HDI-Boards mit mechanischem Mikrobohren, LDI-Belichtung und Mehrlagen-Lamination für Anwendungen in Kommunikation, Automotive und Konsumelektronik.

Fähigkeiten:

- Via-Durchmesser: 0,10 mm (mechanisch)

- Leiterbahn/Abstand: 0,075 mm

- Bis zu 20 Lagen

- Via-Füllung und Oberflächenbeschichtung verfügbar

Mit einem zuverlässigen Fertigungspartner und sauberem Designprozess liefern HDI-PCBs erstklassige elektrische Leistung bei kompakten Bauformen – bereit für die nächste Gerätegeneration.