Die Sicherstellung der Signalintegrität gehört heute zu den wichtigsten Herausforderungen in der modernen Elektronik. Steigen die Datenraten in den Gigahertz-Bereich und werden Signalflanken immer steiler, können selbst kurze Leiterbahnen auf einem kundenspezifischen PCB wie Übertragungsleitungen wirken. In diesem Fall können unkontrollierte Impedanzschwankungen Reflexionen, Signalverluste, Timing-Fehler und elektromagnetische Störungen (EMI) verursachen.

Genau hier kommen PCBs mit kontrollierter Impedanz ins Spiel.

Dieser Leitfaden vermittelt Ihnen ein praxisnahes, technisch verständliches Verständnis zu folgenden Punkten:

- Wann kontrollierte Impedanz tatsächlich erforderlich ist

- Wie Leiterbahnen mit kontrollierter Impedanz ausgelegt und geroutet werden

- Wie Sie Ihre Anforderungen einem PCB-Hersteller eindeutig vorgeben

- Wie die Impedanz in der Fertigung verifiziert wird

- Welche typischen Fehler zu Fehlproduktionen, Mehrkosten und Redesigns führen

Ganz gleich, ob Sie eine High-Speed-Digitalschnittstelle, eine RF-Schaltung oder ein Produkt für FCC-/EMV-Tests entwickeln – dieser Leitfaden bietet Ihnen einen umfassenden Überblick.

Was ist ein PCB mit kontrollierter Impedanz?

Ein PCB mit kontrollierter Impedanz ist eine Leiterplatte, bei der bestimmte Leiterbahnen so ausgelegt werden, dass sie eine vorgegebene elektrische Impedanz einhalten – typischerweise 50 Ω für Single-Ended-Leitungen sowie 90 Ω oder 100 Ω für differentiell geführte Paare.

Impedanz ist nicht dasselbe wie Widerstand.

Sie beschreibt den Wechselstromwiderstand (AC) bei hohen Frequenzen und wird im Wesentlichen beeinflusst durch:

- die Geometrie der Leiterbahn (Breite, Dicke, Abstand)

- die dielektrischen Eigenschaften und Dicken der PCB-Materialien

Kurz gesagt: Eine stabile Impedanz ist wichtig, weil:

- bei hohen Frequenzen jede Leiterbahn wie eine Übertragungsleitung wirkt,

- ein sprunghafter Anstieg oder Abfall der Impedanz entlang des Signalpfads zu Reflexionen führt,

- diese Reflexionen die Signalform verzerren, Timing-Reserven verringern und EMI erhöhen.

Ein PCB mit kontrollierter Impedanz sorgt dafür, dass das Signal vom Treiber bis zum Empfänger eine möglichst konstante elektrische Umgebung vorfindet.

Wann benötigen Sie kontrollierte Impedanz?

Nicht jede Leiterbahn auf einem PCB muss impedanzkontrolliert sein. Wenn Ihr System jedoch High-Speed- oder Hochfrequenzsignale verarbeitet, wird eine stabile Impedanz entscheidend.

1. Kontrollierte Impedanz ist in der Regel erforderlich bei:

- High-Speed-Digitalschnittstellen: PCIe, DDR, HDMI, USB 3.x, Ethernet (1G/2,5G/10G), SATA

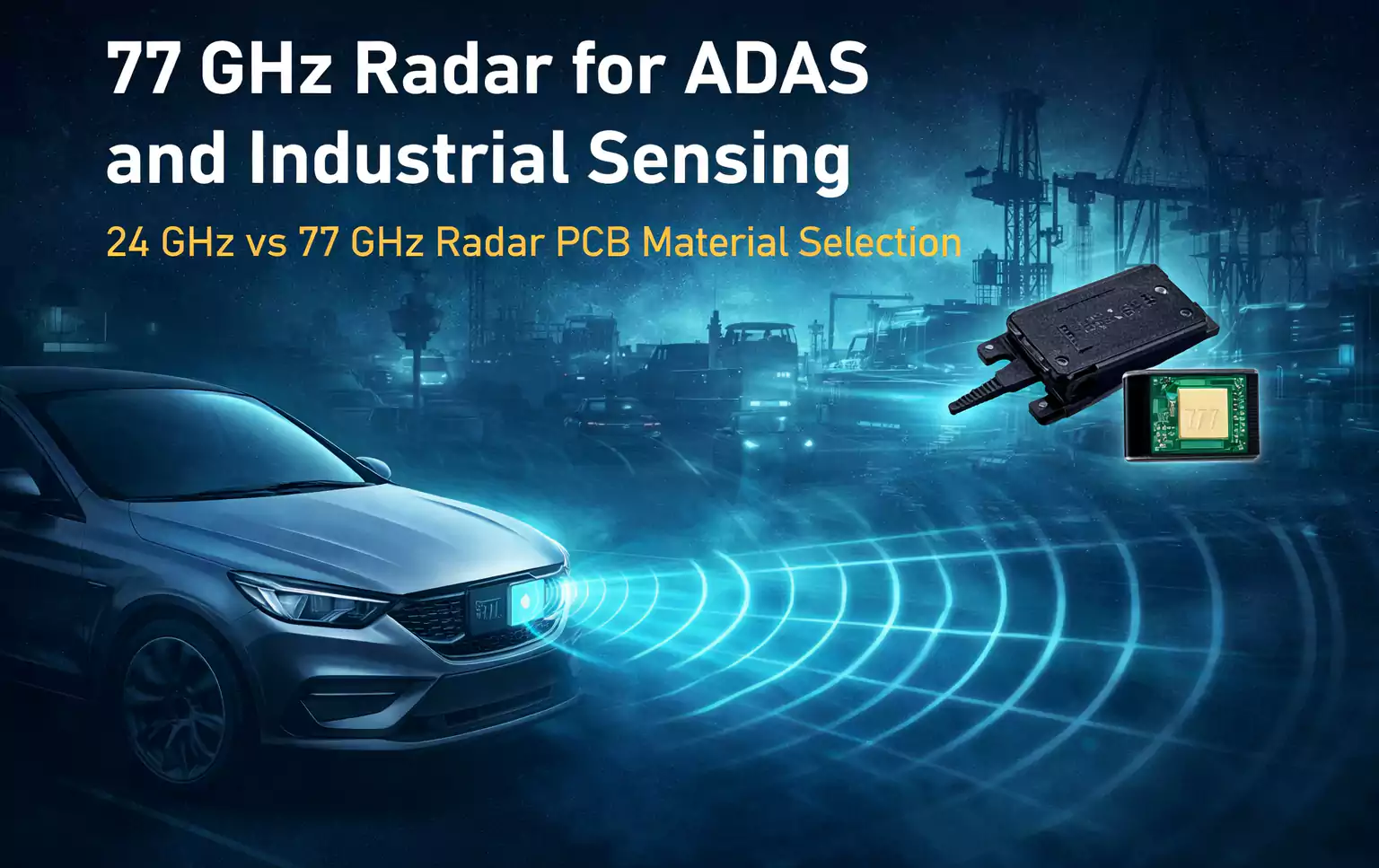

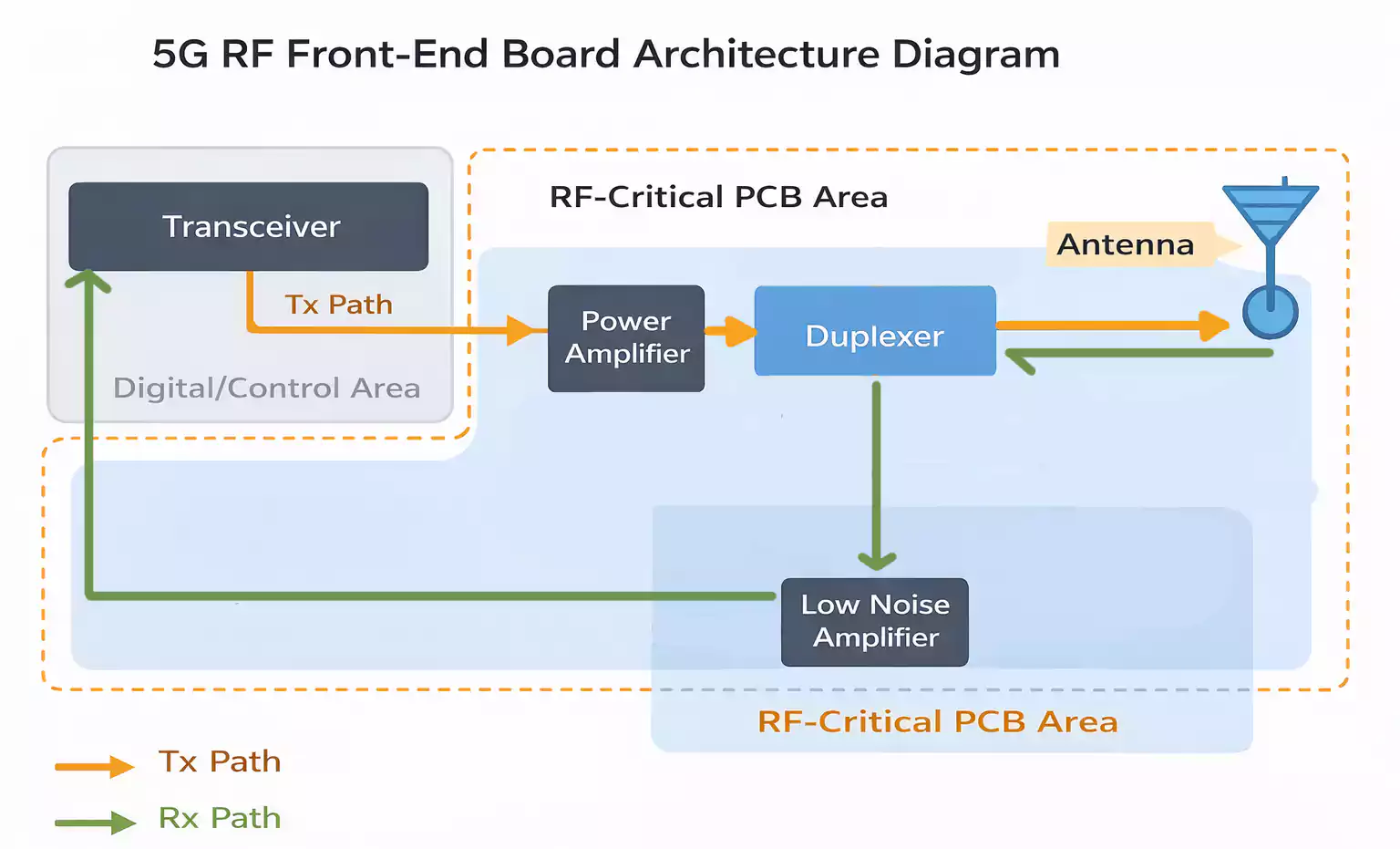

- RF- und Mikrowellensystemen (Mobilfunk, Radar, GNSS, rauscharme Verstärker, Leistungsverstärker)

- differentieller Signalübertragung (LVDS, USB-Differenzialpaare, High-Speed-SerDes)

- längeren Leiterbahnen, bei denen die Laufzeit des Signals relevant wird

- rauscharmen Analog-Front-Ends mit Anforderungen an eine konstante Leitungsimpedanz

- Produkten, die EMI-/EMV-Compliance-Tests bestehen müssen

2. Kontrollierte Impedanz ist möglicherweise nicht erforderlich, wenn:

- Signale mit sehr niedrigen Frequenzen arbeiten (kHz bis niedriger MHz-Bereich)

- die Leiterbahnen extrem kurz sind

- das Signal nicht empfindlich auf steile Flanken reagiert

- laut Datenblatt keine Impedanzanpassung zwischen Treiber und Empfänger gefordert ist

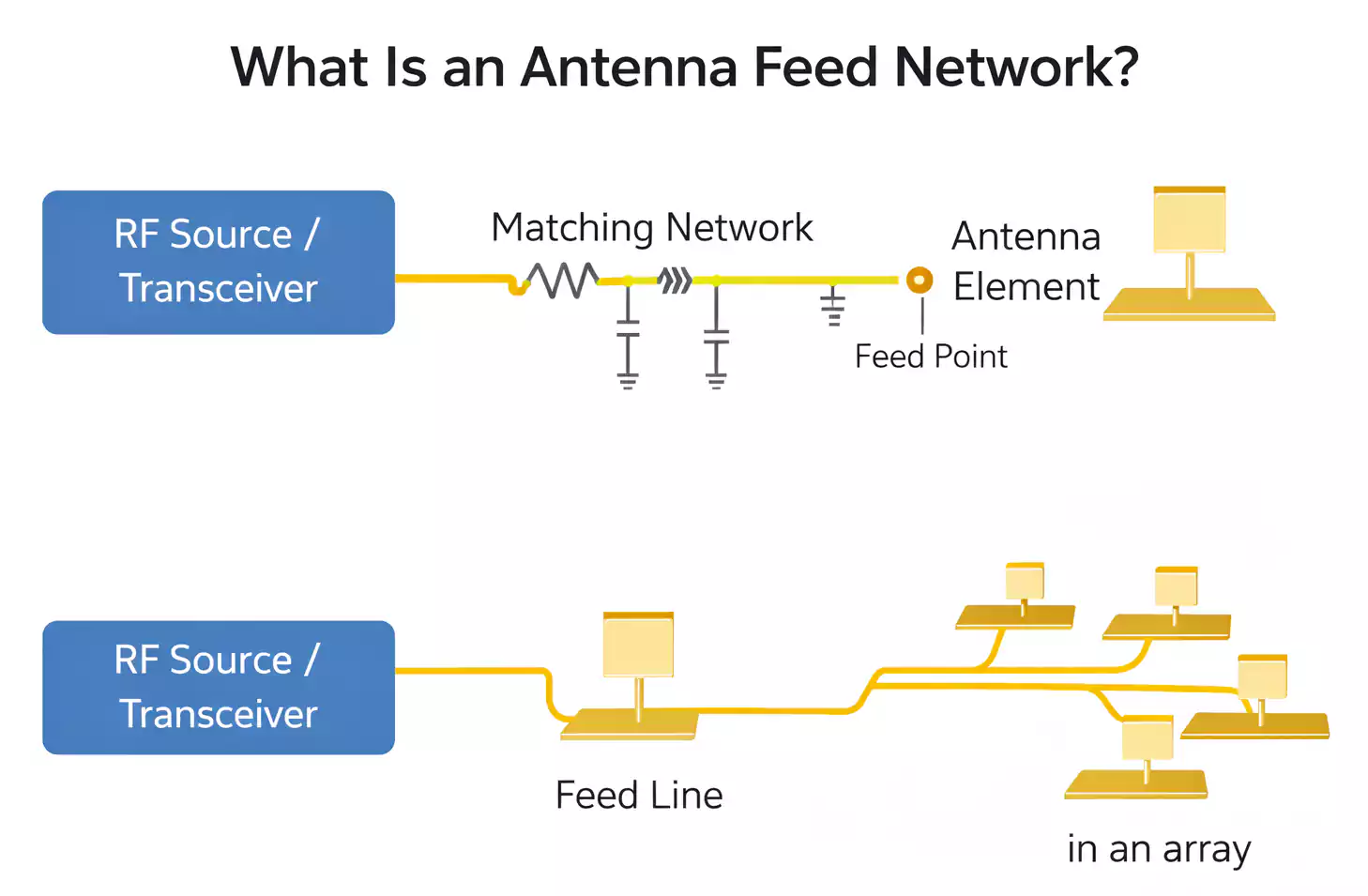

Gängige Strukturen für kontrollierte Impedanz

Unterschiedliche Routing-Layer und Geometrien führen zu unterschiedlichem Impedanzverhalten. Zu den häufigsten Strukturen gehören:

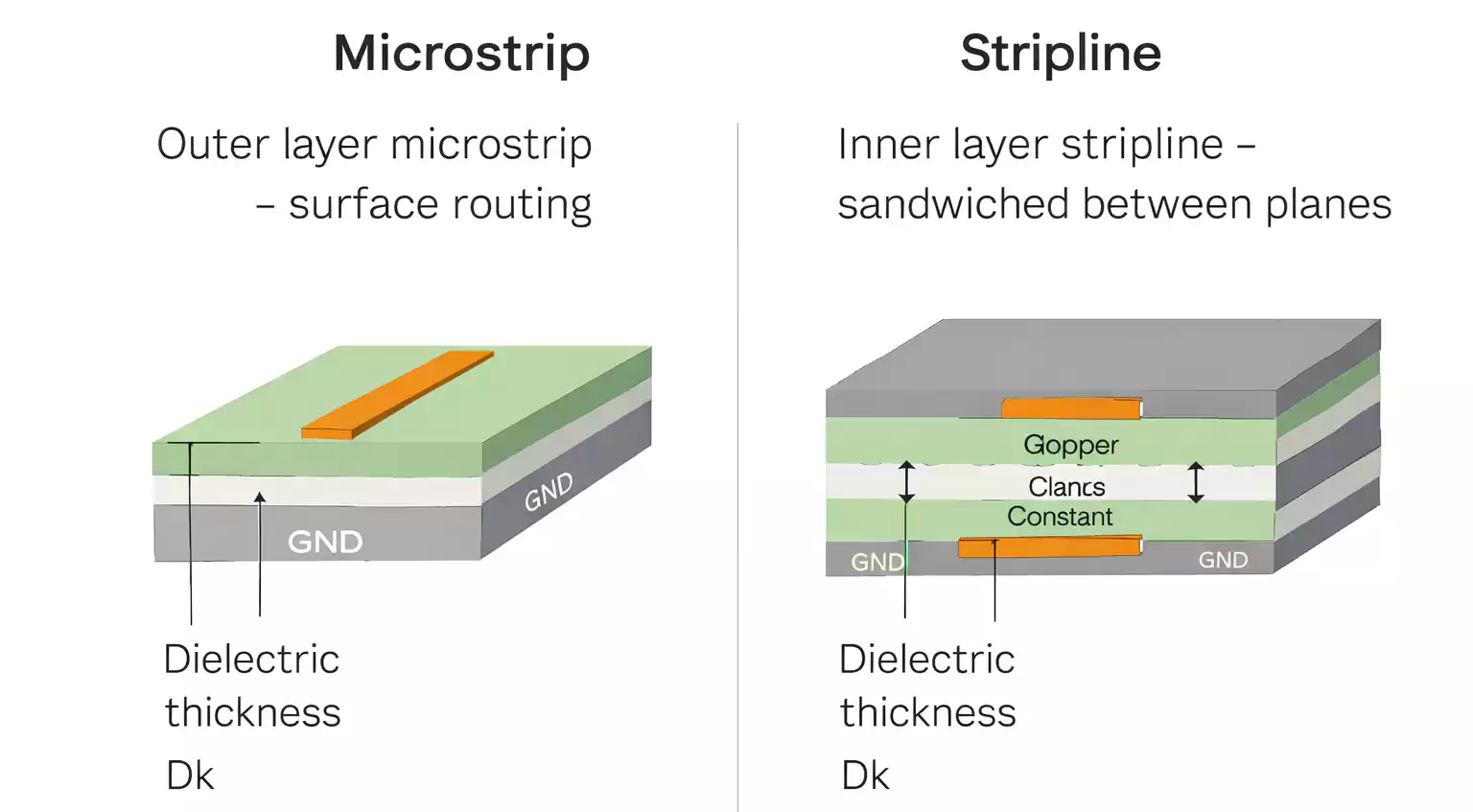

1. Microstrip (Routing auf Außenlagen)

Ein Microstrip ist eine Leiterbahn auf einer Außenlage mit einer Referenzebene direkt darunter.

- geringere EMI-Abschirmung

- leichter zugänglich und einfacher nachzuarbeiten

- die Impedanz wird von der Lötstoppmaskendicke beeinflusst

2. Stripline (Routing auf Innenlagen)

Eine Stripline liegt zwischen zwei Referenzebenen eingebettet.

- sehr gute Isolation

- konstantere Impedanz

- für dieselbe Zielimpedanz sind meist kleinere Leiterbahnbreiten erforderlich

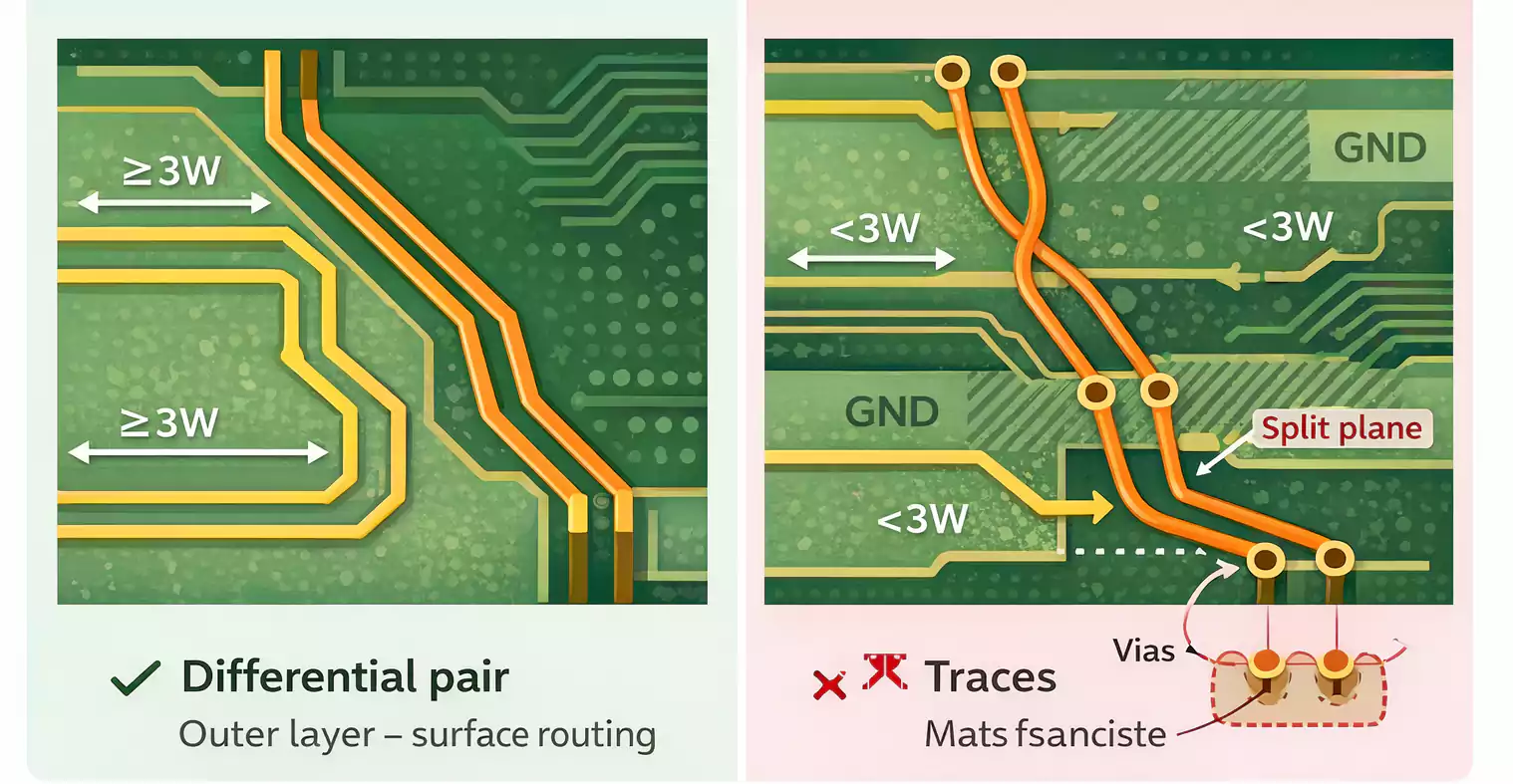

3. Differenzialpaare

Zwei Leiterbahnen führen gleich große, aber gegensinnige Signale.

Die Impedanz hängt dabei ab von:

- der Geometrie jeder einzelnen Leiterbahn

- dem Abstand zwischen den beiden Leiterbahnen

- der Symmetrie (sehr wichtig)

4. Coplanar Waveguide (CPW)

Hier befinden sich zusätzliche Masseflächen seitlich neben der Leiterbahn.

Diese Struktur ist besonders geeignet für:

- RF-Designs

- Anwendungen mit engen Impedanzvorgaben

- dicht gepackte Layouts

Das Verständnis dieser Strukturen hilft dabei, geeignete Leiterbahnbreiten, Abstände und den richtigen Stack-up festzulegen.

Welche Faktoren beeinflussen die PCB-Impedanz?

Mehrere geometrische und materialbezogene Parameter bestimmen, ob eine Leiterbahn ihre Zielimpedanz erreicht.

1. Leiterbahnbreite

Breitere Leiterbahnen senken die Impedanz, schmalere erhöhen sie.

2. Leiterbahnabstand (bei Differenzialpaaren)

- Ein kleinerer Abstand führt zu stärkerer Kopplung und damit zu niedrigerer differentieller Impedanz

- Ein größerer Abstand reduziert die Kopplung und erhöht die differentielle Impedanz

3. Kupferdicke

Dickeres Kupfer senkt die Impedanz.

So benötigen 1-oz-Kupferlagen oft breitere Leiterbahnen, um 50 Ω zu erreichen, als 0,5-oz-Kupfer.

4. Dielektrikumsdicke (Abstand zur Referenzebene)

Je größer der Abstand der Leiterbahn zur Massefläche, desto höher ist die Impedanz.

5. Dielektrizitätskonstante (Dk / Er)

Hochfrequenzmaterialien mit niedrigerem Dk (z. B. Rogers) führen bei gleicher Geometrie in der Regel zu höherer Impedanz als FR-4.

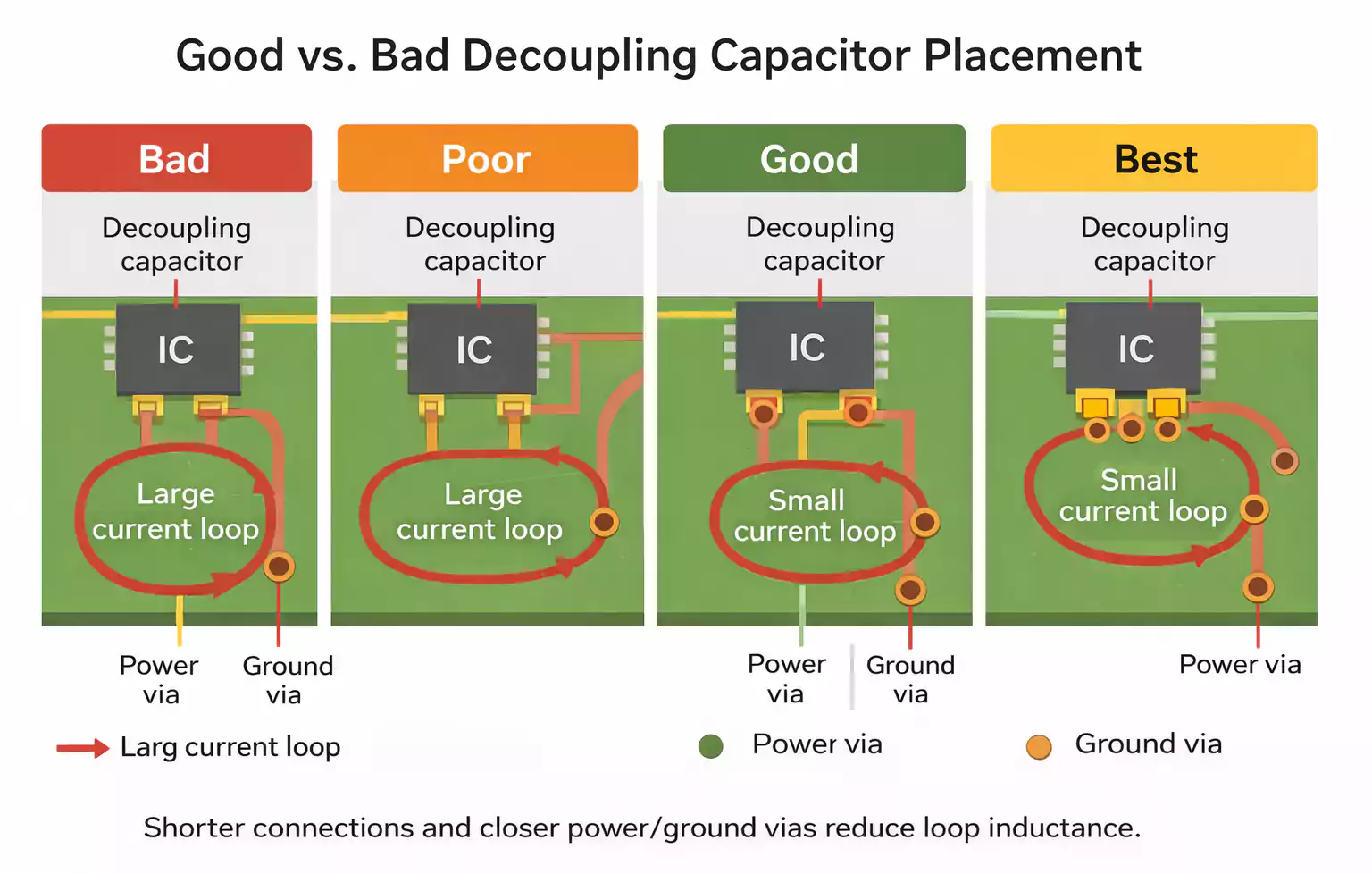

6. Kontinuität der Referenzebene

Eine Lücke oder ein Schlitz in der Referenzebene führt sofort zu Impedanzsprünge, was Reflexionen und EMI verstärkt.

7. Fertigungstoleranzen

Selbst bei einem perfekten Design verursachen Kupferätzprozesse, Schwankungen der Prepreg-Dicke und Unterschiede im Harzanteil gewisse Impedanzabweichungen – typischerweise ±10 %, sofern keine engere Toleranz vereinbart wurde.

Ablauf für das Design eines PCBs mit kontrollierter Impedanz

Ein zuverlässiger Ansatz beginnt lange bevor die erste Leiterbahn geroutet wird.

Schritt 1 – Festlegen, welche Netze kontrollierte Impedanz benötigen

Prüfen Sie Datenblätter und Anforderungen der verwendeten Schnittstellen.

Identifizieren Sie dabei insbesondere:

- Differenzialpaare

- High-Speed-Seriell-Netze

- Taktnetze

- RF-Signalpfade

Schritt 2 – Den Stack-up vor dem Routing definieren

Die Impedanz hängt stark ab von:

- der Anzahl der Lagen

- der Position der Signallage

- der Kupferdicke

- der Dielektrikumsdicke

- dem verwendeten Material (FR-4, High-Tg, Low-Loss, PTFE, Rogers usw.)

Beginnen Sie nicht mit dem Routing, bevor der Stack-up festgelegt ist.

Schritt 3 – Leiterbahnbreite und Abstand berechnen

Verwenden Sie einen Field Solver oder einen Impedanzrechner, der Folgendes unterstützt:

- Microstrip / Stripline

- differentielle Impedanz

- CPW

- Einfluss der Lötstoppmaske

Je nach Lage kann eine andere Leiterbahnbreite erforderlich sein, um 50 Ω / 100 Ω zu erreichen.

Schritt 4 – Anforderungen eindeutig dokumentieren

Fügen Sie Impedanzangaben hinzu in:

- Schaltplan

- Layer-Stack-Manager

- Fertigungsnotizen

- Gerber-Begleitdokumentation oder Fertigungszeichnungen

Es muss klar ersichtlich sein, welche Netze impedanzkontrolliert sind und welche Zielwerte gelten.

Schritt 5 – SI-/DFM-Prüfung vor der Freigabe

Kontrollieren Sie unter anderem:

- Unterbrechungen in Referenzebenen

- zu viele Via-Übergänge

- Längenunterschiede

- abrupte Geometrieänderungen

- ungleichmäßige Abstände

Eine kurze Überprüfung vor der Fertigung kann teure Nacharbeit vermeiden.

Best Practices für das Routing mit kontrollierter Impedanz

Gerade im Routing geht die Impedanzkontrolle oft verloren. Die folgenden Regeln helfen, die gewünschte Performance sicherzustellen.

1. Differenzialpaare symmetrisch führen

Achten Sie auf:

- gleiche Leiterbahnbreiten

- gleiche Abstände

- parallele Führung

- angeglichene Längen

Symmetrie ist entscheidend, um Common-Mode-Störungen zu reduzieren.

2. Ausreichenden Abstand zu anderen Signalen einhalten

Allgemeine Richtwerte:

- andere Leiterbahnen mindestens im Abstand von 3W halten (dreifache Leiterbahnbreite)

- bei besonders empfindlichen Differenzialpaaren 5W verwenden

So wird Übersprechen minimiert.

3. Keine Splits oder Lücken in Referenzebenen kreuzen

Wird ein Split in einer Innenlage überquert, muss der Rückstrom einen längeren Weg nehmen. Das führt zu:

- Reflexionen

- stärkerer EMI-Abstrahlung

- Timing-Problemen

Daher sollte immer eine möglichst durchgehende Referenzebene vorhanden sein.

4. Via-Übergänge minimieren

Jedes Via erzeugt eine kleine Impedanzstörung.

Wenn ein Lagenwechsel unvermeidbar ist, sollte die Anzahl der Vias auf beiden Leitern eines Differenzialpaars identisch sein.

5. Längen von Differenzialpaaren anpassen

Längenausgleich sollte möglichst nahe an der Quelle der Abweichung erfolgen.

Vermeiden Sie Serpentinen in Bereichen mit starker Kopplung zu benachbarten Netzen.

6. Eindeutige Leiterbahnbreiten für impedanzkontrollierte Netze verwenden

Ein kleiner, aber sehr wirksamer Tipp:

Wählen Sie z. B. 5,1 mil statt 5,0 mil.

Dadurch kann Ihr Fertiger impedanzkontrollierte Netze in der CAM-Prüfung schneller identifizieren.

Wie wird kontrollierte Impedanz in der Fertigung verifiziert?

PCB-Hersteller prüfen die Impedanz über Testcoupons, nicht direkt an den Signalleiterbahnen des eigentlichen Produkts.

1. Testcoupons

Testcoupons bilden die Geometrie Ihrer impedanzkontrollierten Leiterbahnen nach und werden am Rand des Fertigungspanels platziert.

2. TDR (Time Domain Reflectometry)

Ein schneller elektrischer Impuls wird durch den Coupon geschickt. Aus den entstehenden Reflexionen lässt sich bestimmen, ob die Zielimpedanz erreicht wird.

3. Wann kommt ein VNA zum Einsatz?

Vector Network Analyzer (VNA) werden hauptsächlich bei höherfrequenten RF-Anwendungen verwendet.

4. Warum werden nur Coupons gemessen?

Die tatsächlichen Signalleiterbahnen zu messen würde bedeuten, die Leiterplatte zu beschädigen oder aufzutrennen.

Testcoupons liefern eine identische Struktur, ohne das Endprodukt zu beeinträchtigen.

Häufige Fehler, die vermieden werden sollten

- Routing beginnen, bevor der Stack-up final festgelegt ist

- nicht angeben, welche Netze kontrollierte Impedanz benötigen

- widersprüchliche Angaben in verschiedenen Unterlagen

- unrealistische Toleranzen festlegen

- Vias oder Bauteile zwischen die Leiter eines Differenzialpaars setzen

- Splits in Strom- oder Masseflächen kreuzen

FAQ

Benötigen alle High-Speed-Leiterbahnen kontrollierte Impedanz?

Nein. Nur Signale, bei denen Reflexionen die Funktion beeinträchtigen – typischerweise High-Speed-Seriellschnittstellen, Taktleitungen, RF-Leitungen oder Differenzialpaare.

Was ist der Unterschied zwischen Single-Ended- und differentieller Impedanz?

Die Single-Ended-Impedanz wird gegenüber der Referenzebene gemessen.

Die differentielle Impedanz wird zwischen zwei komplementären Leiterbahnen gemessen.

Kann der PCB-Hersteller die Leiterbahnbreite anpassen?

Ja, sofern Sie dies ausdrücklich zulassen. Viele Entwickler erlauben dem Hersteller, die Breite anhand realer Materialien und Fertigungsparameter feinzujustieren.

Welche Toleranz sollte ich wählen?

±10 % ist der übliche Standard.

±5 % erfordert spezialisiertere Prozesse und kann die Kosten erhöhen.

Was ist der Unterschied zwischen Controlled Dielectric und Controlled Impedance?

Controlled Dielectric bedeutet, dass Sie die Dicke des Materialaufbaus sehr genau festlegen.

Controlled Impedance bedeutet, dass der Hersteller die Geometrie so anpasst, dass ein definierter Zielwert erreicht wird – mithilfe eigener Berechnungstools und Prüfverfahren.

Fazit

Kontrollierte Impedanz ist längst nicht mehr nur für RF-Spezialisten relevant – sie ist heute für nahezu jedes moderne digitale und kommunikationstechnische Produkt von Bedeutung. Mit einer sauberen Stack-up-Planung, konsequenten Routing-Regeln und klarer Kommunikation mit Ihrem PCB-Lieferanten wird kontrollierte Impedanz zu einem beherrschbaren und planbaren Bestandteil Ihres Entwicklungsprozesses.

Wenn Sie eine zuverlässige Fertigung für kundenspezifische PCBs mit kontrollierter Impedanz benötigen, bietet FastTurnPCB kompetente DFM-Unterstützung, schnelle Fertigung (Quick-Turn) und präzise Impedanzprüfungen, damit Ihr Design die gewünschte Performance erreicht.