Wenn Sie eine Leiterplatte entwickeln, die sich sauber fertigen lässt, EMI-Anforderungen besteht und sich in realer Hardware stabil verhält, darf das Layout kein „Nachgedanke“ sein. Starke PCB-Designregeln – insbesondere rund um Platzierung, Routing und Kupfergeometrie – machen aus einem korrekten Schaltplan ein zuverlässiges Produkt.

Dieser Artikel ist ein praxisnahes Set an PCB-Designregeln mit drei Grundlagen: PCB-Bauteilplatzierung, PCB-Routingregeln sowie Leiterbahnbreite und -abstand.

1. Regeln zur PCB-Bauteilplatzierung (PCB Component Placement Rules)

PCB-Bauteilplatzierung bedeutet, Bauteile entsprechend der funktionalen Absicht des Schaltplans und den mechanischen Abmessungen der jeweiligen Gehäuse zu positionieren. Die Qualität der Platzierung beeinflusst die Ausbeute in der Montage, den Aufwand für Debug/Repair sowie die elektrische Gesamtperformance.

Befolgen Sie diese PCB-Designregeln für die Platzierung:

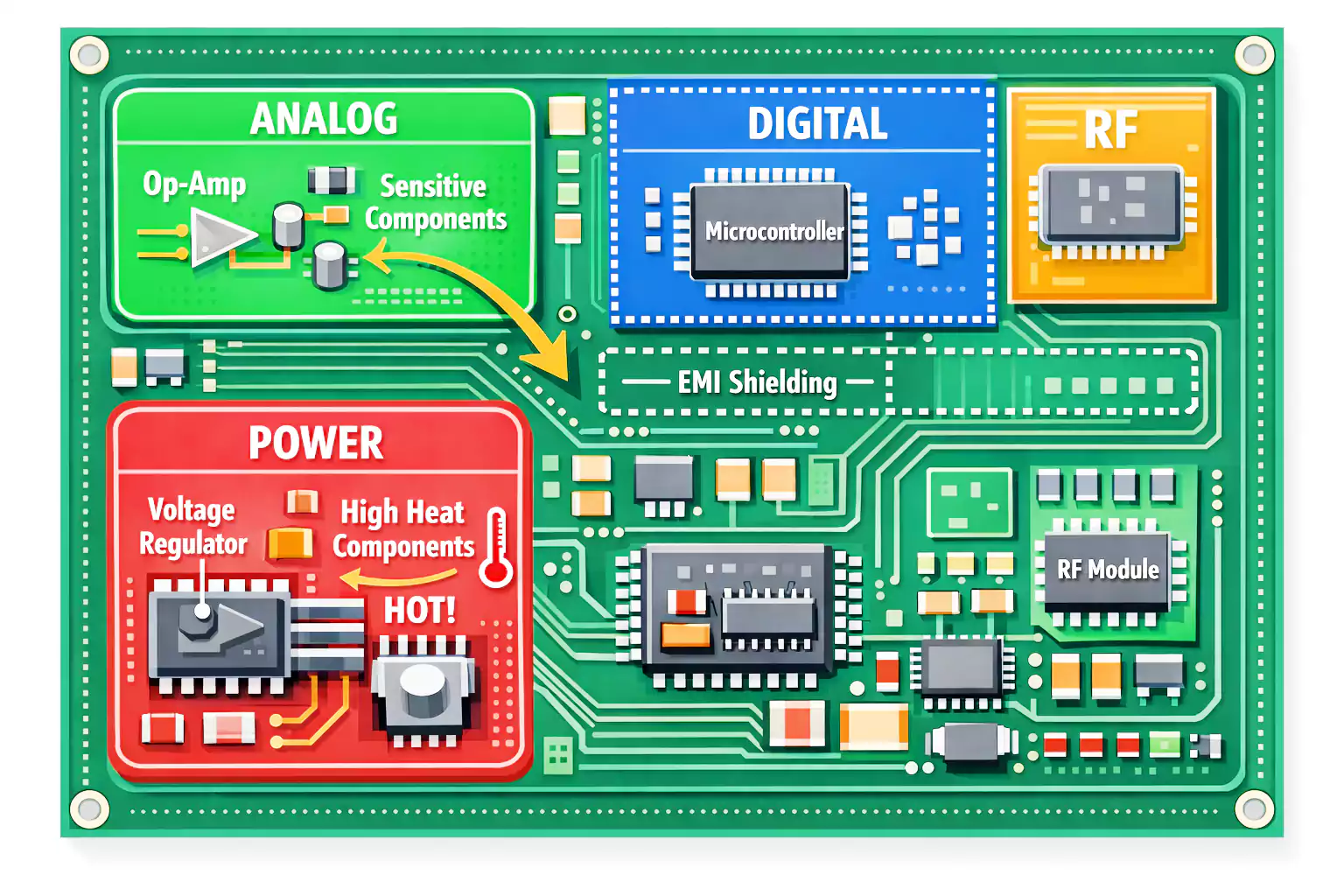

(1) Platzierung gleichmäßig halten; Bauteile nach Funktion gruppieren

- Bauteile gleichmäßig und sauber verteilen.

- Bauteile innerhalb desselben Funktionsblocks zusammenhalten und relativ nahe platzieren – das erleichtert Test, Fehlersuche und Service.

(2) Elektrisch verbundene Bauteile nahe beieinander platzieren, um Routinglängen zu reduzieren

- Bauteile, die miteinander verbunden sind, sollten möglichst nah beieinander liegen.

- Kürzere Verbindungen erhöhen die Routingdichte und helfen, parasitäre Effekte zu minimieren.

(3) Wärmeempfindliche Bauteile von Wärmequellen trennen

- Temperaturkritische Bauteile von Hochleistungsbauteilen und anderen starken Wärmequellen fernhalten, um Drift zu reduzieren und die Stabilität zu verbessern.

(4) Bauteile, die EMI-Probleme verursachen können, isolieren oder abschirmen

- Für Bauteile mit potenzieller elektromagnetischer Beeinflussung je nach Bedarf Abstand, Abschirmung oder Isolation einsetzen.

2. PCB-Routingregeln (PCB Routing Rules)

Routing ist der Schritt, in dem PCB-Designregeln zu realem Kupfer werden. Gutes Routing reduziert Störungen, begrenzt Kopplung und verbessert die Fertigbarkeit.

(1) Lagen in dieser Reihenfolge wählen: einlagig → doppellagig → multilayer

Solange die Anforderungen erfüllt werden, bevorzugen Sie zunächst einfachere Stackups:

- Einlagig, dann zweilagig, dann mehrlagiges Routing.

(2) Leiterbahnen kurz halten; empfindliche/kleine Signale zuerst routen

- Leiterbahnen zwischen Pads so kurz wie möglich halten.

- Empfindliche und kleine Signale zuerst routen, um Verzögerung und Störeinflüsse zu reduzieren.

- In Analog-Bereichen bei Bedarf eine Masseleitung parallel zu Eingangsleitungen als Abschirmung führen.

- Routing auf derselben Lage gleichmäßig verteilen und die Kupferfläche möglichst ausbalancieren, um das Risiko von Verzug (Warpage) zu reduzieren.

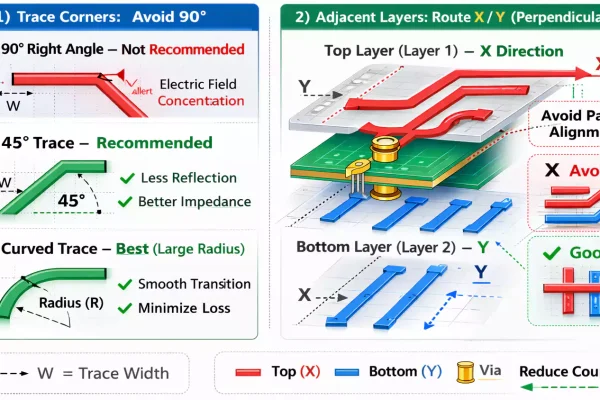

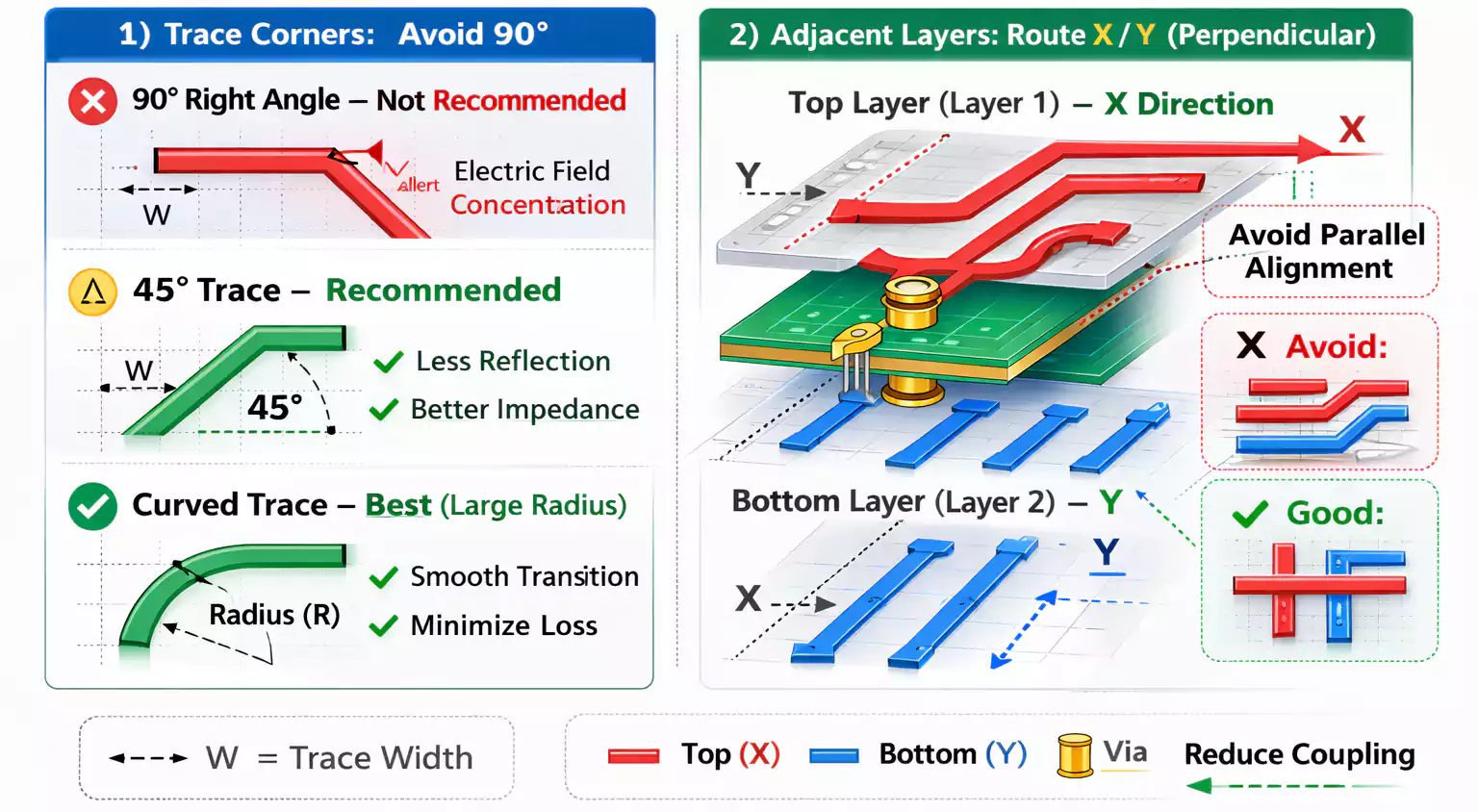

(3) Scharfe Ecken vermeiden: 45°-Winkel oder sanfte Bögen verwenden

- Richtungswechsel mit 45°-Winkeln oder glatten Kurven mit größerem Radius ausführen.

- Das hilft, Feldkonzentration, Reflexionen und zusätzliche Impedanz-Diskontinuitäten zu vermeiden.

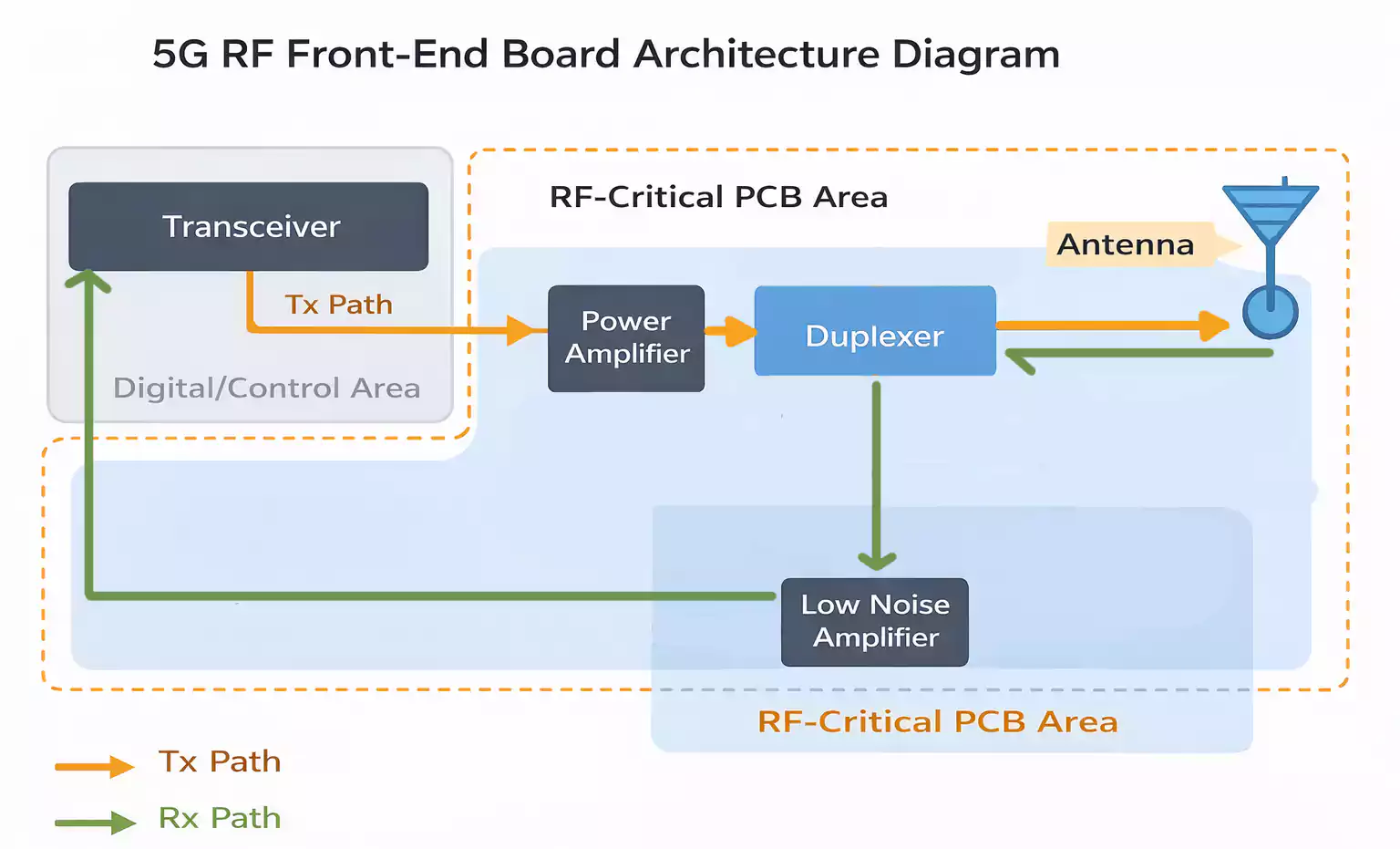

(4) Digital und Analog getrennt routen – und deren Power/GND-Systeme ebenfalls trennen

- Digitale und analoge Bereiche getrennt routen, um gegenseitige Beeinflussung zu verhindern.

- Wenn beide Bereiche eine Lage teilen, Power-Verteilung und Masse-Verteilung getrennt führen.

- Bei Signalen unterschiedlicher Frequenzen kann eine Masseleitung dazwischen helfen, Übersprechen zu reduzieren.

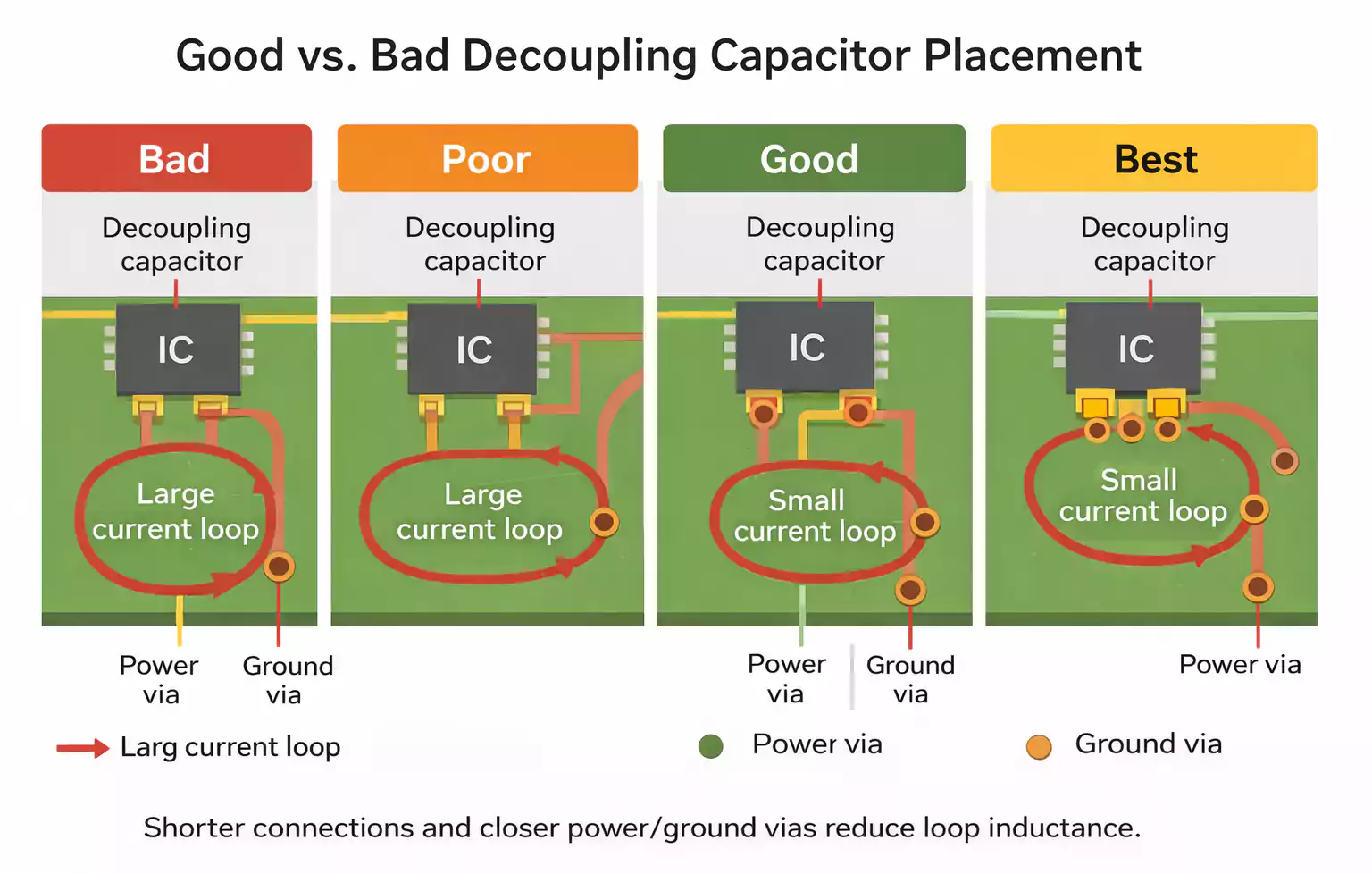

(5) Power- und GND-Anbindungen kurz und nah halten

- Kurzes, nahes Power/GND-Routing reduziert den Innenwiderstand.

(6) Benachbarte Lagen orthogonal (X/Y) routen; parallele Überlappung vermeiden

- Auf benachbarten Lagen orthogonale Routingrichtungen nutzen, um Kopplung zu reduzieren.

- Lange parallele Strecken vermeiden und Leiterbahnen nicht direkt übereinander (oben/unten) ausrichten.

(7) Längenabgleich für kritische High-Speed-I/O sowie symmetrische/differenzielle Pfade

- High-Speed-Multi-I/O und symmetrische/differenzielle I/O-Pfade sollten gleich lang sein, um unerwünschte Verzögerungsunterschiede oder Phasenverschiebungen zu vermeiden.

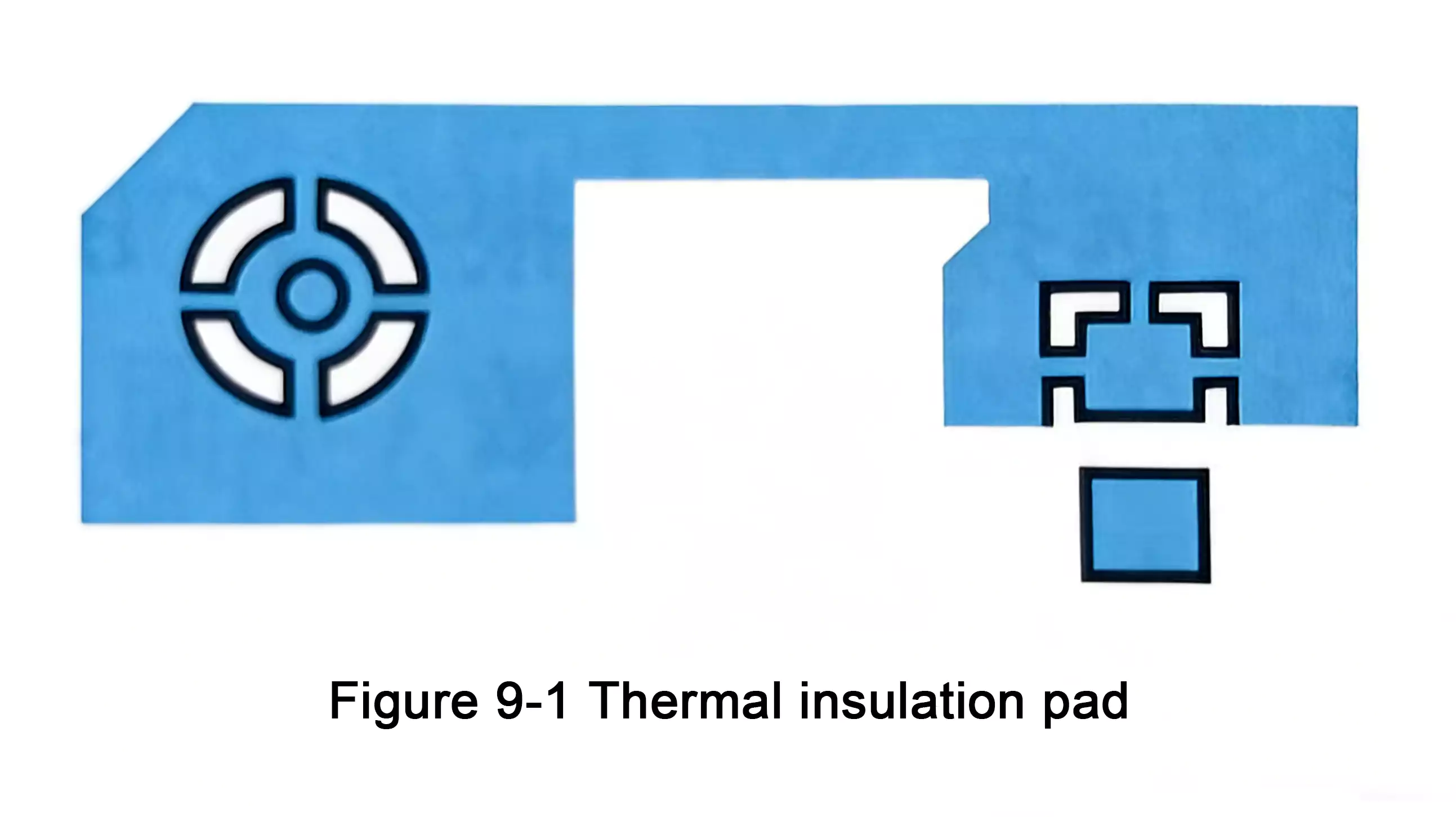

(8) Thermal-Relief für Pads an großen Kupferflächen – außer bei > 5 A

Für Pads, die an große Kupferflächen angebunden sind, Thermal-Relief verwenden:

- Speichenlänge ≥ 0,5 mm

- Speichenbreite ≥ 0,13 mm

- Kein Thermal-Relief für Pads, die mehr als 5 A führen.

(9) Leiterbahn-zu-Kantenabstand einhalten

- Die nächstgelegenen Leiterbahnen sollten in der Regel > 5 mm von der Leiterplattenkante entfernt sein.

- Masseleitungen dürfen bei Bedarf näher an die Kante.

- Wenn die Leiterplatte in Führungsschienen (Rails/Guides) eingeschoben wird, muss der Abstand größer als die Nut-/Schlitz-Tiefe der Führung sein.

(10) Power und Masse auf niedrige Impedanz auslegen (2-Lagen und Multilayer)

- Bei zweilagigen Leiterplatten gemeinsame Power- und Masseführung nahe an der Kante platzieren und – wenn möglich – auf beiden Seiten verteilen, um niedrige Impedanz zu erreichen.

- Bei Multilayer-Boards dedizierte Power-/GND-Planes nutzen und über durchkontaktierte Vias anbinden.

- Große Kupferflächen in Innenlagen (Power/GND) können als Mesh-Pattern ausgeführt werden, um die Verbundfestigkeit zwischen den Lagen zu verbessern.

(11) Breakpoints und Testpunkte für einfaches Testen ergänzen

- Erforderliche Breakpoints und Testpunkte vorsehen, um Validierung und Produktionstests zu vereinfachen.

3. Leiterbahnbreite und -abstand (Trace Width and Spacing)

Die Leiterbahnbreite hängt von Laststrom, zulässiger Temperaturerhöhung und praktischen Fertigungsgrenzen (inkl. Kupferhaftung) ab. Allgemein gilt:

- Typische Leiterbahnen sind mindestens 0,2 mm breit, oft mit einer Kupferdicke von ≥ 18 µm.

- SMT- und High-Density-Boards können dünnere Leiterbahnen verwenden, aber feinere Geometrien erhöhen die Fertigungsschwierigkeit – wählen Sie breitere Leiterbahnen, wenn der Platz es zulässt.

(1) Signal-Leiterbahnbreiten konsistent halten; Power/GND breit ausführen

- Konsistente Signalbreiten unterstützen Impedanzkonstanz und Matching.

- Eine gängige Leitlinie für Signale ist 0,2–0,3 mm (8–12 mil).

- Für Power/GND breitere Kupferflächen nutzen, um Störeinflüsse zu reduzieren.

- Bei Hochfrequenzsignalen kann eine benachbarte Masseführung zur Abschirmung sinnvoll sein.

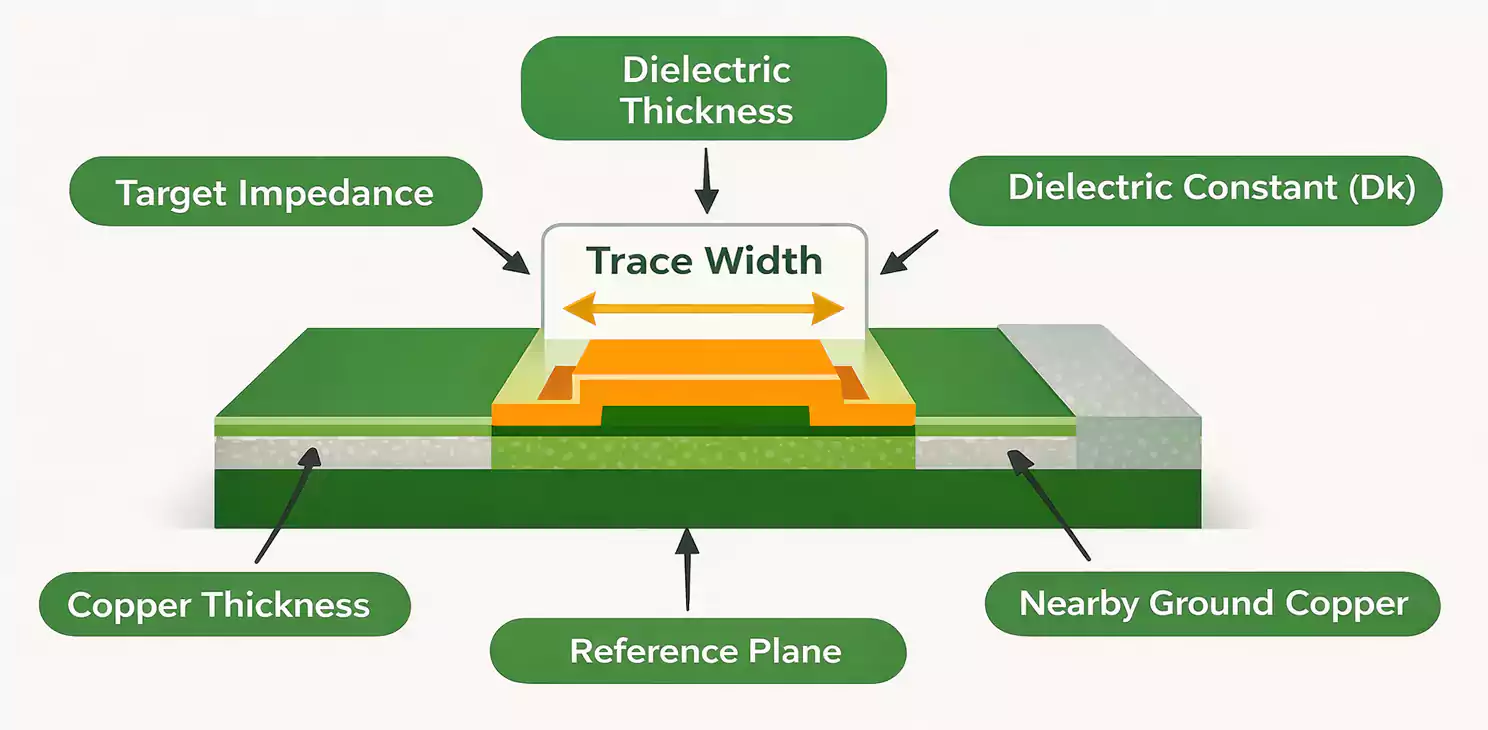

(2) High-Speed- und Mikrowellenleitungen müssen die Ziel-Impedanz erfüllen

- Breite und Dicke müssen so gewählt werden, dass die Impedanzanforderungen erfüllt werden.

(3) High-Power-Designs: Stromdichte und Isolation berücksichtigen

- Nicht nur die Breite, sondern auch Abstands-/Isolationsanforderungen berücksichtigen.

- Innenlagenleiter erlauben typischerweise nur etwa die halbe Stromdichte von Außenlagen.

(4) Abstände erhöhen, wenn möglich, um den Isolationswiderstand zu verbessern

Der Isolationswiderstand auf Außenlagen wird beeinflusst durch:

- Leiterbahnabstand

- Länge paralleler Abschnitte

- Isoliermedium (Substrat und Luft)

Wenn der Routingplatz es erlaubt, den Abstand erhöhen.

Fazit

Diese PCB-Designregeln und PCB-Designguidelines sind einfach, verhindern aber einen großen Teil realer Probleme:

- Beginnen Sie mit disziplinierter PCB-Bauteilplatzierung.

- Wenden Sie konservative PCB-Routingregeln an – für Trennung, Kopplungskontrolle und Testbarkeit.

- Nutzen Sie realistische Leiterbahnbreiten und Abstände, die Strom, Impedanz und Fertigungsfähigkeit unterstützen.