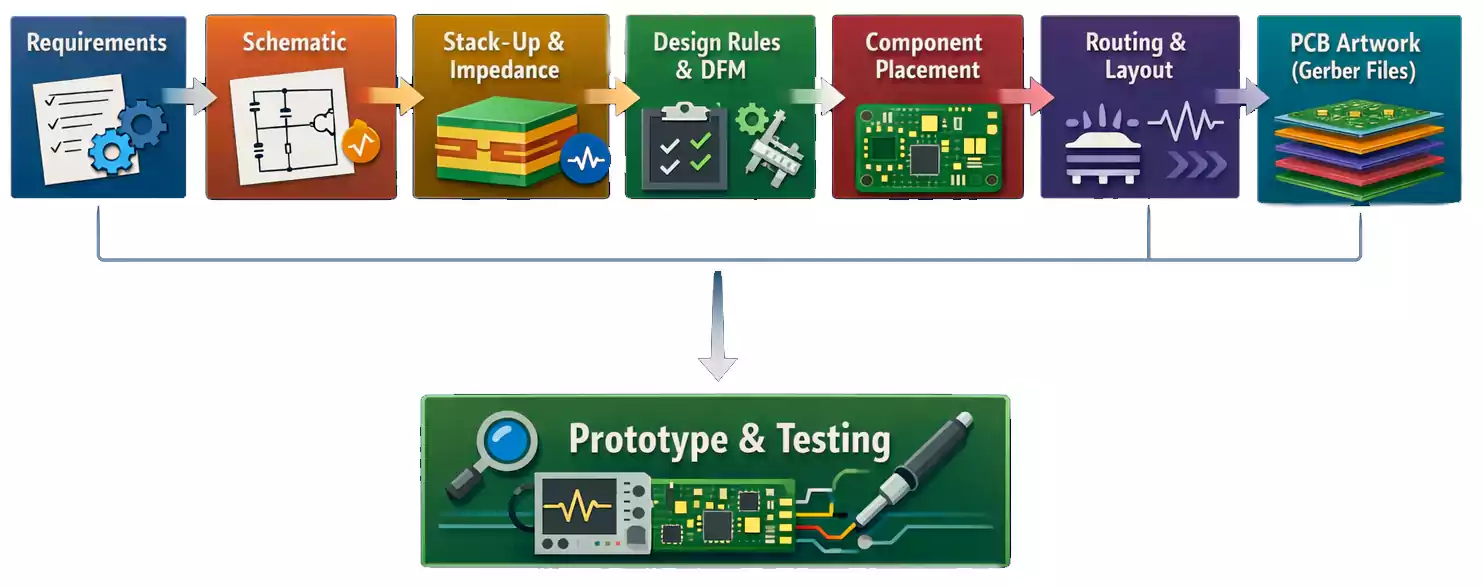

Zum ersten Mal eine gedruckte Leiterplatte (PCB) zu entwerfen, wirkt schnell komplex – eine Mischung aus Kunst, Wissenschaft und Fertigungstechnik. Wenn du jedoch den Ablauf vom Schaltplan bis zu den Fertigungsdaten (PCB Artwork / Gerber) verstehst, wird der Prozess logisch und gut beherrschbar.

Dieser Leitfaden führt dich Schritt für Schritt durch alle wichtigen Themen: Best Practices für den Schaltplan, Stack-up- und Impedanz-Planung, Regeln für Placement und Routing sowie die Vorbereitung der Fertigungsunterlagen.

Schritt 1 – Anforderungen definieren, bevor du ein CAD-Tool öffnest

Jedes erfolgreiche PCB-Design beginnt mit klaren Anforderungen. Lege elektrische und mechanische Randbedingungen fest:

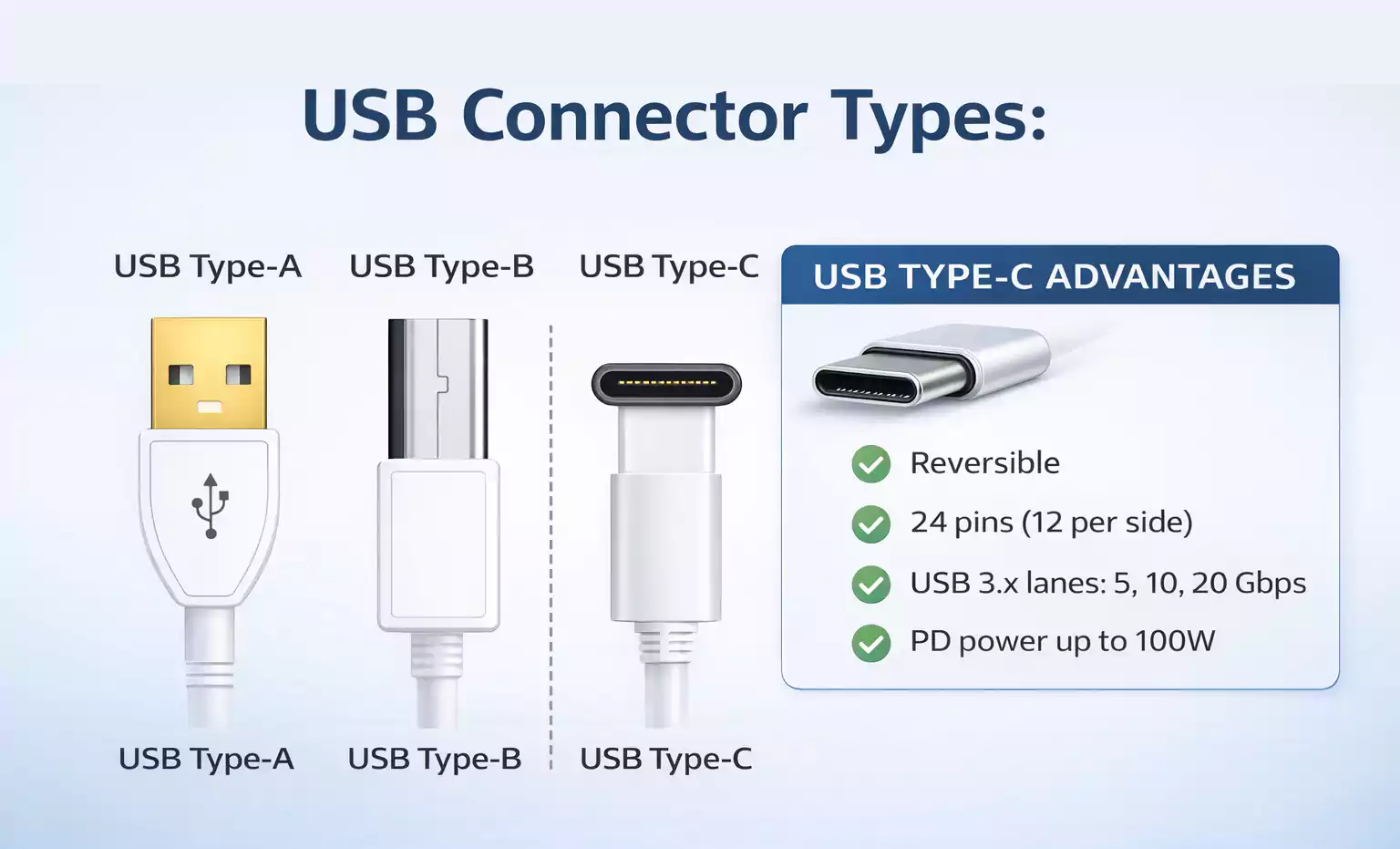

- Elektrisch: Versorgungsschienen, Stromlasten, Signalarten (analog, digital, High-Speed), Taktfrequenzen, impedanzkritische Netze, Schnittstellenstandards (z. B. USB 3.0, PCIe, LVDS).

- Mechanisch: Leiterplattenkontur, Bauhöhe, Befestigungsbohrungen, Steckverbinder, Keep-out-Zonen für das Gehäuse.

- Umgebung & Normen: Betriebstemperatur, EMI/EMV-Vorgaben, Sicherheitsklassen und Zulassungen (z. B. FCC, CE).

Erstelle ein kurzes Design-Briefing mit allen Funktionsblöcken, Schnittstellen und Leistungsbudgets. Das dient als Roadmap für Schaltplan und Layout.

Schritt 2 – Den PCB-Schaltplan zeichnen (die elektrische Blaupause)

Der Schaltplan legt fest, wie Bauteile verbunden sind. Schlechte „Schaltplan-Hygiene“ führt später zu Layout-Chaos. Beachte daher:

Saubere, konsistente Bibliotheken

Nutze geprüfte Symbol- und Footprint-Bibliotheken oder erstelle eigene. Jedes Symbol muss zum korrekten Footprint und 3D-Modell passen. Falsche Gehäusezuordnung ist ein häufiger Anfängerfehler.

Klare Benennung und Hierarchie

Vergib aussagekräftige Netznamen (USB_D+, ADC_IN1, 3V3_SYS). Größere Projekte gliederst du in hierarchische Blätter (Versorgung, MCU, Schnittstellen, Sensorik), damit Funktionen wiederverwendbar bleiben.

ERC (Electrical Rule Check) ausführen

Vor dem Export ins Layout einen ERC laufen lassen: schwebende Pins, unverbundene Versorgung, Mehrfachtreiber auf einem Netz usw. – jetzt beheben spart später Zeit.

BOM früh managen

Komponenten mit stabiler Verfügbarkeit wählen und Alternativen prüfen. Nichts bremst die Produktion so sehr wie ein abgekündigtes IC.

Schritt 3 – Stack-up planen und Impedanz berücksichtigen

Nach einem sauberen Schaltplan legst du auf der leeren Leiterplatte das Stack-up fest – also Anordnung von Kupfer- und Dielektrikschichten. Das beeinflusst Impedanz, Übersprechen und Fertigbarkeit.

- 2-lagig für einfache Analog-/Low-Speed-Schaltungen.

- 4-lagig (Signal / GND-Ebene / Power-Ebene / Signal) ist der Sweet Spot für Mixed-Signal und moderate High-Speed.

- 6-lagig oder mehr bei High-Speed-Interfaces oder dichten BGA-Bauteilen.

Für impedanzkontrollierte Netze (USB, Ethernet, RF) früh mit dem Leiterplattenhersteller sprechen: Materialdaten (Dk, Dicken, Toleranzen) ermöglichen die Berechnung von Leiterbahnbreite und -abstand für 50 Ω (single-ended) bzw. 100 Ω (differenziell).

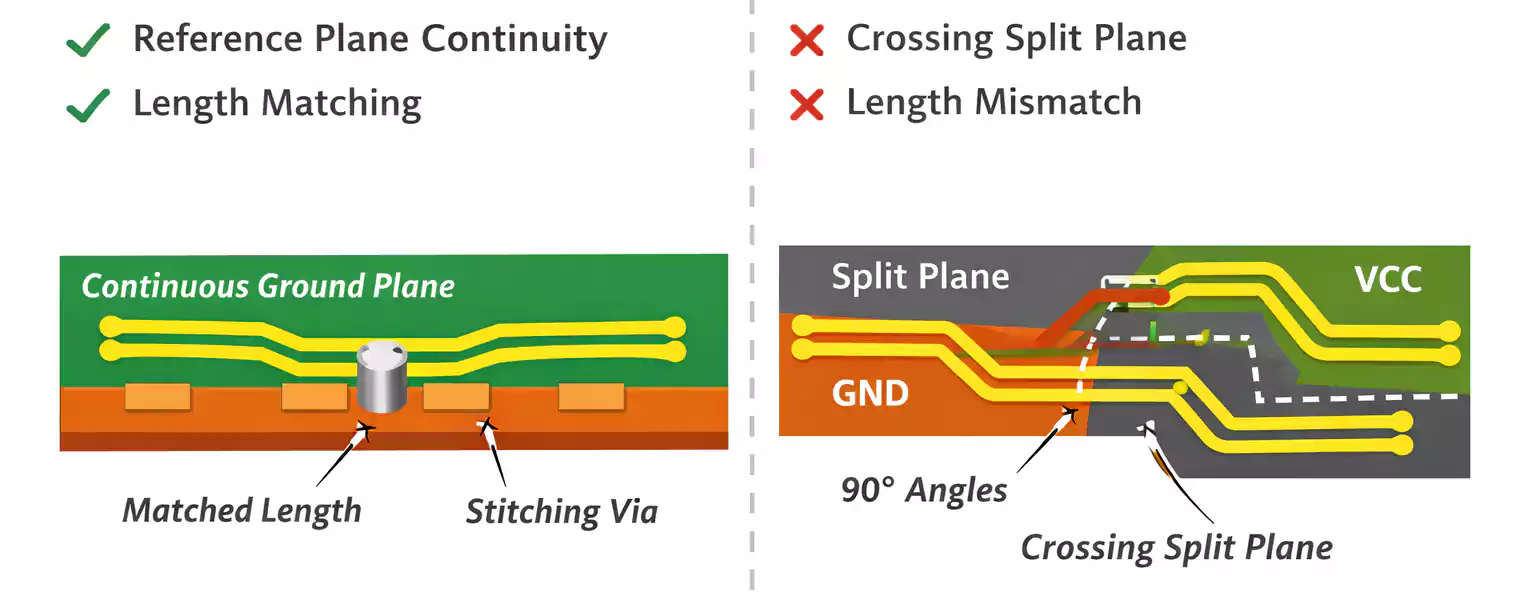

Ein gutes Stack-up stellt durchgängige Bezugsebenen unter High-Speed-Leitungen sicher und minimiert Unterbrechungen des Rückstrompfads – einer der häufigsten SI-Probleme.

Schritt 4 – Design- und DFM-Regeln früh festlegen

Bevor du platzierst, konfiguriere im CAD die Designregeln (DRC) gemäß den Fähigkeiten deines Fertigers. Typische Startwerte (variieren je nach Hersteller):

- Min. Leiterbahnbreite/-abstand: 5 mil / 5 mil

- Min. Bohrdurchmesser / Ringbreite: 0,3 mm / 0,15 mm

- Min. Lötsteg (Solder Mask Bridge): 4 mil

- Min. Silkscreen-Texthöhe: ≥ 40 mil

- Kupferdicke: 1 oz (≈ 35 µm)

DFM (Design for Manufacturability) gehört nach vorn: innerhalb realistischer Toleranzen entwerfen statt an die Grenzen zu gehen – das reduziert Kosten und erhöht die Ausbeute.

Schritt 5 – Bauteilplatzierung: nach Funktionen organisieren

Die Platzierung beeinflusst Performance, Fertigung und Service:

- Funktional gruppieren: Spannungswandler, Analog-Frontend, MCU, I/O jeweils als Inseln.

- Signalfluss beachten: Eingänge auf einer Seite, Ausgänge auf der anderen.

- Leitungswege kurz halten bei High-Speed und sensibler Analogik.

- Abblockkondensatoren so nah wie möglich an die Versorgungspins – mit kurzen Vias zur Massefläche.

- Mechanische Keep-outs für Stecker, Kühlkörper, Befestigungen reservieren.

- Testpunkte gut zugänglich vorsehen.

Denke in modularen Blöcken, das erleichtert das spätere Routing.

Schritt 6 – Vias, Ebenen und Rückstrompfade

Vias verbinden Lagen, fügen aber Induktivität hinzu und können Reflexionen begünstigen:

- Durchkontaktierte Vias (TH): am günstigsten und üblichsten.

- Blind/Buried Vias: sparen Platz in HDI-Designs, sind aber teurer.

- Kontinuierlicher Rückstrompfad: High-Speed-Leitungen nicht über geteilte Ebenen führen – der Rückstrom müsste Umwege gehen, was Rauschen/EMI erhöht.

- Beim Lagenwechsel Stitching-Vias in Masse setzen, damit der Rückstrom nahe der Leitung „abkürzen“ kann.

- Für hohe Ströme mehrere Vias parallel oder gefüllte Vias nutzen.

Schritt 7 – Routing-Strategie und Prioritäten

Damit das Routing nicht zur „Spaghetti-Leitung“ wird, gehst du nach Wichtigkeit vor:

- Differentielle High-Speed-Paare (USB, HDMI, Ethernet): Längen matchen, Kopplungsabstand konstant halten.

- Zeitkritische Signale (Clocks, Reset): kurz und separiert.

- Empfindliche Analog-Signale: Abstand zu digitalen Störquellen, ggf. Guard-Rings.

- Allgemeine Digitalsignale: lieber 45°-Bögen statt 90°-Ecken.

- Versorgung & Massenflächen: breite Kupferflächen für geringe Verluste und bessere Wärmeverteilung.

Wenn möglich, eine Lage horizontal, die nächste vertikal routen (reduziert Übersprechen). Danach DRC laufen lassen und Clearance/Konnektivität prüfen.

Schritt 8 – Thermik, EMI/EMV und Zuverlässigkeit

Auch „kleine“ Boards können heiß werden oder abstrahlen – vorbeugen ist einfacher als kurieren.

Thermisches Management

- Kupferflächen und thermische Vias leiten Wärme von Reglern, MOSFETs oder LEDs ab.

- Unter Kühlkörpern Lötstopp frei halten für guten thermischen Kontakt.

- Beim Reflow darauf achten, dass Nachbarbauteile nicht überhitzen.

EMI/EMV-Grundlagen

- Durchgehende Masseebenen und kleine Schleifenflächen.

- High-Speed-Leitungen kurz halten und von Boardkanten fern.

- Ferritperlen/CM-Drosseln nahe an I/O-Steckern.

- Bei Bedarf kleine RC-Filter einsetzen.

Zuverlässigkeit

- Via-in-Pad nur gefüllt und metallisiert verwenden.

- Teardrops an kritischen Übergängen für mechanische Robustheit.

- Je nach Branche nach IPC-A-600/610 zielen.

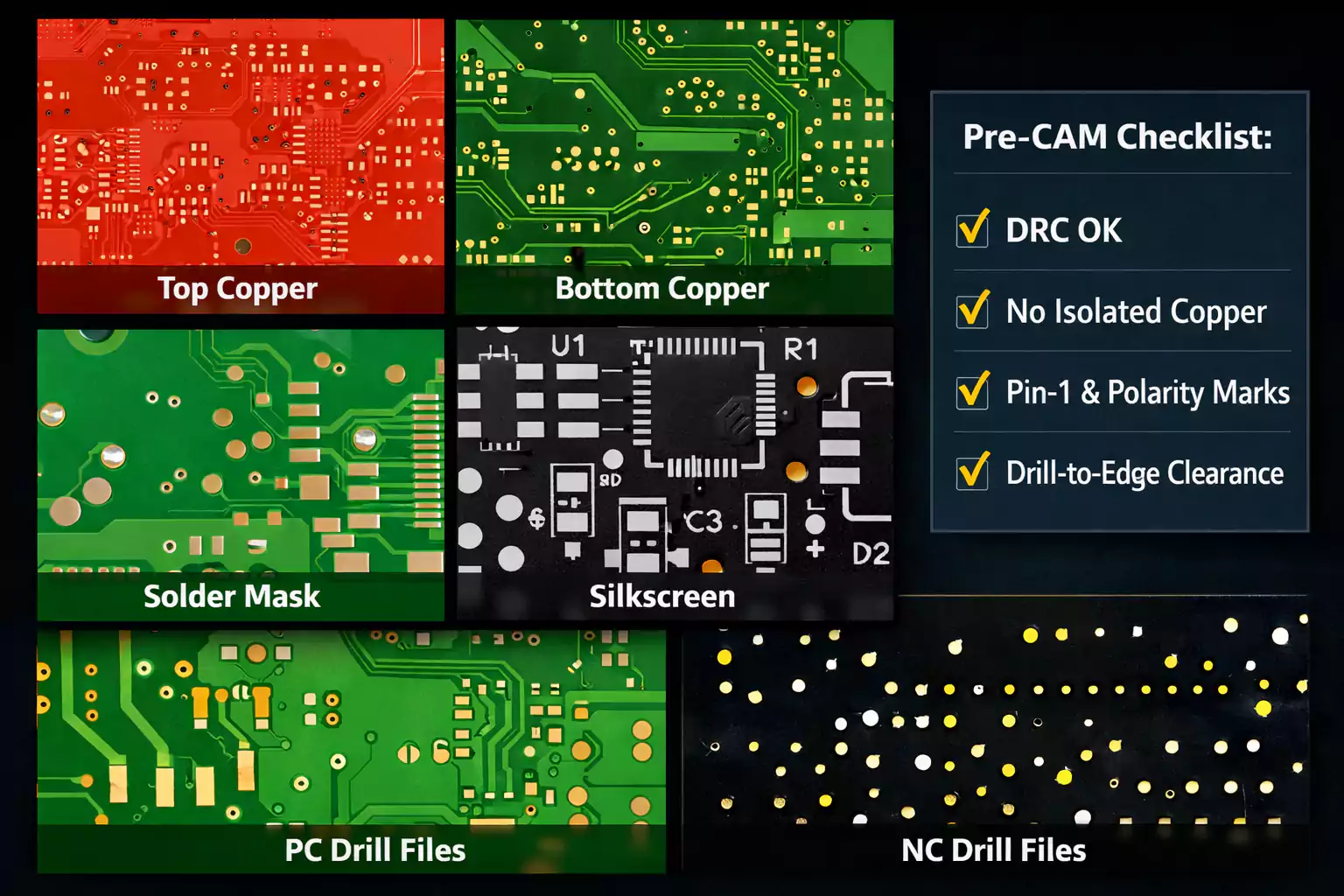

Schritt 9 – Vom Layout zum PCB Artwork (Gerber & Co.)

Unter PCB Artwork versteht man die Fertigungsdaten, die jede Lage der Leiterplatte beschreiben – Grundlage für Fotowerkzeuge oder digitale Belichtung.

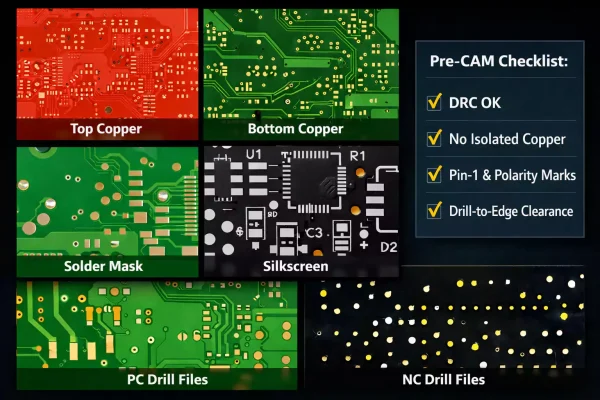

Diese Dateien gehören ins Paket

- Gerber für alle Kupfer-, Lötstopp- und Silkscreen-Lagen.

- NC-Drill für metallisierte und nichtmetallisierte Bohrungen.

- Fertigungshinweise (FAB Notes): Material, Stack-up, Kupfergewicht, Impedanzvorgaben, Oberfläche (ENIG, HASL), Lötstoppfarbe.

- Fertigungszeichnung (FAB Drawing): Kontur, Bohrtabelle, Toleranzen.

- Bestückungszeichnung (ASSY Drawing): Referenzbezeichnungen, Polungsmarkierungen.

- Pick-and-Place-Datei für die Automaten.

- BOM mit Hersteller-/Bestellnummern.

Pre-CAM-Checks vor dem Versand

- Alle DRC-Verletzungen beheben.

- Nach unverbundenen Netzen, isolierten Kupferinseln, fehlenden Referenz-/Polmarken suchen.

- Bohrung-zu-Kante-Abstand und Bauteilorientierung (Pin 1/Polung) prüfen.

- Lagen klar benennen, z. B.

TopCopper.GTL,BottomMask.GBS.

Gute Artwork-Daten stellen sicher, dass der Hersteller genau das baut, was du entworfen hast – ohne teure Überraschungen.

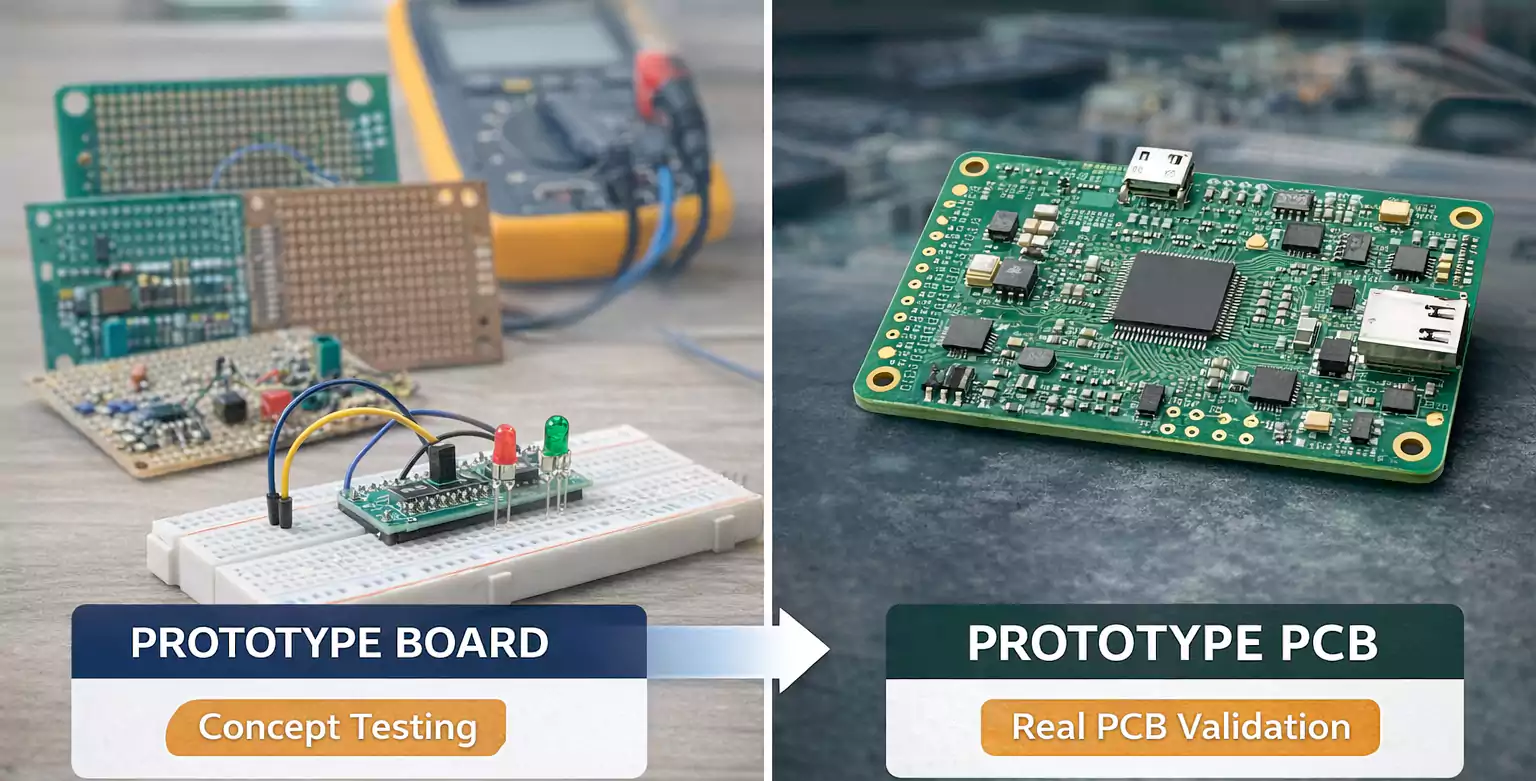

Schritt 10 – Prototyp, Test und Iteration

Baue zuerst eine kleine Prototyp-Serie und verifiziere:

- Power-Up-Test: Versorgungsspannungen und Stromaufnahme.

- Funktionstest: alle I/Os, Sensoren, Schnittstellen.

- Thermotest: Hot-Spots unter Last messen.

- Signal-Integrität: kritische Netze auf Überschwingen/Jitter prüfen.

Alles dokumentieren und gezielt in eine Revision überführen. Iteration ist Teil des Prozesses – kein Scheitern.

Wann PCB-Layout-Services sinnvoll sind

Auslagern lohnt sich, wenn:

- High-Speed, HF/RF oder HDI/Rigid-Flex im Spiel sind.

- Deadlines eng sind und die interne Kapazität fehlt.

- Du Fertigungs- und Bestückungsunterlagen nach IPC benötigst.

- SI/PI-Simulation über Bordmittel hinaus erforderlich ist.

Achte bei Dienstleistern auf Referenzen, Tool-Kompatibilität (Altium, KiCad, Cadence), vollständige Deliverables (Native-Daten + Gerber + ASSY + BOM), Vertraulichkeit sowie klare Preise und SLAs.

FAQ

1) Unterschied zwischen Schaltplan und Layout?

Der Schaltplan beschreibt die logischen Verbindungen; das Layout setzt sie physisch mit Leiterbahnen, Vias und Ebenen um. Geprüft wird mit ERC (Schaltplan) und DRC (Layout).

2) Was genau ist PCB Artwork?

Die Fertigungsdaten: Gerber-Layer, NC-Drill und Zeichnungen. Moderne Formate wie ODB++ oder IPC-2581 bündeln alles in einer Datei, Gerber bleibt jedoch am weitesten verbreitet.

3) Welches CAD eignet sich für Einsteiger?

- KiCad: Open Source, ideal für Hobby & Start-ups.

- Altium Designer: Industriestandard für professionelle, mehrlagige Designs.

- EasyEDA: Browserbasiert, gut mit Online-Fertigung verzahnt.

Wähle nach Projektkomplexität, Team-Workflow und Exportanforderungen.

Fazit

Ob einfache 2-Lagen-Arduino-Platine oder komplexes Mehrlagen-RF-System – diese zehn Schritte sind das Fundament:

- Anforderungen, 2) sauberer Schaltplan, 3) Stack-up & Impedanz, 4) Regeln & DFM,

- Placement, 6) Vias & Rückstrom, 7) strukturiertes Routing, 8) Thermik/EMI/EMV & Zuverlässigkeit,

- sauberes PCB Artwork, 10) Prototyp, Test, Iteration.

So entstehen Platinen, die nicht nur einschalten, sondern zuverlässig funktionieren, fertigbar sind und sich vom Prototyp bis in die Serie skalieren lassen. Gute PCB-Entwickler verbinden nicht nur Bauteile – sie konstruieren für Leistung, Zuverlässigkeit und Wiederholbarkeit.